Устройство для логарифмирования двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1241237

Автор: Миронов

Текст

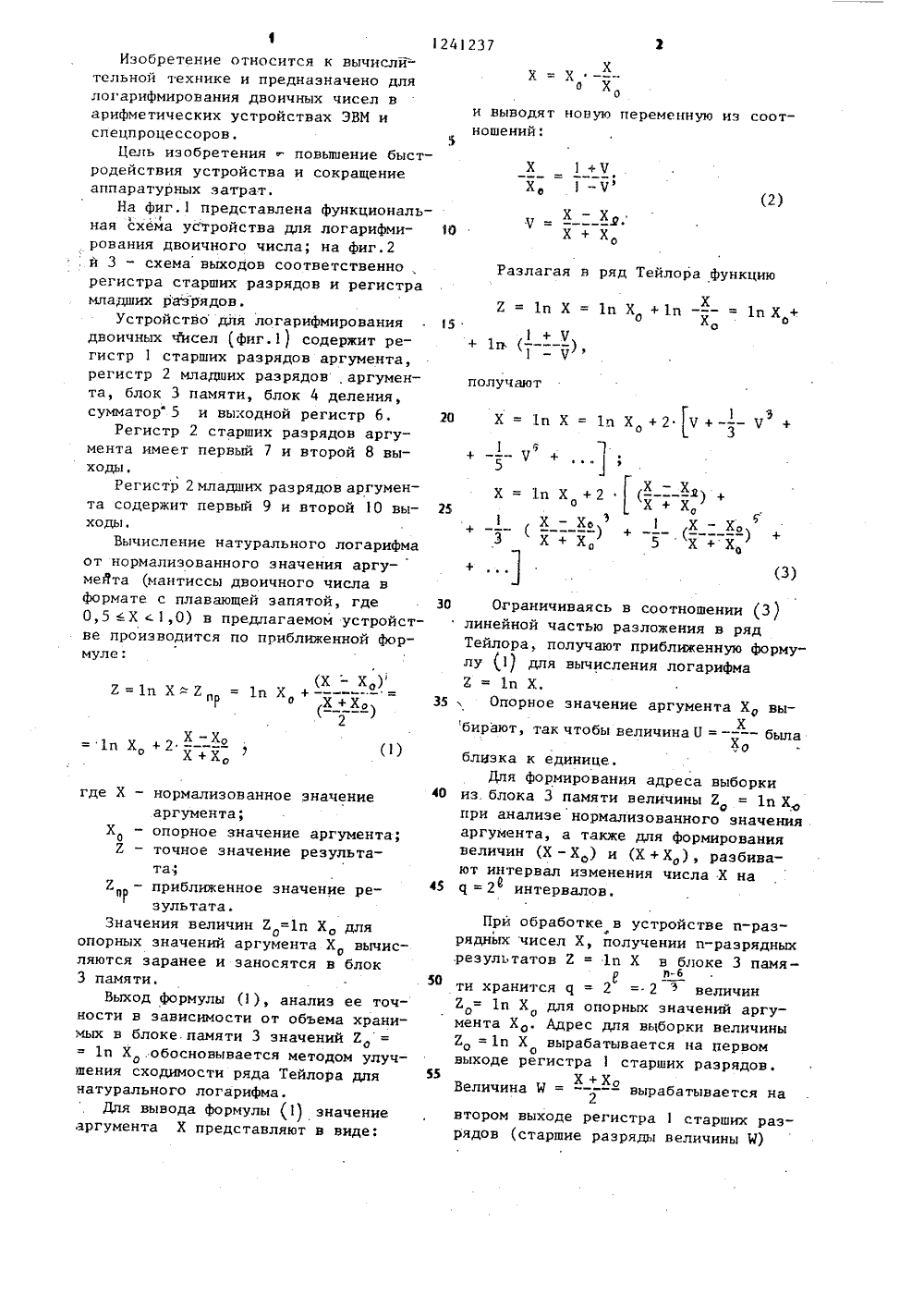

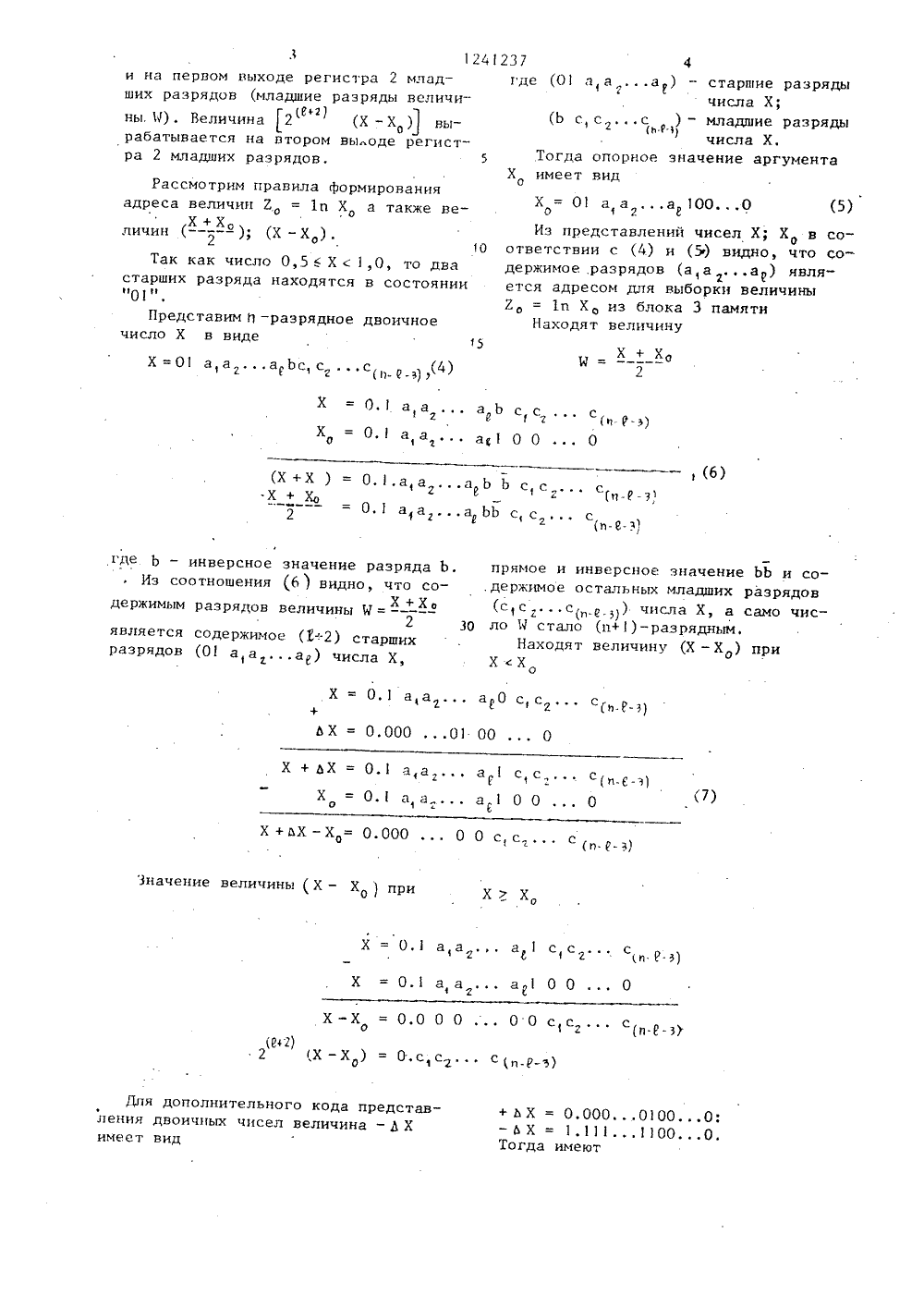

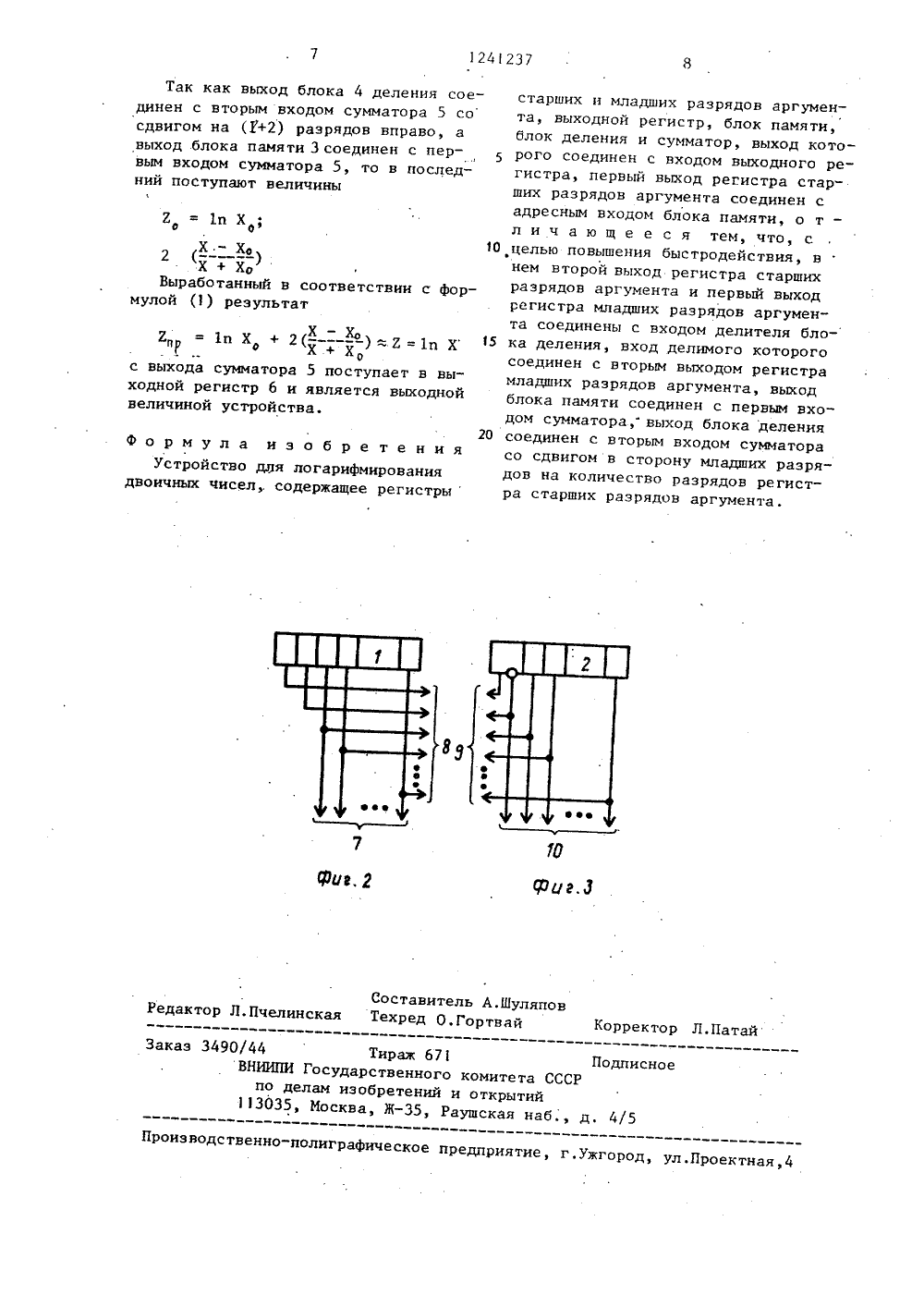

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 191 О 1 6 Р 7 55 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ЭВМ и спецпроц тения в . повыше 4-2 Вюл. У 24нов088.8) сокращение апп достигается примннй приближенно 2 = 1 п Х =2= 1 п Х +,),ованное значени регис Ю ие ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО делАм изОБРетений и ОтнРыт(56) Авторское свидетельство СССРУ 981741, кл. 6 06 Р 7/556, 1979.Авторское свидетельство СССРВ 924705, кл, С 06 Р 7/556, 1980.(54) УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ ДВОИЧНЫХ ЧИСЕЛ(57) Изобретение относится к области вычислительной техники и предназначено для логарифмирования двоичных чисел в арифметических устройствах где Х - нормализ аргумента; Х гумента; 2 - точ тата; 2 - приб результата, Устр гистры 1, 2, бло ления 4, суммато соров, Цель изобрее быстродействия и атурных затрат. Цель енением для вычисле- формулы опорное значение арное значение резульлиженное значениеойство содержит рек памяти 3, блок де 1241237Изобретение относится к вычислй тельной технике и предназначено для логарифмирования двоичных чисел в арифметических устройствах ЭВИ и спецпроцессоров.Цель изобретенияповышение быстродействия устройства и сокращение аппаратурных затрат.На фиг.1 представлена функциональная схема устройства для логарифмирования двоичного числа; на фиг,2 : и 3 - схема выходов соответственно регистра старших разрядов и регистра младших разрядов.Устройство для логарифмирования двоичных чисел (фиг.1) содержит регистр 1 старших разрядов аргумента, регистр 2 младших разрядов . аргумента, блок 3 памяти, блок 4 деления, сумматор" 5 и выходной регистр 6,Регистр 2 старших разрядов аргумента имеет первый 7 и второй 8 выходы.Регистр 2 младших разрядов аргумента содержит первый 9 и второй 1 О выходы.Вычисление натурального логарифма от нормализованного значения аргумейта (мантиссы двоичного числа в формате с плавающей запятой, где 0,5 Х с 1,0) в предлагаемом устройстве производится по приближенной формуле:=1 п Х +2Х+Хгде Х - нормализованное значениеаргумента;Х - опорное значение аргумента;Е - точное значение результата;Е - приближенное значение реОзультата.Значения величин 2 =1 п Хо для опорных значений аргумента Х вычисляются заранее и заносятся в блок 3 памяти.Вьжод формулы (1), анализ ее точности в зависимости от объема хранимых в блоке памяти 3 значений 2 =1 п Х ,обосновывается методом улучошения сходимости ряда Тейлора для натурального логарифма.Для вывода формулы (1) значение аргумента Х представляют в виде:хХ=Хо Х,и выводят новую переменную иэ соотношений: Х 1+УХ 1-Уо(2) Х - Х2.Х+ Хо Разлагая в ряд Теилора функцию Е = 1 п Х = 1 п Х + 1 п= 1 п Х +Хо Х о15о1+У.результатов 2 = 1 п Х в блоке 3 памярти хранится и = 2 = 2 э величинЕ= 1 п Х для опорных значений аргумента Хо. Адрес для выборки величиныЕ = 1 п Х вырабатывается на первомО овыходе регистра 1 старших разрядов.55 Х .ХВеличина И = в , -- вырабатывается на2втором выходе регистра 1 старших разрядов (старшие разряды величины 1 О 30 Ограничиваясь в соотношении (3)линейной частью разложения в рядТейлора, получают приближенную формулу (1 для вычисления логарифмаЕ = 1 п Х.35, Опорное значение аргумента Х выХбирают, так чтобы величина Б = -- былаХ.близка к единице.Для формирования адреса выборки 40 из, блока 3 памяти величины Е = 1 п Хпри анализе нормализованного значенияаргумента, а также для формированиявеличин (Х - Х) и (Х + Хо), разбивают интервал изменения числа Х на 45 о = 2 интервалов.(Е 2)2 (Х - Х)о О 00 0 с сс0 с сс 3 124 и на первом выходе регистра 2 младших разрядов (младшие разряды величины. Щ . Величина 2(Х - Х ) вырабатывается на втором вы оде регистра 2 младших разрядов,Рассмотрим правила формирования адреса величин 2 = 1 п Х а также веХ+Холичин (- -- ) а (Х - Х ) .ОТак как число 0,5 6 Х с 1,0, то два старших разряда находятся в состоянии 0 нПредставим 1-разрядное двоичное число Х в виде 15 Х=О а а а Ьс с с, )(4),где Ъ - инверсное значение разряда Ь,Из соотношения (,6 ) видно, что соХ+Хо держимым разрядов величины У = ---2 является содержимое (Ь.2) старших разрядов (01 а,а а) числа Х,Х+оХ = 0.1 а,а, Х = 0а а Значение величины 1,Х - Х ) прио Для дополнительного кода представления двоичных чисел величина - Д Химеет вид 1237 4где (01 а,а а ) - старшие разрядычисла Х;(Ь с с с ) - младшие разряды1 г1 В,.Р.числа Х .Тогда опорное значение ар гументаХ имеет в идоХ = 01 а а а 1000 (5)о т г иИз представлений чисел Х; Хо в соответствии с (4) и (5) видно, что содержимое .разрядов (а,а а) является адресом для выборки величины2 о = 1 п Х из блока 3 памятиНаходят величину прямое и инверсное значение ЬЬ и содержимое остальных младших разрядовчисла Х а само чис - ло Ы стало (и+1)-разрядным.Находят величину (Х - Хо) при Х ХИз выражения (7) и (8) видно, что величина ( 2( ) (Х-Х )(в дополниотельном коде формируется путем выдачи Чтаршим разрядом инюверсного значения Ь и содержи мого разрядов (с, сс(г .( -з) т.е.(2 (х - х) =ьсс с20В предлагаемом устройстве для логарифмирования двоичных чисел формирование адреса (а,аа) и величинХ + Хо е+)14= --- , Я = 2 (Х - Х ) произ 25 водится следующим образом.В регистре 1 старших разрядов хранятся (1+2) старших разряда аргумента Х; в регистре 2 младших разрядов хранятся остальные (п-2 ) младших разряда числа Х.30Первый выход регистра 1 старших разрядов, который является адресом величины Е о = 1 п Хц представляет собой прямые выходы всех, исключая два старших, разрядов регистра 1 старших разрядов.путем выдачи прямого кода из регистра 1 старших разрядов, прямого и инверсного содержимого старшего разряда и прямого кода всех остальных разрядов регистра 2 младших разрядов,(0+г)Величина Я = 2 (Х - Х ) формио руется на втором выходе регистра 2 младших разрядов путем выдачи инверсного значения старшего и прямого кода остальных разрядов регистра 2.Так как величина 50 то при вычислении величины, (Ьг) гХ - Хо6=22х+ х,достаточно в блоке 4 деления определить (и-1) его старших разрядов. Для обеспечения выдачи в сумматор5 величины необходимо выход блока 4 деления подключить к второму входу сумматора 5 со сдвигом вправо на (1+2) разрядов,Устройство для логарифмирования двоичных чисел при реализации алгоритма по формуле ) работает следующим образом.Нормализованное и-разрядное значение аргумента Х хранится в регистрах 1 и 2 старших и младших разрядов, имеющих разрядность соответствен-, но (1+2) (п-2), при этом выполняется условие 3(1+2)п, что позволяет получить точность результата 2 = 1 п Х, при которой абсолютная ошиб-, ка не превосходит половины цены младшего разряда п-разрядного результата. На первом выходе регистра 1 старших разрядов вырабатывается адрес числа Е = 1 п Хб, которое поступает на выход блока 3 памяти, Адресом является содержимое Р младших разрядов регистра 1 старших разрядов.В блок 4 деления поступают велиХ+ Х, Иг) чины У =и Ц = 2 (Х -Х ) .2 о, (е)Делимое Я = 2 (Х - Х ) поступаето в блок 4 со второго выхода регистра 2 младших. разрядов, а (и+1)-разрядХ + Хный делитель И ==формируется2на втором выходе регистра 1 старших разрядов (1+2), т,е, старших разрядов величины.1), и на первом выходе регистра. 2 младших разрядов (п-1), т,е, младших разрядов величины Ч,На выходе блока 4 деления, обрабатывающего числа в дополнительном коде находится величина24237 Составитель А.Шуляпов Техред О.Гортвай актор Л.Пчелинска Корректор Л.П каз 3490/44ВНИИПИ Г Тираж 67 Подписное ственного комитета СССРбретений и открытийпо дел3035,роизводственно-полиграфическое предприятие, г.Ужгород,ектна Так как выход блока 4 деления соединен с вторым входом сумматора 5 со сдвигом на (К+2) разрядов вправо, а выход блока памяти 3 соединен с пер - вым входом сумматора 5, то в последний поступают величиныХ - Х2 (- --- ).Х+ ХоВыработанный в соответствии с формулой ( ) результат Х - Хо2 щ 1 п Х + 2(- -- -)=Е=1 п ХдР ф Х+Х,с выхода сумматора 5 поступает в выходной регистр 6 и является выходной величиной устройства. Формула и з о б р е т е н и я Устройство для логарифмирования двоичных чисел,. содержащее регистрыстарших и младших разрядов аргумента, выходной регистр, блок памяти,блок деления и сумматор, выход которого соединен с входом выходного регистра, первый выход регистра старших разрядов аргумента соединен садресным входом блока памяти, о т -личающееся тем,что, с 10 целью повышения быстродействия, внем второй выход регистра старшихразрядов аргумента и первый выходрегистра младших разрядов аргумента соединены с входом делителя бло ка деления, вход делимого которогосоединен с вторым выходом регистрамладших разрядов аргумента, выходблока памяти соединен с первым входом сумматора, выход блока деления 20 соединен с вторым входом сумматорасо сдвигом в сторону младших разрядов на количество разрядов регистра старших разрядов аргумента.

СмотретьЗаявка

3756539, 19.06.1984

ВОЙСКОВАЯ ЧАСТЬ 13132

МИРОНОВ ИВАН ЯКОВЛЕВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: двоичных, логарифмирования, чисел

Опубликовано: 30.06.1986

Код ссылки

<a href="https://patents.su/5-1241237-ustrojjstvo-dlya-logarifmirovaniya-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для логарифмирования двоичных чисел</a>

Предыдущий патент: Вычислительное устройство

Следующий патент: Генератор случайного напряжения

Случайный патент: Установка для фиксированной подачи животных при искусственном осеменении