Микропроцессорный модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

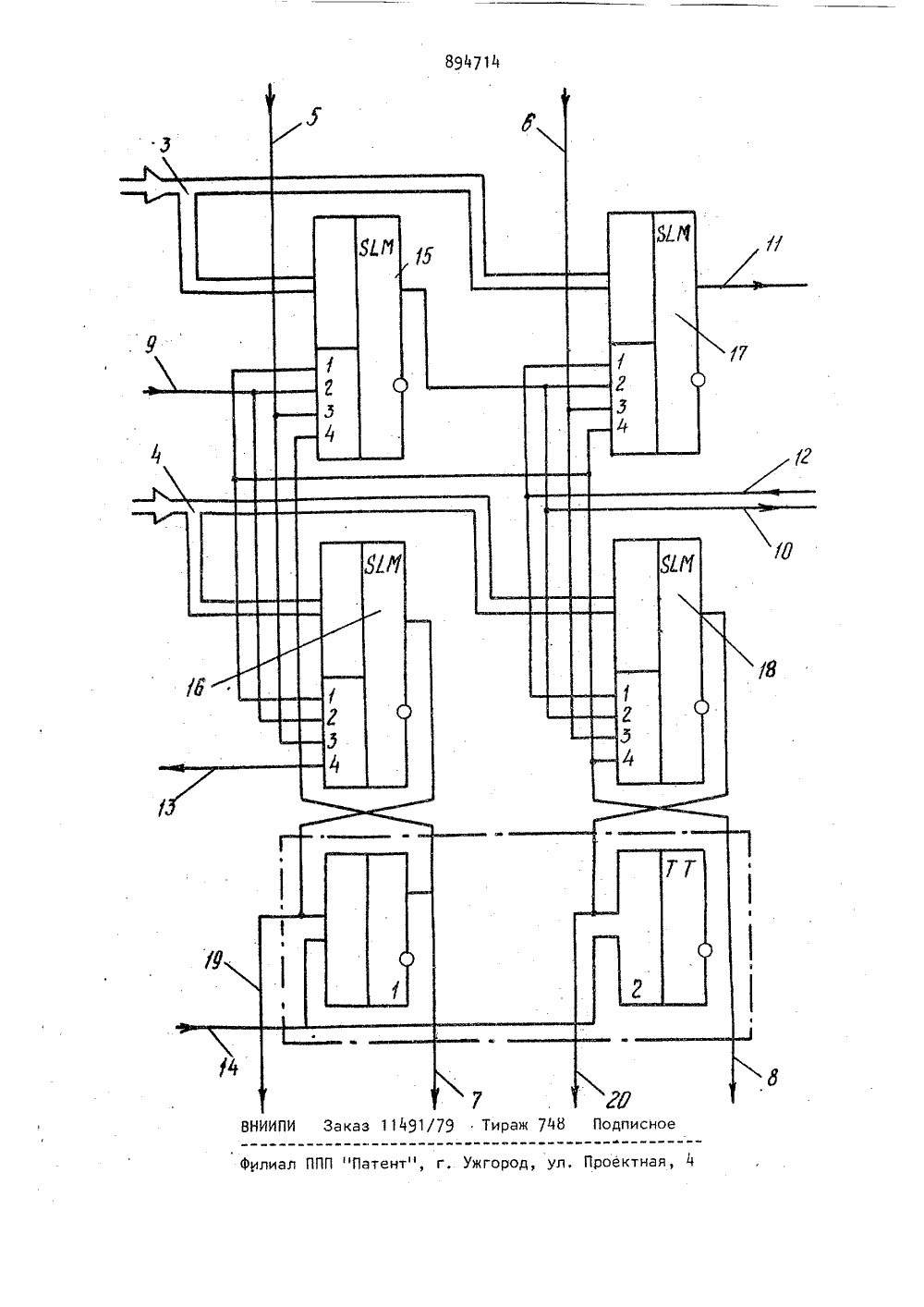

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциалистическихРеспублик(51) М. Кл. 6 06 Г 15/00 Гасударственный комитет ло делам изобретений м открытий(72) Авторы изобретения бинский авиационный технологический. инстит 1) Заявител 4) МИКРОПРОЦЕССОРНЫЙ МОДУЛЬ сится к вычислиожет быть применеднородных универИзобретение отнотегьной технике ино при построении осальных ЭВМ.Известны микропли, содержащие триуправления 1 1,е мо оцессоргеры и пы шин цессор- ункциоН стного микропроограниченные можности, обусловждый разряд резульсываются ограни- еключательных достаток изв рного модуляиональные во е тем, что к и перенос оп сс функ ленн тата нным набором п Недостаток таких микропроных модулей - ограниченные фнальные возможности.Наиболее близким к предлагаемому является микропроцессорный модуль, содержащий регистр, группы шин управления, входные и выходные шины данных, шины переноса, шины обратн й связи и шину тактовых импульсов 21 функций трех аргументов: разрядовоперандов и переноса из прудыдущегоразряда, Микропроцессорный модульпозволяет реализовать всего лишьшесть основных операций, выполняемыхза один такт синхронизации: арифметическое сложение в дополнительных кодах, поразрядные логическиесложения, умножение и инверсия суммыпо модулю два, сдвиг вправо и влевона один разряд,Цель изобретения - расширениефункциональных возможностей микропроцессорного модуля за счет увели"чения числа арифметико-логическихопераций,Поставленная цель достигаетсятем, что в микропроцессорный модуль,содержащий триггеры нулевого и первого разрядов, входы синхронизациикоторых соединены с шиной тактовыхимпульсов, введены четыре мультиплексора, причем первая группа шинуправления соединена с информацион 894714.ными входами первого мультиплексора, первый управляющий вход которого. соединен с первым управляющим входомвторого мультиплексора, второй управляющий вход которого соединен с 5входной шиной переноса и со вторымуправляющим входом первого мультиплексора, третий управляющий входкоторого соединен с первой входнойшиной данных и с третьим управляющимвходом второго мультиплексора,четвертый управляющий вход которогосоединен с выходной шиной обратнойсвязи, первой выходной шиной данных,выходом триггера нулевого разрядаи с четвертым управляющим входомпервого мультиплексора, выход которого соединен с первой выходной шиной переноса, вторая выходная шинапереноса соединена с выходом третьего мультиплексора, первый управляющий вход которого соединен со входной шиной обратной связи и с первымуправляющим входом четвертого мультиплексора, второй управляющий входкоторого соединен с первой выходнойшиной переноса и со вторым управляющим входом третьего мультиплексора,третий управляющий вход которогосоединен со второй входной шиной дан" ЗОных и с третьим управляющим входомчетвертого мультиплексора, четвертыйуправляющий вход которого соединенс выходом триггера первого разряда,со ВТОРОЙ ВыхОднОЙ шинОЙ данных с 35первым управляющим входом первогомультиплексора и с четвертым управляющим входом третьего мультиплексора, информационные входы которогосоединены с первой группой шин управления, информационные входы второго и четвертого мультиплексоров соединены со второй группой шин управления, выходы второго и четвертогомультиплексоров соединены с 0-входами триггеров нулевого и первого.разрядов соответственно, первая ивторая асинхронные шины данных соединены соответственно с 0-входами триггеров нулевого и первого разрядов.На чертеже представлен микропрацеосорный модуль, функциональнаясхема,Микропроцессорный модуль содержиттриггеры 1 и 2 нулевого и первогоразрядов, первую и вторую группы шин 3и 4 управления, первую и вторую входныешины 5 и б данных, первую и вторуювыходные шины 7 и 8 данных,входную шину 9 переноса, первую иВторую выходные шины 10 и 11 переноса, входную и выходную шины 12 и13 обратной связи и шину 14 тактовых импульсов, первый, второй, третий и четвертый мультиплексоры 1518, первую и вторую выходные асинхронные шины 19 и 20 данных.Микропроцессорный модуль работает следующим образом.Двоичный код, подаваемый па шинам групп шин 3 и 4 управления,задает вид реализуемой модулем операции над двумя операндами, один изкоторых записан в триггеры 1 и 2, авторой установлен на входных шинах5 и.б данных. На выходах мультиплексоров 16 и 18 формируются соответственно нулевой и первый разрядыкода результата операции. При этом,1-ый разряд результата (нулевой илипервый) есть переключательная функция четырех аргументов: сигнала на1-той выходной шине данных (первой7 или второй 8); сигнала на 1-той"входной шине данных (первой 5 иливторой б), сигнала переноса, поступающего по входной шине 9 переносаили непосредственна с выхода мультиплексора 15 и сигнала обратной связи,поступающего непосредственно с первойвыходной шины 8 данных или по входной шине 12 обратной связи, Вид этойфункции определяется двоичным кодом,подаваемым по шинам группы шин 4управления,Одновременно на выходах мультиплексоров 15 и 17 Формируются сигналы переноса соответственно из нулевого и первого разрядов модуля, которые поступают на выходные шины 10 и 11 переноса. Сигналы переноса являются переключательными функциями тех же самых четырех аргументов, чта и сигналы результата операции. Вид этих функций определяется двоичным кодом, подаваемым по шинам групп шин 3 управления.По фронту тактового импульса, поступающего по шине 14 на входы синхронизации триггеров 1 и 2, происходит запись кода результата опера ции с асинхронных выходных шин 19 и 20 данных в разряды триггеров 1 и 2. Этот код подается на выходные шины 7 и 8 данных. Одновременно сигнал с выхода триггера 1 нулевого40 разряда поступает на выходную шину1 обратной связи, Код, записанныйв триггерах 1 и 2, остается неизменным до прихода фронта следующеготактового импульса,5Использование изобретения позволяет расширить функциональные возможности устройства за счет обеспечения реализации 2-=4.294 967.296(количество возможных кодовых ком 10бинаций на шинах первой и второйгрупп шин управления) различныхарифметико-логических операций сдвумя операндами, каждая из которыхвыполняется за один такт синхрониза 1ции.Это обусловлено тем, что каждыйразряд результата и переноса описываются полным набором .всех возможныхпереключательных функций четырехаргументов: разрядов операндов, переноса из предыдущего разряда и сигнала обра 1;ной связи из последующегоразряда,Предлагаемый микропроцессорныймодуль позволяет реализовать всешестнадцать поразрядных логическихопераций, из которых лищь три выполняются в известном устройстве, атакже совмещенные операции, напримерЗ 0арифметическое сложение в дополнительных кодах с одновременным инвертированием или другим преобразованиемкода результата, и т,п.Реализация за один такт совмещен-.ных арифметико-логических операцийпозволяет повысить быстродействиепредлагаемого модуля по сравнениюс известным.Формула изобретенияМикропроцессорный модуль, содержащий триггеры нулевого и первогоразрядов, входы синхронизации которых соединены с шиной тактовых импульсов, о т л и ч а ю щ и й с я 4тем, что, с целью расширения Функциональных возможностей за счет увеличения числа арифметико-логическихопераций, в него введены четыре мультиплексора, причем первая группа шин 50управления соединена с информационными входами первого мультиплексора,первый управляющий вход которого соединен с первым управляющим входом второго мультиплексора, второй управляющий вход которого соединен свходной шиной переноса и со вторымуправляющим входом первого мультиплексора, третий управляющий входкоторого соединен с первой входнойшиной данных и с третьим управляющимвходом второго мультиплексора, четвертый управляющий вход которого соединен с выходной шиной обратной связи, первой выходной шиной данных,выходом триггера нулевого разряда ис четвертым управляющим входом первого мультиплексора, выход которогосоединен с первой выходной. шиной переноса, вторая выходная шина переноса соединена с выходом третьегомультиплексора, первый управляющийвход которого соединен со входнойшиной обратной связи и с первымуправляющим входом четвертого мультиплексора, второй .управляющий входкоторого соединен с первой выходнойшиной переноса и со вторым управляющим входом третьего мультиплексора,третий управляющий вход которогосоединен со второй входной шинойданных и с третьим управляющим входом четвертого мультиплексора, четвертый управляющий вход которогосоединен с выходом триггера первогоразряда, со второй выходной шинойданных, с первым управляющим входомпервого мультиплексора и с четвертым управляющим входом третьего куль.типлексора, информационные входы,которого соединены с первой группойшин управления, информационные входы второго и четвертого мультиплексоров соединены со второй группойшин управления, выходы второго ичетвертого мультиплексоров соединеныс. О-входами триггеров нулевого ипервого разрядов соответственно,первая и вторая асинхронные шиныданных соединены соответственно сО-входами триггеров нулевого и первого разрядов.Источники информации,принятые во внимание при экспертизе1. Патент Японии й 52-13706,кл. 98 (5) О 1, 19772. Зарубежная электронная техника. 1977, 8 9, с, 19-21 (прототип).

СмотретьЗаявка

2786482, 22.06.1979

РЫБИНСКИЙ АВИАЦИОННЫЙ ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ

ГЛАДШТЕЙН МИХАИЛ АРКАДЬЕВИЧ, БАСКАКОВ ВЯЧЕСЛАВ АЛЕКСЕЕВИЧ, КОМАРОВ ВАЛЕРИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессорный, модуль

Опубликовано: 30.12.1981

Код ссылки

<a href="https://patents.su/4-894714-mikroprocessornyjj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессорный модуль</a>

Предыдущий патент: Устройство для контроля хода программ

Следующий патент: Микропроцессор

Случайный патент: Устройство для поштучной выдачи цилиндрических деталей