Устройство для умножения п-разрядных двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

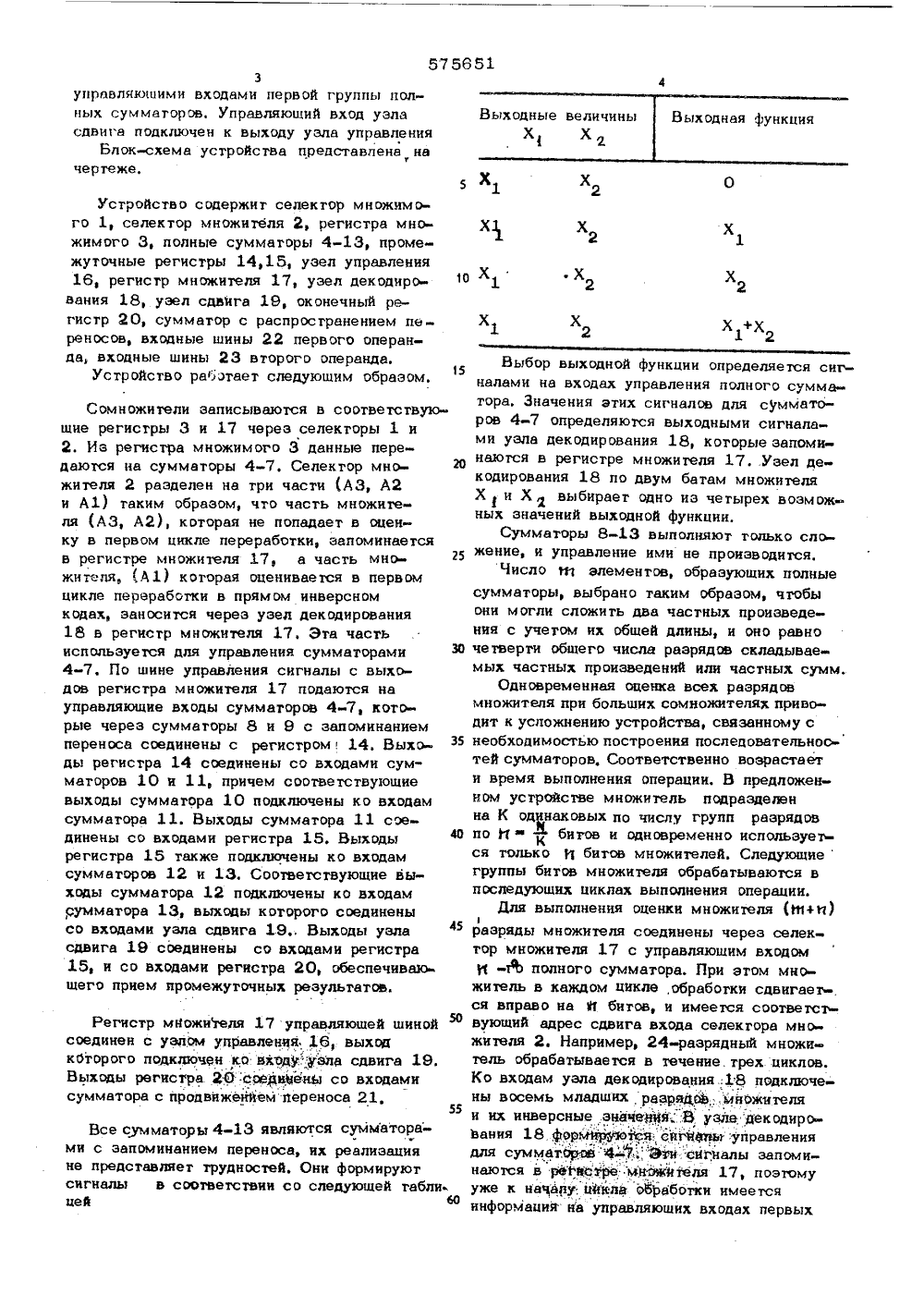

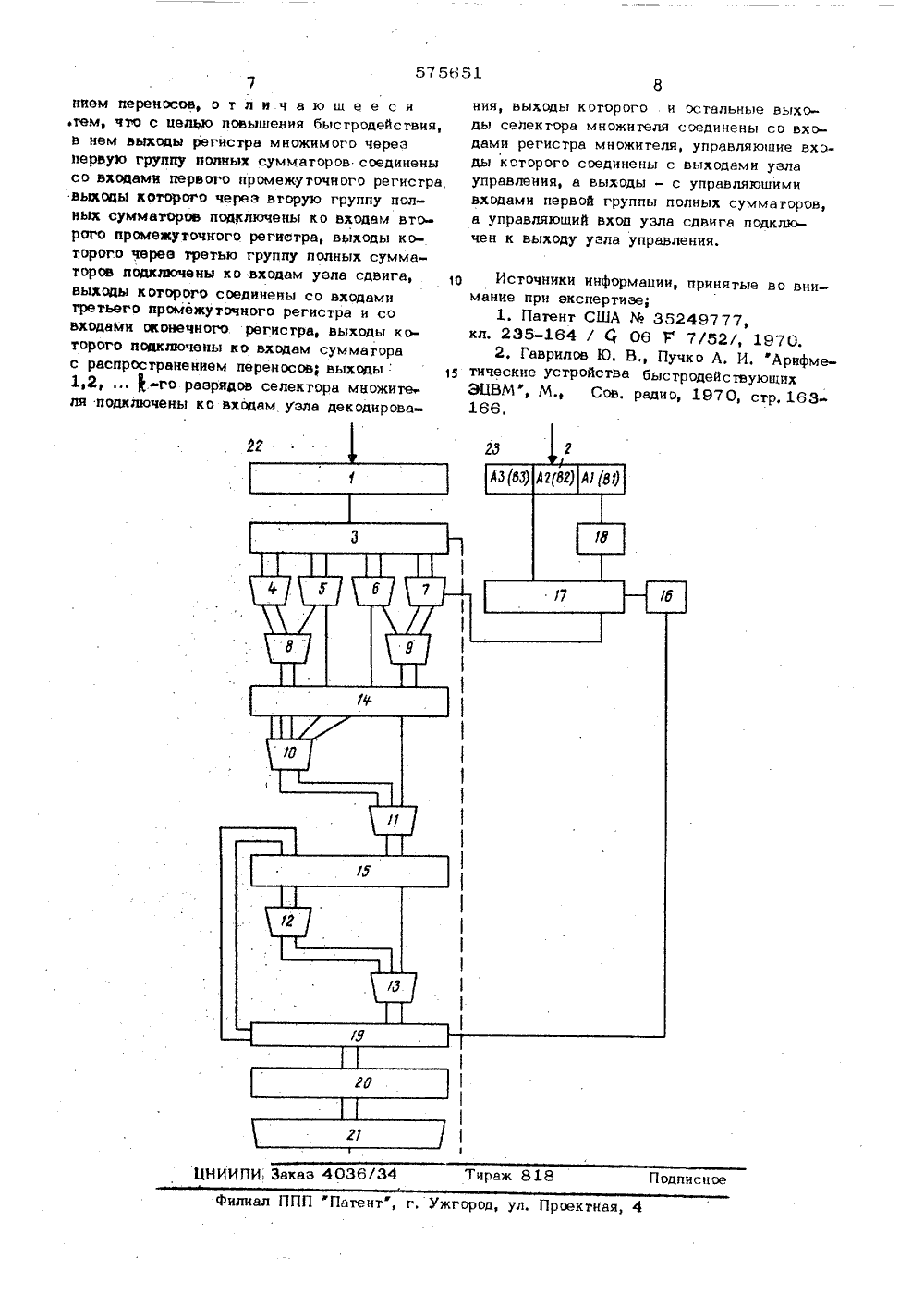

Союз Советскии Социалистицеских Республикнсоединением зая осударствеииыи комитетСовета Ииииотроо СССРоо делам изобретеиийи открытий 23) Приоритет31) Ф Р 6 061/1706143) Опубликовано 05,112) Авторы изобретения юнтер Кра ланд Га раннее предприятие Комбинат Роботрон" Ино "Фе) УСТРОЙСТВО ДЛЯДВОИЧНЫХ М НОЖЕИСЕД И -РАЗРЯДНЫ Х 61) Дополнительное к а Изобретение относится к области ввтома тики и вычислительной техники и может быть использовано при реализации технических средств ЫВМ и устройств дискретной автоматики.Известны устройства для умножения И -разрядных двоичных чисел, содержащие селекторы данных, регистры, полные сумматоры с распространением переносов, узлы управления и сдвига 1 1. Недостаткоь известного устройства является низкое быстр оде йс твие. Наиболее близким техническим решение к изобретению является устройство для умножения И -разрядных двоичных чисел, содержащее селектор множимого, входы которого соединены с входными шинами первого операнда, а выходы - с входами регистра множимого, селектор множителя, входы которого подключены к входным шинам второго операнда, регистр множителя, сумматоры с распространением переносов, узел сдвига, узел декодирования, узел управления, оконечный н промежуточный вйнц Бейс н Готтфрид Валь регистры и суммпереносов 121,Белью изобретения является повышениебыстродействия устройства.Эта цель достигается тем, что в предлагаемом устройстве выходы регистра множимого через первую группу полных сумматорОв соединены со вкодамн первого промежуточного регистра, выходы которого через вторую группу полных сумматоров псаключеныко входам второго промежуточного регистра. Выходы этого регистра через третьюгруппу полных сумматоров подключены ковходам узла сдвиге., выходы которого соединены со входами третьего промежуточного,регистра я со входами оконечного регистра,Выходы последнего подключены ко входамсумматоров с распространением переносов,Выходы 1,2, Кго разрядов селекторамножителяподключены ко входам узда декодирования, выхсаы. которого н остальныевыходы селектора множителя соединены совходами регистра множителя. Управляющие .вхсаы регистра множителя соединены свыходами узда управленияа выходы - с втор с распространением3 улравляюшимн входами лервой ных сумматоров. Управляющий сдвига подключен к выходу уБлок-схема устройства лре чертеже. группы лолвход узла зла управления дставлена наТ Устройство содержит седектор множимого 1, селектор множитедя 2, регистра множимого 3, полные сумматоры 4-13, промежуточные регистры 14,15, узел управления 16, регистр множителя 17, узел декодирования 18, узел сдвига 19, оконечный регистр 20, сумматор с распространением лвреносов, входные шины 22 первого операнда, входные шины 23 второго операнда.Устройство ра:отает следующим образом. 30 40 управдяюшей щи ой ния 16, выхоа ОдУ.".:узда сдвига 19. вацеки со входами переноса 21, н стр множигеля 17 н с уэдом удравле о подключен ко ек регистра 20:ссед ора с продвижением сумматоры 4-13 явл апоминанием перенос ставляет трудносге в соответствииРеги соедине которог Выходы сумм атяются сумматора-т а, их реализация . Они формируют со следующей табл Все мисэ не пре сигн аль цей Сомножители записываются в соответсгвуюшие регистры 3 и 17 через селекторы 1 и 2. Из регистра множимого 3 данные передаются на сумматоры 4-7. Селектор множителя 2 разделен на три части (АЗ, А 2 и А 1) таким образом, что часть множителя (АЗ, А 2), которая не попадает в оценку в первом цикле переработки, запоминается в регистре множителя 17, а часть множителя, (А 1) которая оценивается в первом цикле переработки в прямом инверсном кодах, заносится через узел декодирования 18 в регистр множителя 17, Эта часть используется для управления сумматорами 4-7, По шине управления сигналы с выходов регистра множителя 17 подаются на управляющие входы сумматоров 4-7, которые через сумматоры 8 и 9 с запоминанием переноса соединены с регистром 14, Выходы регистра 14 соединены со входами сумматоров 10 и 11, причем соответствующие выходы сумматора 10 подключены ко входам сумматора 11. Выходы сумматора 11 соединены со входами регистра 15. Выходы регистра 15 также подключены ко входам сумматоров 12 и 13. Соответствующие выходы сумматора 12 подключены ко входам сумматора 13, выходы которого соединены со входами узла сдвига 19 Выходы узда сдвига 19 соединены со входами регистра 15, и со входами регистра 20, обеспечиваюшего прием промежуточных результатов.Х Х Х Х Х Выбор выходной функции определяется сигналами на входах управления полного сумматора, Значения атих сигналов для сумматоров 4-7 определяются выходными сигналами узла декодирования 18 которые запоминаются в регистре множителя 17. Узел декодирования 18 по двум батам множителяХи Хвыбирает одно иэ четырех возможных значений выходной функции,Сумматоры 8-13 выполняют только сложение, и управление ими не производится,Число и элементов, образующих полныесумматоры, выбрано таким образом, чтобыони могли сложить два частных произведения с учетом их общей длины, и оно равночетверти общего числа разрядов складываемых частных произведений или частных сумм.Одновременная оценка всех разрядовмножителя при больших сомножителях приводит к усложнению устройства, связанному снеобходимостью построения последовательностей сумматоров, Соответственно возрастаети время выполнения операции. В предложенном устройстве множитель подрана К одинаковых по числу групппо Ибитов и одновременноКся только И битов множителей.группы битов множителя обрабатпоследующих циклах выполнения оДля выполнения оценки множи зделенразрядовиспользуетСледующиеываются вле рации.геля (Ини) разряды множителя соединены через селектор множителя 17 с управляющим входоми -А полного сумматора. При атом множитель в каждом цикле,обработки сдвигаепся вправо на й битов, и имеется соответствующий адрес сдвига входа селектора множителя 2. Например, 24-разрядный множитель обрабатывается в течение. трех циклов.Ко входам узла декодирования:18 подключены восемь младших раэрщов,;,множителяи их инверсные эначейня.:8. уэдв.аекодироЬания 18.формщюФся сегида:управлениядля сумматоровФ,; ЭФи сигналы запоминаются в рЖФстре ьййжнтеля 17, поэтомууже к началу: цйкдю обработки имеетсяинформация иа управляюших входах первых5четырех сумматоров 4-7. При атом время распространения сигналов через узел декодирования 18 сокращается за счет использования прямых и инверсных значений сигналов селекторов множителя. Регистр множимого 3 с длиной 24 разряда так соеди-. нен с информационными входами сумматоров 4-7, что на входах каждого из них множи-, мое подведено дважды, причем оба они сдвинуты одно относительно другого на один разряд, поэтому частные произведения в процессе умножения могут складываться.Процесс умножения разделен во времени на четыре такта, Каждому иэ этих тактов соответствуют передачи информации на соответствующие промежуточные и оконечные регистры.Промежуточный регистр 15, подключенный к последовательности сумматоров 4-11 запоминает на время цикла частные суммы, 2 О В сумматорах 12,13 в третьем такте выполнения операции они складываются, таким образом, после трех циклов обработки весь множитель оказывается обработанным. Окончательное произведение множимого и множи- д теля формируется после восьми циклов, причем в шестом цикле производится запись по сигналу управления в оконечный регистр 20.Для атой цели множитель разбивается на зО три равных по длине группы битов А 1, А 2, А 3 или В 1, В 2 ВЗ или С 1С 2 СЗ, В сумматорах 4-7 частные произведения суммируются до частных сумм и частных переносов и через полные сумматоры 8,9 35 заносятся в регистр 14, Некоторые частные переносы сразупопадают в регистр 14, не проходя через полные сумматоры. Одновременно множитель в регистре множителя 17 с помощью узлауправления 16 сдвигает 40 ся на восемь разрядов вправо с помощью селектора мнощтеля 2, так что в узле. цекодирования 18. декодйруются разряды с 8 до 15, которые затем заносятся на регистр множителя 17, ФсВ следующем цикле промежуточный результат попадает из регистра 14 на регистр 15. Как и в предыдушем цикле к сумматораМ 4-7 подключено множимое. Декодированный множитель переносится с регистра множителя 17 и определяет в сумматорах 4-7, какие частные произведения будут сложены. Одновременно множитель иэ регистра множители 17 с помощью селектора множителя 2 сдвигается еще на восемь разрядов вправо, так что в узле декодирования 18 дека дируются последние разряды от 16 до 23. В третьем цикле первый промежуточный результат с регистра 15 проходит через сумматоры 12, 13, Посредством управляющего импульс иэ узла управления 16, который передается на узел сдвига 19, первый промежуточный результат сдвигается на восемь разрядов и в конце цикла вместе со вторым промежуточным результатом поступает на регистр 15. Третий промежуточный результат от третьего и последнего участком множителя запоминается в регистре 14.Теперь новая пара сомножителей может быть записана в регистр множителя 17 и регистр множимого 3. В четвертом цикле оба первых промежуточных результата (частные суммы и частные переносы) объединяются через сумматоры 12,13. Посредством сигналауправления с узла управления 16, который подается на узел сдвига 19, объединенные промежуточные результаты сдвигаются еше на восемь разрядов вираво. Эти промежуточные результаты в конце цикла вместе с третьим и последним промежуточным результатом попадают на регистр 15.В следующем цикле объединенные промежуточные результаты добавляются в сумматорах 12, 13 к третьему и последнему промежуточным результатам, так что получается общая сумма и общие переносы всех частных произведений. Посредством импупьса управления с узлауправления 16 на узел сдвига 19 передается команда записи в регистр 20. Общая суммд и общий перенос запоминаются.В циклах с шестого по восьмой в сумматоре продвижения переноса 21 складываются общая сумма и общие переносы в .окончательное произведение.После восьми циклов переработки получают произведение. В то же время, когда формируются конечная сумма ч конечные переносы, от третьей нары сомножителей объединяются первая и вторая частные суммы,Технико-экономический эффект изобретения заключается в повышении быстродействвия устройства в 3,5 - 4 разапрп достаточно простой и однородной структуре. Ф о р м у. л а и э о б р е т е н и я Устройство для умножения л -разрядных двоичных чисел, содержащее селектор множимого, входы которого соединены со входными шинами первого операнда, а выходысо входами регистра множимого селектор множителя, входы которого подключены ко входным шинам второго операнда, регистр множителя, сумматоры с распространением переносов, узел сдвига, узел декОдирования, узел управления, оконечный и проме жуточный; регистры сумматор с распростране575651 10 15 7нием переносов, о г л и ч а ю ш е е с я тем, что с целью новьиоения быстродействия, в нем выходы регистра множимого через первую группу полных сумматоров соединены со входами первого промежуточного регистра, выходы которого через вторую группу полных сумматоров подключены ко входам второго промежуточного регистра, выходы которого через третью группу полных сумматоров подключены ко входам узла сдвига, выходы которого соединены со входами третьего промежуточного регистра и со входами оконечного регистра, выходы которого подключены ко входам сумматора с распространением переносов; выходы1,2,. го разрядов селектора множите ля подключены ко входам узла декодирования, выходы которого и остальные выходы сепекгора множителя соединены со входами регистра множителя, управляющие входы которого соединены с выходамн узлауправления, а выходы - с управляюшимивходами первой группы полных сумматоров,а управляющий вход узла сдвига подключен к выходу узла управления. Источники информации, принятые во внимание при акспертизе;1. Патент США Х 35249777,кл. 235-164 /06 Г 7/52/, 1970.2. Гаврилов Ю. В., Пучко А. И. Арифметические устройства быстродействующих ЭЦВМ, М Сов. р дио, 1970, сгр. 163- 166.

СмотретьЗаявка

2021983, 30.04.1974

ФЕБ КОМБИНАТ РОБОТРОН

ГЮНТЕР КРАУЗЕ, РОЛАНД ГАЙСЛЕР, КАРЛ ХАЙНЦ ВАЙС, ГОТТФРИД ВАЛЬТЕР

МПК / Метки

МПК: G06F 7/52

Метки: двоичных, п-разрядных, умножения, чисел

Опубликовано: 05.10.1977

Код ссылки

<a href="https://patents.su/4-575651-ustrojjstvo-dlya-umnozheniya-p-razryadnykh-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения п-разрядных двоичных чисел</a>

Предыдущий патент: Частотно-импульсное алгебраическое суммирующее устройство

Следующий патент: Частотно-импульсное множительное устройство

Случайный патент: Устройство для утилизации тепловой энергии