Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1585835

Автор: Урбанович

Текст

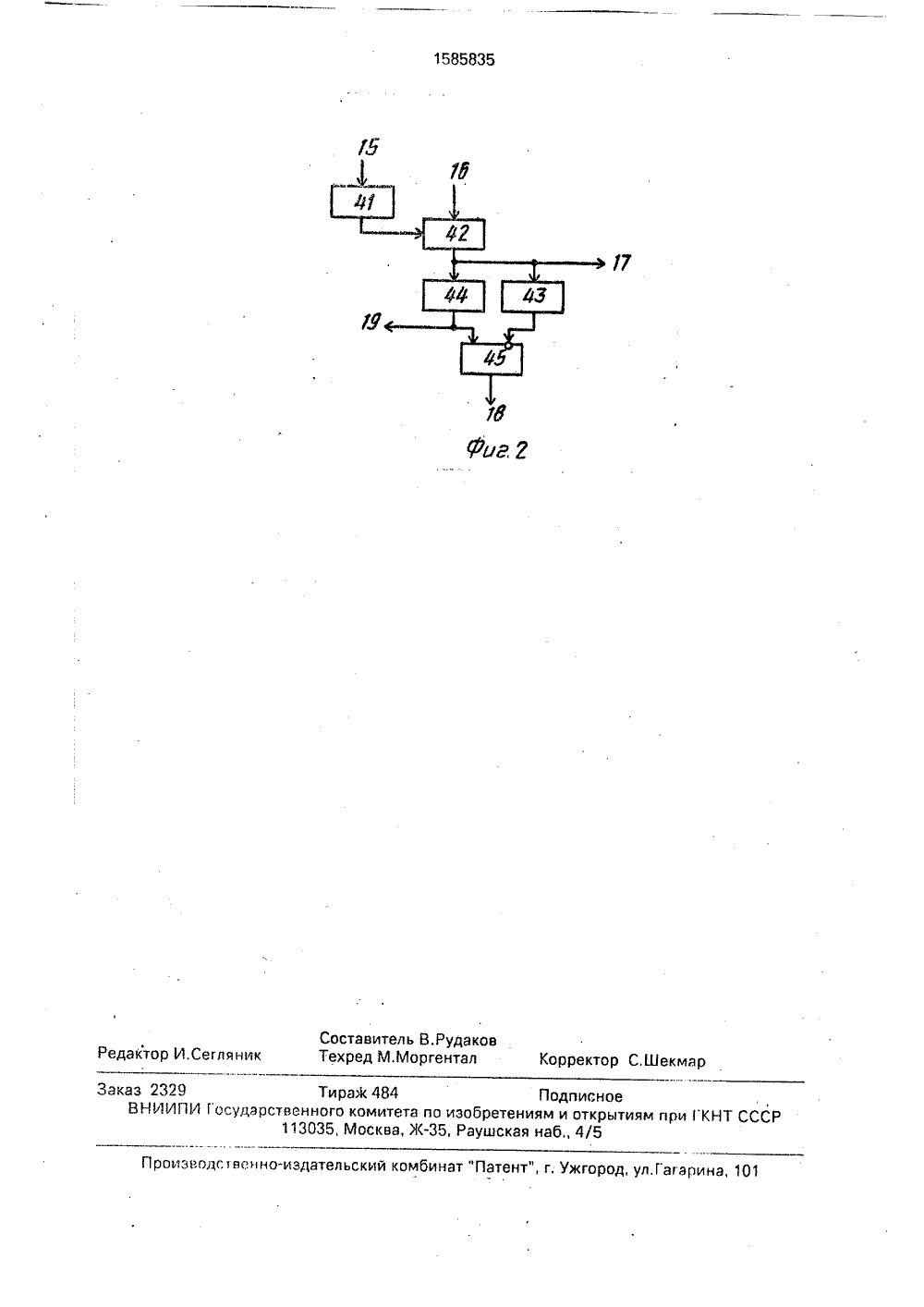

(51) 5 ИСАНИЕ ИЗОБРЕТЕНИЯ 0 ИДЕТЕЛЬСТВ ческии инсти ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(54) ЗАПОМИНАЮЩЕИСПРАВЛЕНИЕМ ОШИ57) Изобретение относной технике и может быт ьство СССР/00, 1981.ьство СССР9/00, 1983.Е УСТРОЙСТВО СБОКится к вычислительь использовано при создании устройств памяти повышенной функциональной надежности. Цель изобретения - повышение быстродействия, Устройство содержит блок 1 памяти, коммутаторы 3 и 6, регистр 5 числа, блок 9 инверторов, блок 12 кодирования, блок 14 обнаружения ошибок, дешифратор 21, блок23 коррекции, регистр 24 сдвига, элементы И 29 - 31, элементы ИЛИ 32,33, В устройстве обеспечивается исправление многократных ошибок в любом кодовом слове, количество которых более, чем в два раза превышает корректирующую способность применяемого кода. 2 ил.формационные выходы 35, адресный вход 36, вход 37 записи-чтения, вход 38 обращения, тактовый вход 39, выход 40 "Окончание цикла".Пример реализации блока 14 обнаружения ошибок при использовании модифицированного кода Хемминга для коррекции одной ошибки в кодовом слове показан на фиг.2. Блок 14 содержит сумматоры 41 - 43 по модулю два, элемент ИЛИ 44 и элемент.И 45,На выходах 17 блока 14 формируется синдром ошибки, все разряды которого равны нулю лишь при отсутствии ошибок в считанном из блока 1 памяти кодовом слове. Единичные сигналы на выходах 19 и 18 этого блока вырабатываются в случаях наличияошибки любой кратности и появления 45 50 55 Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежных запоминающих устройств (ЗУ) и систем,5Цель изобретения - повышение быстродействия.На фиг.1 приведена структурная схема предложенного устройства; на фиг.2 - блок обнаружения ошибок (пример реализации). 10Запоминающее устройство с исправлением ошибок фиг.1) содержит блок 1 памяти, информационные входы 2 которого соединены с выходами первого коммутатора 3, выходы 4 блока 1, соединенные с ин формационными входами регистра 5 числа, информационными входами первой группы второго коммутатора 6, информационные входы второй 7 и третьей 8 групп подключены к соответствующим выходам регистра 5, 20 соответствующие выходы которого связаны также с входами блока 9 инвертирования, выходами подключенного к информационным входам 10 третьей группы коммутатора 3, информационные входы первой группы 25 которого подключены к информационным входам 11 устройства, соединенным также с входами блока кодирования 12, выходы 13 блока 12 кодирования, соединенные с информационными входами коммутатора 3, 30 Устройство содержит также блок 14 обнаружения ошибок с входами 15 и 16 и выходами 17 - 19, управляющий вход 20 коммутатора 3, дешифратор 21, с выходами 22, соединенными с входами блока 23 коррекции. Уст ройство содержит также регистр 24 сдвига с первым 25, вторым 26, третьим 27 и четвертым 28 выходами, элементы И 29 - 31 с первого по третий, второй 32 й первый 33 элементы ИЛИ. Выход 34 элемента ИЛИ 33 40 соединен с входом обращения блока 1 памяти, Кроме того, устройство содержит иношибки кратности два (в общем случае любой),Принцип работы предлагаемого запоминающего устройства основан на определении кратности ошибки в считанном из блока памяти кодовом(прямом) слове. Если число ошибок не превышает корректирующую способность кода, то ошибка исправляется и инверсное кодовое слово в ту же ячейку блока памяти не записывается, Запись инверсного слова осуществляется лишь в случае обнаружения ошибки, кратность которой превышает корректирующую способность кода. Таким образом, в любом кодовом слове можно исправить более, чем в 2 раза большее число ошибок, чем корректирующая способность кода,Запоминающее устройство работает следующим образом,Режим записи.На входе 37 - логическая единица. На входах 36 - адрес опрашиваемой ячейки блока 1, на входе 38 - также сигнал логической единицы. Подлежащие записи вблок 1 памяти информационные символы поступают на входы 11 устройства, в соответствии с чем блок 12 кодирования вырабатывает проверочные символы корректирующего кода, которые совместно с информационными символами записываются в блок памяти, На этом режим записи окончен.Режим считывания.Опрашиваемая ячейка блока 1 выбирается как и в режиме записи. На входе 37 - ;0", При поступлении первого тактового импульса на входе 39 " - 1" устанавливается в первом выходном разряде 25 регистра сдвига 24, которая с каждым новым тактовым импульсом передвигается к последующему соответствующему разряду регистра, Между первым и вторым тактовыми импульсами происходит считывание кодового слова из блока памяти, запись его в регистр 5 по заднему фронту сигнала на выходе 25 регистра 24, Кроме того, кодовое слово через коммутатор 6 попадает в блок 14 обнаружения ошибок, Если в считанном блоке ошибок нет, о чем свидетельствуют нулевые сигналы на выходах 18 и 19 блока 14, то по приходу второго тактового импульса на выходе 40 элемента ИЛИ 32 вырабатывается сигнал окончания цикла и обнуления регистров 5 и 24, При этом на выходах 17 блока 14 - нулевые сигналы, Информационные символы проходят на выходы 35 устройства через блок 23 коррекции, состоящий из сумматоров по модулю два (на фиг,1 не показаны) без изменений, Если в считанном слове обнаружена одна ошибка (корректируемая), на выходах 19 - "1", 18 - "0", то она коррек 158583510 15 20 25 30 35 40 45 50 тируется единичным сигналом на соответствующем выходе дешифратора 21. По приходу второго такта режим заканчивается. ф Если же в считанном слове обнаруженц две ошибки (некорректируемая ошибка),то по приходу второго тактового импульса единичный сигнал вырабатывается на выходе 34 элемента ИЛИ 33, разрешающий запись в блок 1 памяти инверсного кодового слова с выходов блока 9, которое проходит на входы блока 1 через коммутатор 3, на управляющем входе которого "0". По приходу третьего тактового сигнала производится сЧитывание инверсного кодового слова из блока памяти и его контроль с цельюобнаружения и исправления ошибок. Ошибки исправляются описанным способом, По приходу четвертого тактового импульса цикл заканчивается и регистры 5 и 24 обнуляются. В соответствии с сигналом на выходе 40 элемента ИЛИ 32, связанным с центральным устройством управления (не показано). происходит съем информации, установленной на выходах 35 устройства. Таким образом, предложенное устройство способно исправить Ь = 2(+ 1 ошибок, гдето- корректирующая способность применяемого кода.Формула изобретения Запоминающее устройство с исправлением ошибок, содержащее блок кодирования, блок обнаружения ошибок, блок коррекции, первый и второй коммутаторы, регистр числа, дешифратор и блок памяти, информационные входы которого соединены с выходами первого коммутатора, информационные входы первойгруппы которого соединены поразрядно с входами блока кодирования и являются информационными входами устройства, выходы блока кодирования соединены с информационными входами второй группы первого коммутатора, выходы блока памяти подключены к информационным входам регистра числа и к информационным входам первой группы второго коммутатора, выходы регистра числа подключены к информационным входам второй группы второго коммутатора, выходы первой и второй групп которого подключены к соответствующим входам блока обнаружения ошибок, первый выход кото-, рого соединен с входом дешифратора, вы-ходы которого соединены с входами первой группы блока коррекции, входы второй группы которого соединены с выходами первой группы второго коммутатора, выходы блока коррекции являются информационными выходами устройства, управляющий вход первого коммутатора является входом записи-чтения устройства, . адресные входы блока памяти являются одноименными входами устройства, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены регистр сдвига, блок инвертирования, первый, второй и третий элементы И, первый и второй элементы ИЛИ, причем информационный и тактовый входы регистра сдвига являются соответственно входом обращения и тактовым входом устройства, входы установки в "0" регистра сдвига и регистра числа подключены к выходу второго элемента ИЛИ, первый выход регистра сдвига соединен с входом разрешения приема регистра числа, второй выход регистра сдвига соединен с первыми входами элементов И с первого по третий, вторые входы первого и второго элементов И соединены с вторым выходом блока обнаружения ошибок, третий выход которого соединен с третьим входом первого элемента И, второйвход третьего элемента И и первый вход первого элемента ИЛИ соединены с входом записи-чтения устройства, второй вход первого элемента ИЛИ подключен к выходу первого элемента И, третий выход регистра сдвига подключен к управляющему входу второго коммутатора, выходы второго и третьего элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ, третий вход которого соединен с четвертым выходом регистра сдвига, выход первого элемента ИЛИ подключен к входу записи-чтения блока памятй, входы и выходы блока инвертирования соединены соответственно с выходами регистра числа и информационными входами третьей группы первого коммутатора, выход второго элемента ИЛИ является выходом "Окончание цикла" устройства.1585835Составитель В.Рудаков едактор И.Сегляник Техред М.Моргентал Корректор С,Шекмар каз 2329 Тираж 484 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС113035, Москва, Ж, Раушская наб 4/5изводевоино-издательский комбинат "Патент", г, Ужгород, ул.Гагар

СмотретьЗаявка

4196251, 17.02.1987

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

УРБАНОВИЧ ПАВЕЛ ПАВЛОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 15.08.1990

Код ссылки

<a href="https://patents.su/4-1585835-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Элемент памяти

Следующий патент: Индукционный выключатель

Случайный патент: Способ изготовления адаптерной плиты