Устройство для формирования адресов процессора быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

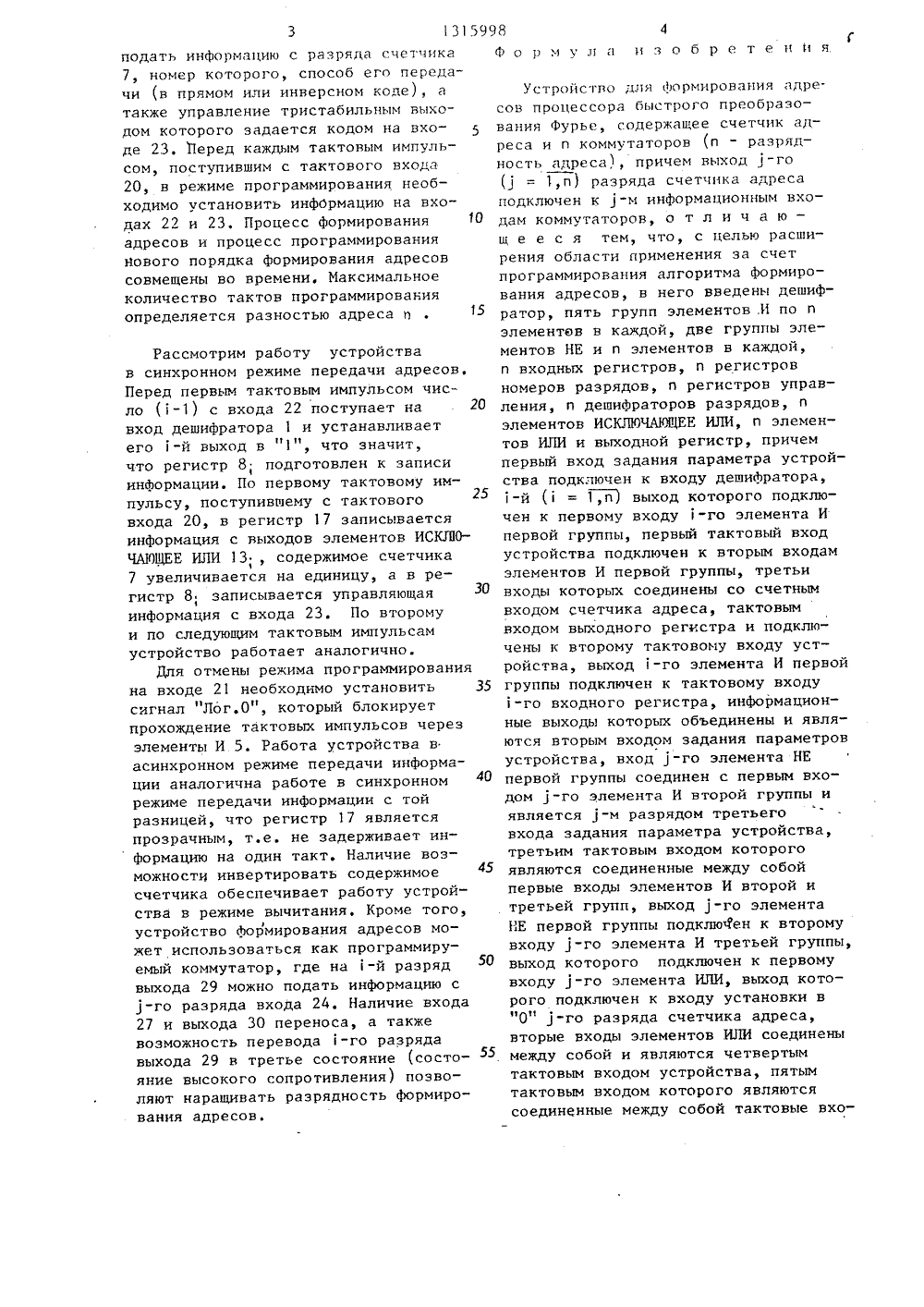

ОЮЗ СОВЕТСКИХ ОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) 06 5 о 1. Цмо СССР1975.СР льств5/332ство15/33 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ПРОЦЕССОРА БЫСТРОГО ПРЕОБРА ЗОВАНИЯ ФУРЬЕ(57) Изобретение относится к вычислительной технике и может быть использовано в цифровых процессорах обработки сигналов. Цель изобретения - расширение области применения за счет программирования алгоритма9 1920 21 22 Л формирОвания адресов - достигаетсяза счет того, что устройство дляформирования адресов процессора бьтрого преобразования Фурье содержитдешифратор 1, элементы НЕ 2, .,2,элементы И 33 ц, 4,,45,5, элементы ИЛИ 6, - 6,счетчик 7 адресов, регистры 88, 9. . .9, 10 .10, дешифраторы 11,11, коммутаторы 12,Изобретение относится к вычислительной технике и может быть использовано в цифровых процессорах обработки сигналов,Цель изобретения - расширениеобласти применения за счет программирования алгоритма формированияадресов.На чертеже представлена функцио.нальная схема устройства для формирования адресов,Устройство содержит дешифратор1 элементы НЕ 2, 2 2 д (гдеи - разрядность счетчика адресов),элементы И 3, 3 ,3 4 4,, 4и 555, элементыресов, регистры 8 8, 8 п 99 ,.,9 п и 10 ь 1 0ф 1 0,ю дешифраторы 11 11 .11, коммутаторы 1212 ,12 , элементыИСКЛЮЧА 1 ОЩЕЕ ИЛИ 13 , 1313элементы НЕ 14, 14 , , 14 элементы И 15, 15 15 о, 16 и1616, регистр 17, тактовыевходы 18 - 21, входы 22 - 24 заданияпараметров, тактовые входы 25 и 26,вход 27 переноса сигнала, тактовыйвход 28, информационный выход 29.,выход 30 переноса. Устройство работает следующим образом.Порядок Формирования адресов в устройстве задается информацией, записанной в регистрах 9, 9 9 и 10, 10 1 О. Код числа, записанного в регистре 9; (где1,2, ;,и), задает порядковый номер разряда счетчика 7, информация с которого поступает на выход коммутатора 12. При коде числа в регистре 9 равном (1-1) (где= 1,2, ,п), на 1-м выходе дешифратора 11 устанавливается ециничный сигнал, который разрешает прохождение информации с 1-го разряда счетчика 7 на выход коммутатора 12,. В зависимости от содержимого первого разряда регистра 10, информация с коммутатора 12 проходящая через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13 инвертируется (содержимое первого разряда регистра 10 - Лог. 1) или нет (содержимое1 Рпервого разряда регистра 10, Лог.О), Содержимое второго разряда регистра 1 О; управляет тристабильным выходом 1-го разряда регистра 17: разрешает вывод информации 20 25 30 35 40 45 50 55(содержимое второго разряда регистра 10; - "Лог,О") или переводит выход этого разряда в состояние высокого сопротивления (содержимое второго разряда регистра 10, - "Лог.1")Перед началом каждого нового по" рядка формирования адресов в устройстве необходимо установить режим передачи информации, режим программирования, произвести начальную установку счетчика 7, записать управ-. ляющую информацию в регистры 9 9 9 и 10 ь 10 юь 10 или произвести их установку. Начальная установка счетчика 7 заключается в параллельной записи в него по положительному импульсу с тактового входа 25 информации с входа 24 или в сбросе в "0" по положительному импульсу с входа 26. Запись управляющей информации в регистры 9, 9 9и 10 1010 из регистров 8 8 8производится по переднему Фронту положительного импульса с тактового входа 19.Установка информации в регистрах производится положительным импульсом с входа 18При установке регистрысбрасываются в "0", а в 1-м регистре 9, устанавливается число (-1)Сигналом на тактовом входе 28 устанавливается режим передачи информации - асинхронный (на входе 28 "Лог.1") или синхронный (на входе 28 "Лог,О"), В асинхронном режиме передачи информация с выходов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13; проходит через элемент И 15, поступает на вход установки в "1" -го разряда регистра 17, а также проходит через элемент НЕ 14 иэлемент И 16;, затем поступает на вход установки в "0" -го разряда регистра 17. Таким образом, в асинхронном режиме регистр 17 работает по установочным входам, т.е. является прозрачным, В синхронном режиме информация с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13, записывается в регистр 17 по тактовому импульсу на его синхровходе. Сигнал "Лог,1" на входе 21 устанавливает устройство в режим программирования нового порядка формирования адресов.На входе 22 задается номер разряда выхода, на который необходимо1315998 4г а Формула изобретения подать информацию с разряда счетчик7, номер которого, способ его передачи (в прямом или инверсном коде), атакже управление тристабильным выходом которого задается кодом на входе 23. Перед каждым тактовым импульсом, поступившим с тактового входа20, в режиме программирования необходимо установить инфОрмацию на входах 22 и 23. Процесс формирования 10адресов и процесс программированиянового порядка формирования адресовсовмещены во времени. Максимальноеколичество тактов программированияопределяется разностью адреса и . 15 Рассмотрим работу устройства в синхронном режиме передачи адресов. Перед первым тактовым импульсом число (1-1) с входа 22 поступает на . 20 вход дешифратора 1 и устанавливает его 1-й выход в 1, что значит, что регистр 8, подготовлен к записи информации. По первому тактовому импульсу, поступившему с тактового входа 20, в регистр 17 записывается информация с выходов элементов ИСКЛЮЧАИЩЕЕ ИЛИ 13 , содержимое счетчика 7 увеличивается на единицу, а в регистр 8, записывается управляющая информация с входа 23, По второму и по следующим тактовым импульсам устройство работает аналогично.Для отмены режима программирования на входе 21 необходимо установить 35 сигнал Лог.О, который блокирует прохождение тактовых импульсов через элементы И 5. Работа устройства в асинхронном режиме передачи информации аналогична работе в синхронном 40 режиме передачи информации с той разницей, что регистр 17 является прозрачным, т,ене задерживает информацию на один такт. Наличие возможности инвертировать содержимое 45 счетчика обеспечивает работу устройства в режиме вычитания. Кроме того, устройство формирования адресов может использоваться как программируемый коммутатор, где на 1-й разряд выхода 29 можно подать информацию с 1-го разряда входа 24, Наличие входа 27 и выхода 30 переноса, а также возможность перевода 1-го разряда выхода 29 в третье состояние (состо яние высокого сопротивления) позволяют наращивать разрядность формирования адресов. Устройство для формирования адре. сов процессора быстрого преобразования Фурье, содержащее счетчик адреса и и коммутаторов (и - разрядность адреса), причем выход 1-го (1 = 1,п) разряда счетчика адреса подключен к 1-м информационным входам коммутаторов, о т л и ч а ю - щ е е с я тем, что, с целью расширения области применения за счет программирования алгоритма формирования адресов, в него введены дешифратор, пять групп элементов .И по и элементов в каждой, две группы элементов НЕ и п элементов в каждой, и входных регистров, п регистров номеров разрядов, и регистров управления, и дешифраторов разрядов, и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, и элементов ИЛИ и выходной регистр, причем первый вход задания параметра устройства подключен к входу дешифратора, 1-й (1 = 1,п) выход которого подключен к первому входу 1-го элемента И первой группы, первый тактовый вход устройства подключен к вторым входам элементов И первой группы, третьи входы которых соединены со счетным входом счетчика адреса, тактовым входом выходного регистра и подключены к второму тактовому входу устройства, выход 1-го элемента И первой группы подключен к тактовому входу 1-го входного регистра, информационные выходы которых объединены и являются вторым входом задания параметров устройства, вход 1-го элемента НЕ первой группы соединен с первым входом 1-го элемента И второй группы и является 1-м разрядом третьего входа задания параметра устройства, третьим тактовым входом которого являются соединенные между собой первые входы элементов И второй и третьей групп, выход 1-го элемента НЕ первой группы подключен к второму входу 1-го элемента И третьей группы, выход которого подключен к первому входу -го элемента ИЛИ, выход которого подключен к входу установки в "Оч-го разряда счетчика адреса, вторые входы элементов ИЛИ соединены между собой и являются четвертым тактовым входом устройства, пятым тактовым входом которого являются соединенные между собой тактовые вхоТираж 672 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушскаянаб., д,4/5. ды регистров номеров разрядов и регистров управления, выход-го элемента И второй группы подключен к входу установ ки в "1" 1-го разряда счетчика адреса, вход сигнала переноса устройства подключен к входу переноса счетчика, выход переноса которого является выходом переноса устройства, шестым тактовым входом которого являются соединенные междуфсобой установочные входы регистров номера разряда и регистров управления, выходы 109 п старших разрядов 1-го входного регистра подключены к входам соответствующих разрядов 1-го регистра номера разряда, а выходы первого и второго разрядов 1-го входного, регистра подключены к входам соответственно первого и второго разрядов 1- го регистра управления, выход 1-го регистра номера разряда подключен к входу 1-го дешифратора разрядов,-й выход которого подключен к 1-му управляющему входу 1-го коммутатора, выход которого подключен к первому входу,1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключенк выходупервого разряда 1-го регистра управления, выход второго разряда которо го подключен к установочному входу1-го разряда входного регистра, информационный вход -го разряда которого соединен с первым входом 1-гоэлемента И четвертой группы, входом1.го элемента НЕ второй группы иподключен к выходу 1-го элементаИСКЛ 10 ЧАЮЩЕЕ ИЛИ, выход 1-го элемента НЕ второй группы подключен к первому входу 1"го элемента И пятойгруппы, вторые входы которых соединены. с вторыми входами элементов Ичетвертой группы и являются седьмымтактовым входом устройства, выход1-го элемента И четвертой группы 20 подключен к входу установки в "1"1-го разрядавыходного регистра, входустановки в "0" которогоподключен квыходу 1-го элемента И пятойгруппы,а выход выходного регистра является информационным выходом устройства.

СмотретьЗаявка

4000574, 30.12.1945

ПРЕДПРИЯТИЕ ПЯ В-8751

МЕЛЬНИК АНАТОЛИЙ АЛЕКСЕЕВИЧ, ЦМОЦЬ ИВАН ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 17/14, G06F 9/34

Метки: адресов, быстрого, преобразования, процессора, формирования, фурье

Опубликовано: 07.06.1987

Код ссылки

<a href="https://patents.su/4-1315998-ustrojjstvo-dlya-formirovaniya-adresov-processora-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования адресов процессора быстрого преобразования фурье</a>

Предыдущий патент: Устройство для формирования координат сеточной области

Следующий патент: Устройство для вычисления коэффициентов фурье

Случайный патент: Агрегат для приготовления пластичного забоечного материала и заполнения им шпуров и скважин