Сумматор по модулю

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

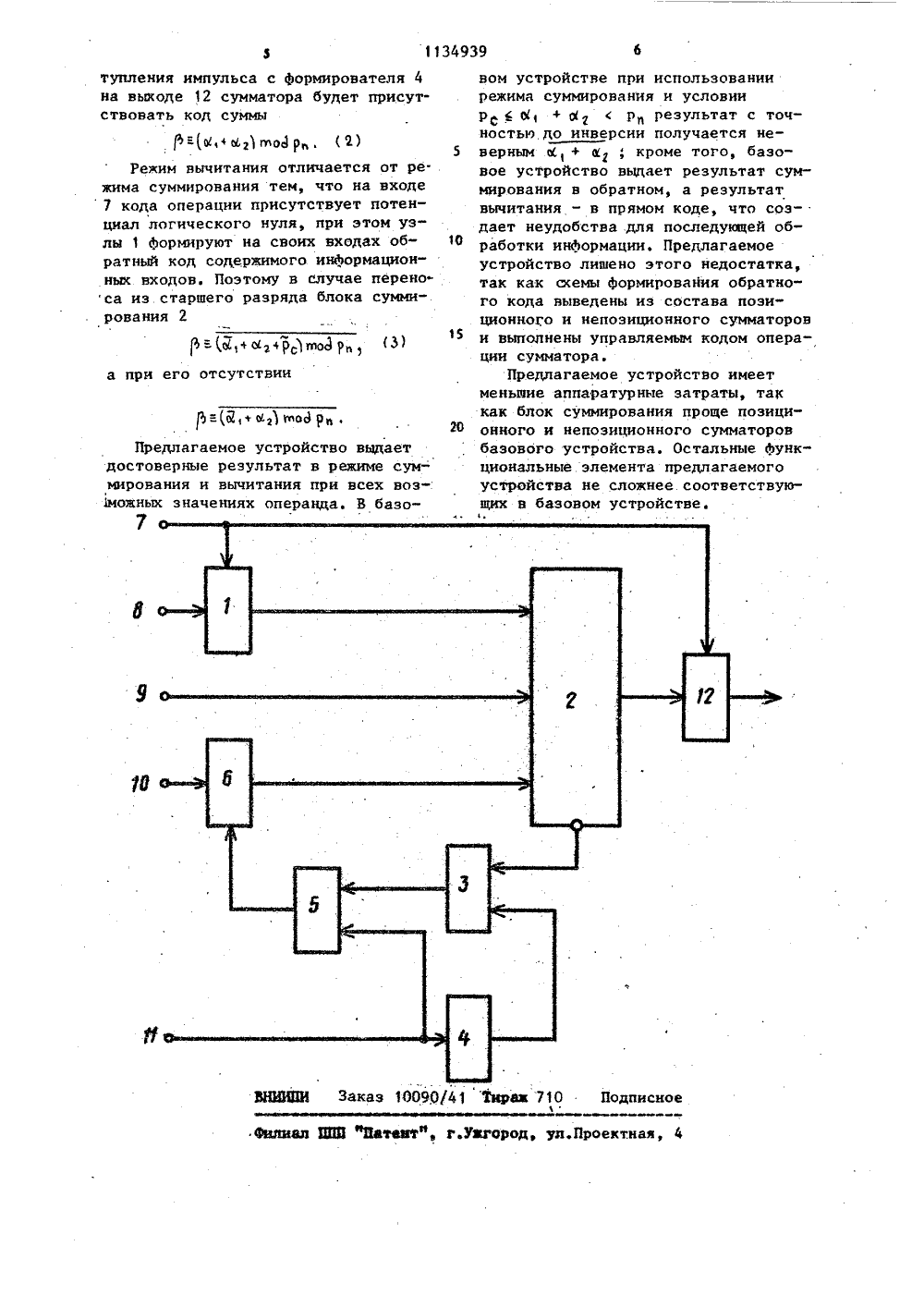

СОЮЗ СОВЕТСКИХсаваазпцевииРЕСПУБЛИК ОЕ 01) ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЙЬСГВУ(54)(57) СУММАТОР ПО МОДУЛЯ, содер-,жащий группу элементов И, блок сум.мирования, первый узел формированияобратного кода, причем информационный вход первого узла Формированияобратного кода является входом первого операнда сумиатора, выход первого узла Формирования обратного кода соединен с входом первого операида блока суммирования, вход второгооперанда которого. является входомвторого .операнда сумматора, уиравлякеий йход первого узла Формирова- -ния обратного кода является входомкода операции сумматора, о т л я 4(51) С 06 Р 11/00 С 06 Р 7/50 ч а ю щ и й с я тем, что, с цельюповышения достоверности суммирования, в него введены триггер, элементИ, Формирователь импульсов и второйузел Формирования обратного кодапричем вьвсод блока суммирования соединен с информационным входом второго узла Формирования обратного кода,выход которого является выходомсумматора, первые входы элементов Игруппы являются входами кода модуля суьвиторя, выходы элементов Игруппы соединены с входом третьегооперанда блока суммирования, выходпереполнения которого соединен сРпервым входом элемента И, выход кото- Щрого соединен с,нулевым входом тригера, прямой выход которого соединен Юфс вторыми входами элементов И группы, Сединичный вход. триггера и вход Формиронателя импульсов объединены иЯявляются входом запуска сумматора,выход Формирователя импульсов соединен с вторым входом элементя И, управпяюций вход второго узла Формирования обратного кода объединен свходом кода операции сумматора.Наиболее близким по технической сущности к изобретению является устройство, содержащее управляемые.инверторы, позиционный .и непозицион-ньй сумматоры, первые и вторые блоки ключей, инвертор, схему ИЛИ, выходы управляемых инверторовподключены к первым входам позиционного сумматора, первый и второй выходы которого подключены к соответствующим входам непозиционного сумматора, выходы которого подключены к вторым входам первых блоков ключей, первые входы которых соединены с управляющим выходом позиционного. сумматора и входом инвертора, выход которого подклю. чен к первым входам вторых блоков ключей, вторые входы которых соединены со вторыми выходами позиционного сумматора и входом инвертора, выход которого подключен к первым входам вторых блоков ключей, вторые входы которых соединены с вторыми выходами позиционного сумматора и входом инвертора, выход которого подключен к первым входам вторых блоков ключей, вторые входы которых 40 50 Изобретение относится к вычислительной технике и может быть использовано при построении однородных вычислительных систем, функционирующих .а системе остаточных классов (СОК), а также при проектировании типовых элементов замены, работающих по произвольному модулю, в системах контроля передачи дискретной информации.Известно ариЬметическое устройство в системе остаточных классов, содержащее приемные регистры, деши 4- раторы, схему преобразования в дополнительный код, матрицу запоминания результатов операций, схему выдачи результатов, в которых выходы первого приемного регистра через первый дешифратор, а выходы второго приемного регистра через второй дешифратор и схему преобразования в дополнительный код подключены к соответствующим входам матрицы запоминания результатов; выходы которой. подключены к входам схемы. выдачирезультатов 11 .Однако дайное устройство обладает низким быстродействием выполнения операции вычитания, большими аппаратурными затратами и не допускает работу по произвольному модулю. 5 1 О 152025 соединены с вторыми выходами позиционного сумматора, а выходы к второму входу элемента ИЛИ, первый вход которого соединен с выходами первых блоков ключей 21.Однако это устройство характери-зуется большими аппаратурными затратами, результаты суммирования и вычитания выдает в обратном и прямом кодах соответствейно, результат суммирования достоверен в ограниченном ( диапазоне изменения входных величин.Целью изобретения является повышение достоверности суммирования.Поставленная цель достигается тем, что в сумматор по модулю, содержащий группу элементов И, блок суммирования, первый узел Аормирования обратного кода, причем инАормационый вход первого узла Ьормирования обратного кода является входом первого операнда сумматора, выход первого узла Аормирования обратного кода соединен с входом первого операнда блока суммирования, вход второго операнда которого является входом второго операнда сумматора, управляющий вход первого узла Аормирования кода является входом кода операции сумматора, введены триггер, элемент И, формирователь импульсов и второй узел Аормирования обратного кода, причем выход блока суммирования соединен с информационным входом второго узла Формирования обратного кода, выход которого является выходом сумматора, первые входы элементов И группы являются входами кода модуля сумматора, выходы элементов И группы соединены с входом третьего операнда блока суммирования, выход переполнения которого соединен с первым входом элемента И, выход которого соединен с нулевым входом триггера, прямой выход которого соединен с вторыми входами элементов И группы, единичный вход триггера и вход формирователя импульсов объединены и являются входом запуска сумматора, выход Формирователя импульсов соединен с вторым входом элемента И, управляющий вход второго узла Аормирования обратного кода объединен с входом кода операции сумматора.На чертеже приведена структурная схема предлагаемого сумматора по модулю.Сумматор по модулю содержит первый и второй узлы 1 Аормирования об3 11349 ратного кода, блок 2 суммирования, элемент И 3, формирователь 4 нмпуль" сов, триггер 5, группу 6 элементов И, вход 7 кода операции, входы 8 и 9 первого и второго операндов сум 5 матора, входы 10 кода модуля сумматора, вход 11 запуска сумматора, выход 12 сумматора.Управляющие входы узлов 1 формирования обратного кода объединены с входом 7 кода операции сумматора. Дпя случая двоичного кодирования операндов узлы 1 представпяют собой управляемые поразрядные инверторы. ,При унитарном кодировании операндов узлы 1 содержат схему перестановки и коммутатор, причем индюрмационный вход узла формирования обратно" го кода соединен с первым входом коммутатора и входом схемы перестановки, выход последней соединен с вторым входом коммутатора, выход н управляющий вход которого являются выходом и управляющим входом узла формирования обратного кода. Информационный вход первого узла формирования обратного кода является входом. первого операнда сумматора, а выход соединен с входом первого операнда блока 2 суммирования. Блок 2 суммирования выполнен трехвходовым и может быть реализован, например, на двухвходовых сумматорах, выход переполнения его выполнен инверсным. Вход второго операнда блока суммирования является входом 9 второго .И операнда сумматора. Вход третьего операнда блока суммирования подключен к выходу группы 6 элементов И, первые. входы которых являются входом 10 кода модуля сумматора, а вторые фО входы объединены и подключены к прямому выходу триггера 5, единичный вход которого объединен со входом формирователя импульсов 4 и являются входом 11 запуска сумматора. Формирователь импульсов 4 может быть выполнен в виде триггера с одним устойчивым состоянием и фиксированным временем нахождения в нем, причем при переходе в исходное состоя- ЗО ние на его выходе появляется импульс. Выход формирователя 4 импульсов соединен с вторым входом элемента И 3, выход которого соединен с нулевым входом триггера 5, а первый вход - М с выходом переполнения блока 2 суммирования. Выход блока суммирования соединен с информационным входом 39 4второго узла формирования обратногокода, выход которого является выходом 12 сумматора.Предлагаемое устройство работает.следующим образом.Режим суммирования. Обозначим модуль, по которому работает блок суммирования, через ря, а модуль, по которому будет выполняться сложение,лчерез уС, тогда модуль сумматора рс, код которого будет подан на.входы10 устройства, определяется по формуле ро = р - р . В исходном состоянии на входе 7 кода операции присутствует потенциал логической "1", при этом узлы формирования обратного кода не изменяют на своем выходе содержимого своих информационных кодов. На выходах 8-10 выставлены коды операндов К Ки модуля сумматора рс. Состояние триггера 5 безразлично, формирователь 4 импульсов - в исходном состоянии.При подаче импульса на вход 11 запуска сумматора формирователь 4 ,импульсов переводится в рабочее сос. тояние, триггер 5 устанавливается в единичное состояние и потенциал логической единицы с его прямого выхода, поступая на вторые входы группы б элементов И, разрешает прохож-, дение кода модуля сумматора с входа 10 на вход третьего операнда блока суммирования, на выходе которого при. сутствует код суммы=-ЬфжР,)вод р,. Г 1)При наличии переноса из старшего разряда блока суммирования на его выходе переполнения присутствует потенциал логического "0", который запретит прохождение импульса с выхода формирователя импульсов 4 (по возвращении его в исходное состояние) через элемент И 3 на нулевой вход триггера 5. На выходе 12 сумма-. тора до прихода очередного импульса запуска будет присутствовать код результата согласно (1). Если на выходе переполнения блока суммирования будет присутствовать потенциал логической "1", то импульс с 1 юрмирователя 4 пройдет через элемент И 3 и переведет триггер 5 в нулевое состояние, что приведет к снятию ко" да модуля сумматора с входа третьего операнда блока 2 суммирования. Спустя время переходных процессов в блоках 3, 5, 6, 2 и 1 после пос1134939фМь 1 тоД( 2)Режим вычитания отличается от ре жима суммирования тем, что на входе 7 кода операции присутствует потенциал логического нуля, при этом узлы 1 Формируют на своих входах об О ратный код содержимого индюрмационных входов. Поэтому в случае переноса иэ старшего разряда блока сумми-. рования 215Ъ = (,М 1+ СС р Р 1 уев р 1 3) аж 710 Подписи каз 10090 г.Уагород, ул.Проектная, 4 тупления импульса с Формирователя 4на выходе 12 сумматора будет присутствовать код суммы а при его отсутствии=(Я 1 Ф кД ФОд РПредлагаемое устройство выдает достоверные результат в режиме суммирования и вычитания при всех воэ можных значениях операнда. В базоУ вом устройстве при использовании режима суммирования и условии рС й О + Ю с РРезультат с точностям По инверсии попучеется неверным М + нт, кроме того, бввовое устройство выдает результат суммирования в обратном, а результат вычитания - в прямом коде, что соэдает неудобства для последующей обработки инФормации. Предлагаемое устройство лишено этого недостатка, так как асемы Формирования обратного кода выведены из состава позиционного и непозиционного сумматоров и выпопнены управляемым кодом операции сумматора.Предлагаемое устройство имеет меньшие аппаратурные затраты, так как блок суммирования проще позиционного и непозиционного сумматоров базового устройства. Остальные Функциональные элемента предлагаемого устройства не сложнее соответствующих в базовом устройстве.1 ж

СмотретьЗаявка

3519549, 07.12.1982

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

ХЛЕВНОЙ СЕРГЕЙ НИКОЛАЕВИЧ, ЧЕРВЯКОВ НИКОЛАЙ ИВАНОВИЧ, ШВЕЦОВ НИКОЛАЙ ИВАНОВИЧ, ЦУПКО ВЛАДИМИР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 11/30, G06F 7/50

Опубликовано: 15.01.1985

Код ссылки

<a href="https://patents.su/4-1134939-summator-po-modulyu.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю</a>

Предыдущий патент: Приоритетное устройство

Следующий патент: Устройство для контроля блоков синхронизации

Случайный патент: Установка для обработки свободным абразивом