Сумматор кодов фибоначчи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1532915

Автор: Гусаков

Текст

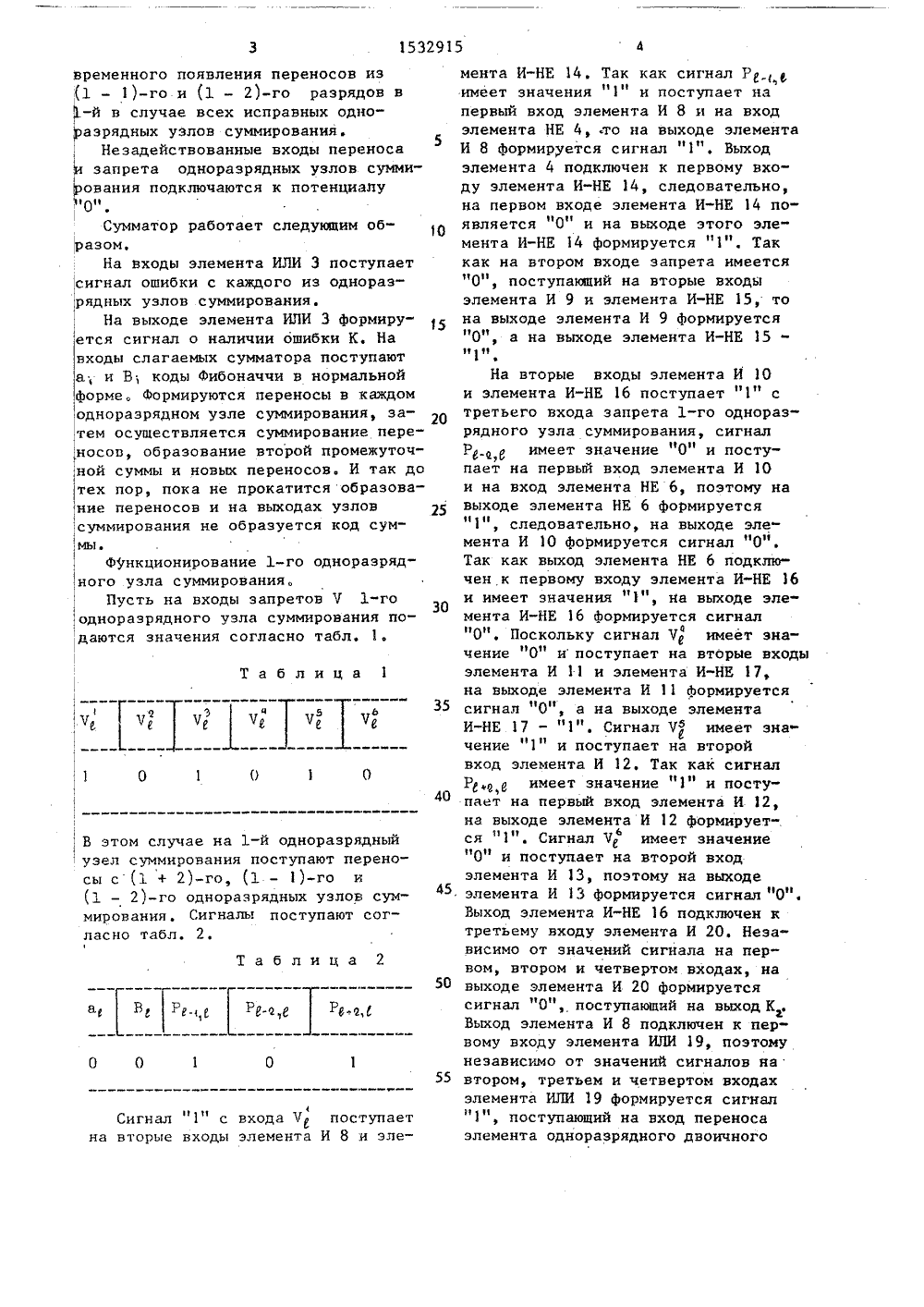

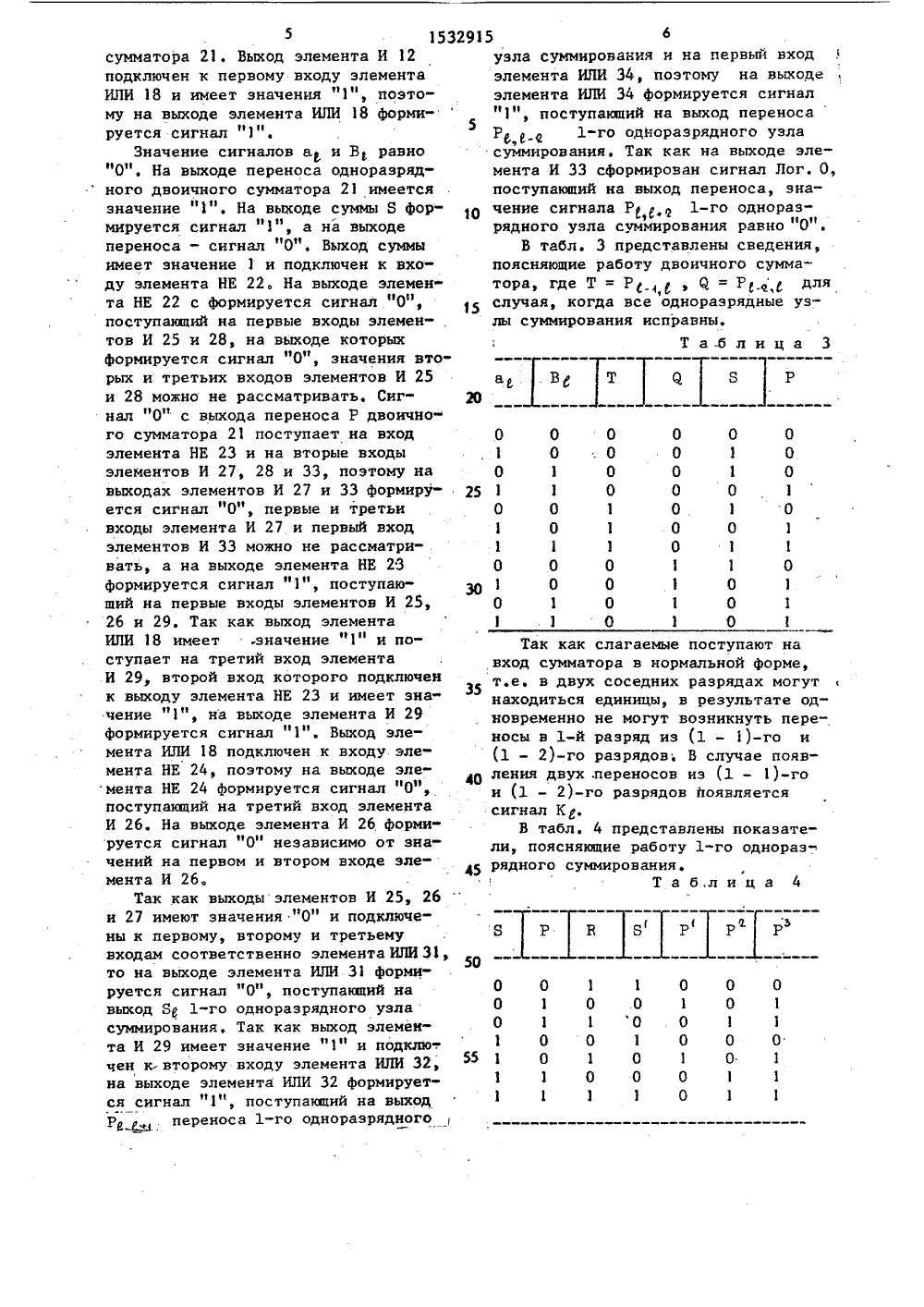

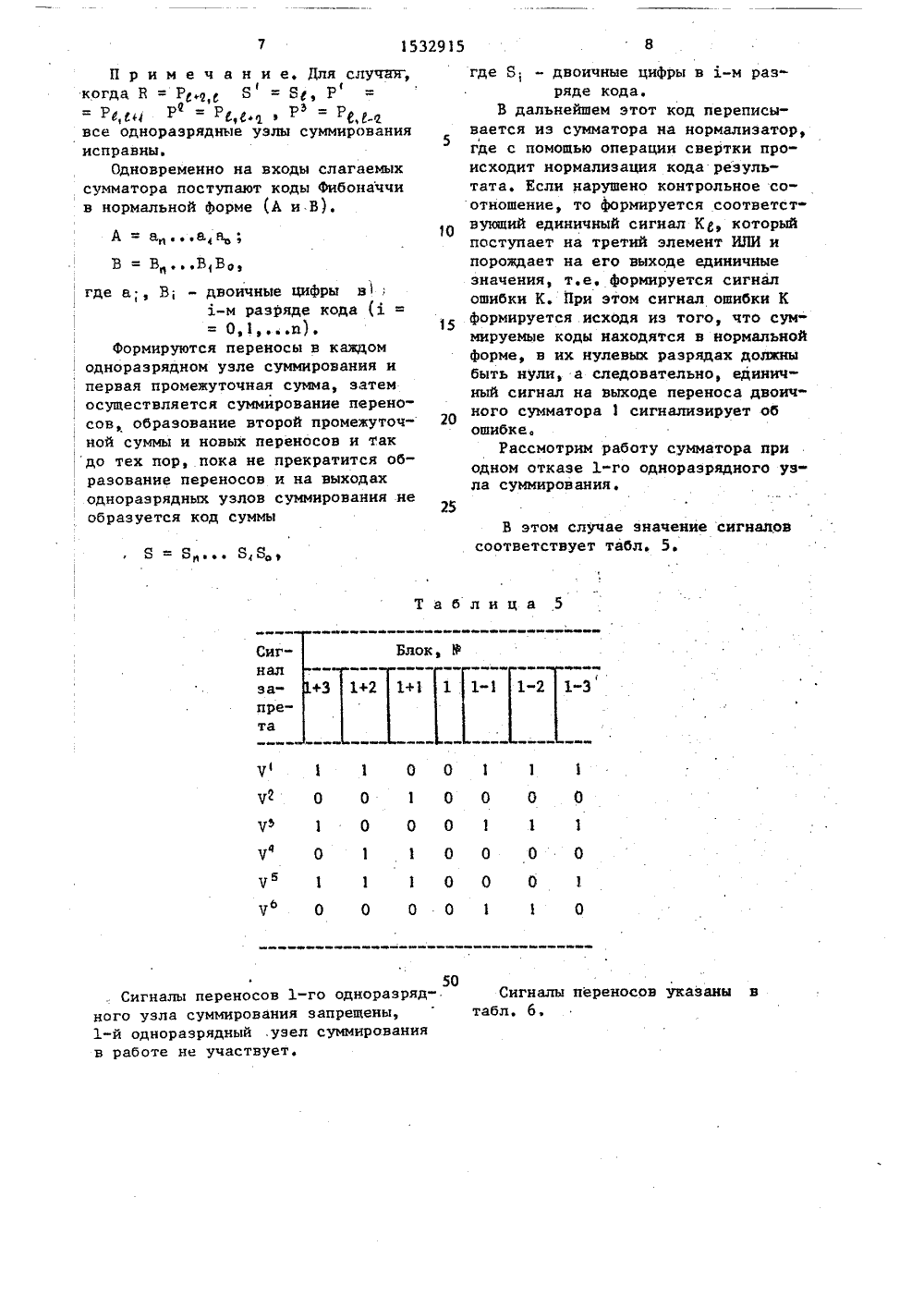

) 1В этом случае на 1-й одноразрядузел суммирования поступают песы с(1 + 2)-го, (Х - 1)-го иоступае 8 и эле временного появления переносов из (1 - 1)-го и (3. - 2)-го разрядов в -й в случае всех исправных одноазрядных узлов суммирования.Незадействованные входы переносазапрета одноразрядных узлов суммиования подключаются к потенциалу0",Сумматор работает следуиаим образом.На входы элемента ИЛИ 3 поступает ,сигнал ошибки с каждого из одноразрядных узлов суммирования,На выходе элемента ИЛИ 3 формируется сигнал о наличии ошибки К. На входы слагаемых сумматора поступают а; и В; коды Фибоначчи в нормальной форме. формируются переносы в каждом одноразрядном узле суммирования, затем осуществляется суммирование переносов, образование второй промежуточной суммы и новых переносов. И так до тех пор, пока не прокатится образование переносов и на выходах узлов 25 суммирования не образуется код сум)мы еФункционирование 1-го одноразрядного узла суммирования,Пусть на входы запретов 7 ,одноразрядного узла суммирован даются значения согласно табл. 1. мента И-НЕ 14. Так как сигнал Ре,имеет значения "1" и поступает на первый вход элемента И 8 и на вход элемента НЕ 4, .то на выходе элемента И 8 Формируется сигнал "1". Выход элемента 4 подключен к первому входу элемента И-НЕ 14, следовательно, на первом входе элемента И-НЕ 14 появляется "0" и на выходе этого элемента И-НЕ 14 формируется "1". Так как на втором входе запрета имеется "0", поступающий на вторые входы элемента И 9 и элемента И-НЕ 15, то на выходе элемента И 9 формируется "0", а на выходе элемента И-НЕ 15-1На вторые входы элемента И 10 и элемента И-НЕ 16 поступает "1" с третьего входа запрета 1-го одноразрядного узла суммирования, сигнал РЕ.римеет значение О и поступает на первый вход элемента И 1 О и на вход элемента НЕ 6, поэтому на выходе элемента НЕ б формируется1 , следовательно , н а выходе элемента И 1 О формируется сигнал " 0" . Так как выход элемента НЕ 6 подключен к первому входу элемента И-НЕ 1 6 и имеет значения " 1 " , на выходе элемента И-НЕ 1 6 формируется сигнал0 . Поскольку сигнал 7 Е имеет знарчение "0" ипоступает на вторые входы элемента И 11 и элемента И-НЕ 17, на выходе элемента И 11 формируется сигнал "О", а на выходе элемента И-НЕ 17 - "1". Сигнал Уз имеет значение 1и поступает на второй вход элемента И 1 2 , Так как сигнал Ре р е имеет значение " 1 " и поступает на первый вход элемента И 1 2 , на выходе элемента И 1 2 формируется 1 . Сигнал 7 е имеет значение3ь"О" и поступает на второй вход элемента И 13, поэтому на выходе элемента И 13 формируется сигнал "0". Выход элемента И-НЕ 16 подключен к третьему входу элемента И 20. Независимо от значений сигнала на первом, втором и четвертом входах, на выходе элемента И 20 формируется сигнал "0", поступающий на выход К .г Выход элемента И 8 подключен к первому входу элемента ИЛИ 19, поэтому независимо от значений сигналов на втором, третьем и четвертом входах элемента ИЛИ 19 формируется сигнал в 1 поступающии на вход переноса элемента одноразрядного двоичного5О15 0 0 0 О; 0 0 1 0 О 1 О 0 О 1 0 0 1 0 10 0 0 1 0 0 1 1 0 1 1 0 1 О 0 1 0 1 0 0 1 1 0 01 1 0 00 1 О 1 0 1 О 1 0 1 0 1 О 1 50 0 1 1 О 1 1 1 0 0 0 1 1 1 1 55 5 153 сумматора 21. Выход элемента И 12 подключен к первому входу элемента ИЛИ 18 и имеет значения "1", поэтому на выходе элемента ИЛИ 18 формируется сигнал "1".Значение сигналов аЕ и Ве равно "0". На выходе переноса одноразрядного двоичного сумматора 21 имеется значение . На выходе суммы Б формируется сигнал "1", а на выходе переноса - сигнал "0", Выход суммы имеет значение 1 и подключен к входу элемента НЕ 22. На выходе элемен та НЕ 22 с формируется сигнал "О", поступаккий на первые входы элемен-, тов И 25 и 28, на выходе которых формируется сигнал "0", значения вторых и третьих входов элементов И 25 и 28 можно не рассматривать, Сигнал "О" с выхода переноса Р двоичного сумматора 21 поступает на вход элемента НЕ 23 и на вторые входы элементов И 27, 28 и 33, поэтому на выходах элементов И 2 и 33 формируется сигнал "0", первые и третьи входы элемента И 27 и первый вход элементов И 33 можно не рассматривать, а на выходе элемента НЕ 23 формируется сигнал "1", поступающий на первые входы элементов И 25, 26 и 29. Так как выход элемента ИЛИ 18 имеет .значение "1" и поступает на третий вход элемента И 29 второй вход которого подключен к выходу элемента НЕ 23 и имеет значение "1", на выходе элемента И 29 формируется сигнал "1". Выход элемента ИЛИ 18 подключен к входу элемента НЕ 24, поэтому на выходе элемента НЕ 24 формируется сигнал "О"поступающий на третий вход элемента И 26, На выходе элемента И 26 формируется сигнал "0" независимо от значений на первом и втором входе элемента И 26.Так как выходы элементов И 25, 26 и 27 имеют значения "0" и подключены к первому, второму и третьему входам соответственно элемента ИЛИ 31, то на выходе элемента ИЛИ 31 формируется сигнал "0", поступающий на выход ЯЕ 1-го одноразрядного узла суммирования. Так как выход элемемта И 29 имеет значение "1" и подклю-. чен к.второму входу элемента ИЛИ 32, на выходе элемента ИЛИ 32 формируется сигнал "1", поступакщий на выход Репереноса 1-го одноразрядного 2915 6 узла суммирования и на первый вход элемента ИЛИ 34, поэтому на выходе элемента ИЛИ 34 формируется сигнал "1", поступающий на выход переносаРЕ Е1-го одиоразрядного узла1суммирования. Так как на выходе элемента И 33 сформирован сигнал Лог, О, поступающий на выход переноса, значение сигнала Р . 1-го одноразрядного узла суммирования равно "О",В табл. 3 представлены сведения, поясняющие работу двоичного сумматора, где т = РЕ.л,4 = РЕ.с,Е для случая, когда все одноразрядные узлы суммирования исправны.Таблица 3 аЕ ВЕ т Ц и Р Так как слагаемые поступают навход сумматора в нормальной форме,т.е. в двух соседних разрядах могутнаходиться единицы, в результате одновременно не могут возникнуть переносы в 1-й разряд из (1 - 1)-го и= Рг,еч Р Р 6,ГР РВ,Е-авсе одноразрядные узлы суммированияисправны.Одновременно на входы слагаемыхсумматора поступают коды Фибоначчив нормальной форме А и В),В = В, еЭ,ВО,где а;, В; - двоичные цифры в 1:З.-м разряде кода (3. -"= 0,1,п).Формируются переносы в каждом одноразрядном узле суммирования и первая промежуточная сумма, затем , осуществляется суммирование перено сов, образование второй промежуточ; ной суммы и новых переносов и такдо тех пор, пока не прекратится образование переносов и на выходах одноразрядных узлов суммирования не образуется код суммы Сигналы переносов 1-го одного узла суммирования эапр1-й одноразрядный .узел суммв работе не участвует. где Б; - двоичные цифры в х-и разряде кода.В дальнейшем этот код переписы 5вается иэ сумматора на нормализатор,где с помощью операции свертки происходит нормализация кода результата. Если нарушено контрольное соотношение, то формируется соответствующий единичный синал К, коорыйпоступает на третий элемент ИЛИ ипорождает на его выходе единичныезначения, т.е. формируется сигналошибки К. При этом сигнал ошибки Кформируется исхОдя из тогор что суммируемые коды находятся в нормальнойформе, в их нулевых разрядах должныбыть нули, а следовательно, единичный сигнал на выходе переноса двоичного сумматора 1 сигнализирует обошибке.Рассмотрим работу сумматора приодном отказе 1-го одноразрядного узла суммирования,2 В этом случае значение сигналовсоответствует табл. 5. Сигналы переносов указаныбл. 6.,г,е-с 1+3 1+2 1+1 1 для одноразрядных узлов суммиро вания, не указанных в табл. 6, сигналы переносов такие же, как для (1 + 3)-го и (1 - 3)-го блоков.В формировании суммы аЕ и де не участвуют и значения их не рассматри веются. В формировании переносов переносы. 1-го одноразрядного сумматора не участвуют, следовательно, суммаСигналы переносов Т, Я, В, постутор не теряет функционирования при выходе из строя одного одноразрядного узла суммирования.Рассмотрим работу сумматора для случая выхода из строя 1-го и.(1+3)-го одноразрядных узлов суммирования Сигналы запретов имеют значениясогласно табл. 7,)т а )к РЕ+т,Е в Рев,сРсц с Рс,с,с.в Рс,в,е в Рс.с,с с Рс.е,е в Рс.М.с Рс.ф,с РС.,С. Ре.с,е Рс.е,е в0Рс.е,с Рс с,е-е Рсв,с э Ре.сРем,сей Рс ,сч Рс с,ес Р Ецси 0 РЬа,е;с 0 Рсс в РЕ.Ес Как видно, сумматор не теряетфункционирования при выходе иэ строядвух узлов.При вычислении суммы значения а ,В, а Е,Ь И ВР.,с, НЕ уЧаСтВуЮт И На)результат суммы не влияют. Как видно из табл. 10 и 9, сигнаы переносов с отказом трех .однораовых узлов суммирования блокируютя и сумматор не теряет функционироания.Таким образом, сумматор правильно функционирует при отказах не только Х-го но и последующих эа ним ЗК (где К - целое число) одноразрядных узлов суммирования. Формула изобретения 1. Сумматор кодов Фибоначчи, содержаший и+1 одноразрядных узлов суммирования (и+1-разрядность кода) и элемент ИЛИ, причем первый и второй входы слагаемых 1-го одноразрядного узла суммирования (1 щ 1и+1) соединены с входами 1-х разрядов первого и второго слагаемых сумматора соответственно, выход сум" мы 1-го одноразрядного узла суммиВ случае отказа трех одноразрядных узлов суммирования 1, 1 + 3,1 + 6, значения сигналов запретов 5указаны в табл. 9; значения Т, Ц и Внаходят из табл. 10. рования является выходом 1-го разряда суммы сумматора, выход ошибки которого соединен с вйходом элемента ИЛИ, 1-й вход которого соединен с контрольным выходом 1-го одноразрядного узла суммирования, первый вход переноса 1-го одноразрядного узла суммирования подключен к перво му выходу переноса (1-3)-го. одноразрядного узла суммирования, второй вход переноса 1-го одноразрядного узла суммирования подключен к третьему выходу йереноса (1+2)-го одноразрядного узла суммирования, третий вход переноса 1-го однораз" рядного узла суммирования подключен к второму выходу переноса (1-2)-го одноразрядного узла суммирования, о т л и ч а ю щ и й с я тем, что, с целью повышения надежности за счет обеспечения функционирования при отказах одноразрядных узлов суммирования, четвертый вход переноса 1-го одноразрядного узла суммирования подключен к первому выходу переноса (1-2)-го одноразрядного узласуммирования, пятый вход переноса1-го одноразрядного узла суммирования к второму выходу переноса(1-3)-го одноразрядного узла суммирования, шестой вход переноса 1-гоодноразрядного узла суммированияподключен к третьему выходу перено.са (1+3)-го одноразрядного узла суммирования с первого по шестой входы запрета 1-го одноразрядного узласуммирования являются соответствующими входами запрета 1-й группысумматора.2Сумматор по п. 1, о т л и -ч а ю щ и й с я тем, что одноразрядный узел суммрни содержит с,первого по седьмой элементы НЕ,с первого по тринадцатый элементыИ, с первого по четвертый элементыИ-НЕ, с первого по шестой элементы,ИЛИ и двоичный одноразрядный сумматор, причем первый вход переносаодноразрядного узла суммированияподключен к первому входу первогоэлемента И и к входу первого элемента НЕ, второй вход переноса одноразрядного узла суммирования подключенк первому входу пятого элемента И,третий вход переноса одноразрядногоузла суммирования подключен к первому входу третьего элемента И и квходу третьего элемента НЕ, четвер 35тый вход переноса одноразрядногоузла суммирования подключен к первому входу второго элемента И и входувторого элемента НЕ, пятый вход переноса одноразрядного узла суммирования подключен к первому входу четвертого элемента И и к входу четвертого элемента НЕ, шестой входпереноса одноразрядного узла сумин" 45рования подключен к первому входушестого элемента И, выходы с первогопо четвертый элементов НЕ соединеныс первыми входами соответствующихэлементов И-НЕ, первый вход запретаодноразрядного узла суммированияподключен к вторым входам первыхэлементов И и И-НЕ, второй вход запрета одноразрядного суммированияподключен к вторым входам вторыхэлементов И и И-НЕ, третий вход запрета одноразрядного узла суммирования подключен к вторым входам третьих элементов И и И-НЕ, четвертый вход запрета одноразрядного узласуммирования подключен к вторым входам четвертых элементов И и И-НЕ,выходы пятого и шестого элементов Иподключены соответственно к входампервого элемента ИЛИ, вход переносадвоичного одноразрядного сумматорапоцключен к выходу второго элементаИЛИ, выход седьмого элемента И подключен к контрольному выходу одноразрядного узла суммирования, выходсуммы двоичного одноразрядного сумматора подключен к входу пятого элемента НЕ, к первым входам девятого,десятого, двенадцатого элементов Ии к первому входу третьего элементаИЛИ, выход переноса двоичного одноразрядного сумматора подключен квходу шестого элемента НЕ, к второмувходу десятого элемента И и к первым входам одиннадцатого и тринадцатого элементов И, пятый вход запретаодноразрядного узла суммированияподключен к второму входу пятогоэлемента И, шестой вход запрета одноразрядного узла суммирования подключен к второму входу шестого элемента И, первый и второй входы слагаемых двоичного одноразрядного сумматора подключены к первому и второму входам слагаемых одноразрядногоузла суммирования, выходы первого,второго, третьего и четвертого элементов И подключены соответственнок входам второго элемента ИЛИ, выходы первого, второго, третьего ичетвертого элементов И-НЕ подключены соответственно к входам седьмогоэлемента И, выход пятого элементаНЕ соединен с первым входом восьмогоэлемента И и с вторым входом одиннадцатого элемента И, выход шестогоэлемента НЕ подключен к вторым вхо дам восьмого, девятого и двенадцатого элементов И, выход первогоэлемента ИЛИ подключен к входу седьмого элемента НЕ, к третьим входамвосьмого, десятого, двенадцатогоэлементов И и к второму входу третьего элемента ИЛИ, выход седьмого элемента НЕ подключен к третьим входамдевятого и одиннадцатого элементовИ, выходы восьмого, девятого и десятого элементов И подключены соответственно к входам четвертого элемента ИЛИ, выходы одиннадцатого идвенадцатого элементов И подключенысоответственно к входам пятого эле;оставитель А.Техред Л.Олийнь в ктор С.Черни актор Л, Пчолинска Тираж 668 омитета по изобретени осква, Ж, Раушская Подписноем и открытиям при аб д, 4/5 аказ 8100)53 НИИПИ Государственног 113035О 1 но-издательский комбинат "Патент", г, Ужгород, ул, Гаг изводс мента ИЛИ, выход третьего элементаИЛИ подключен к второму входу тринадцатого элемента И, выход четвертого элемента ИЛИ подключен к выходусуммы одноразрядного узла суммирования, выход пятого элемента ИЛИПодключен к первому входу шестогоЬлемента ИЛИ и к первому выходу переноса одноразрядного узла суммирования, выход тринадцатого элементаИ подключен к второму входу шестогоэлемента ИЛИ и второму выходу пере"носа одноразрядного узла суммирования, выход шестого элемента ИЛИподключен к третьему выходу переносаодноразрядного узла суммирования.

СмотретьЗаявка

4337360, 04.12.1987

ПРЕДПРИЯТИЕ ПЯ А-1001

ГУСАКОВ АЛЕКСАНДР МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 13/53

Метки: кодов, сумматор, фибоначчи

Опубликовано: 30.12.1989

Код ссылки

<a href="https://patents.su/8-1532915-summator-kodov-fibonachchi.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор кодов фибоначчи</a>

Предыдущий патент: Устройство для поиска заданного числа

Следующий патент: Накапливающий сумматор

Случайный патент: Способ получения смачивателя шерстяных тканей