Устройство для вычисления суммы п к-разрядных р-ичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 652559

Автор: Брюхович

Текст

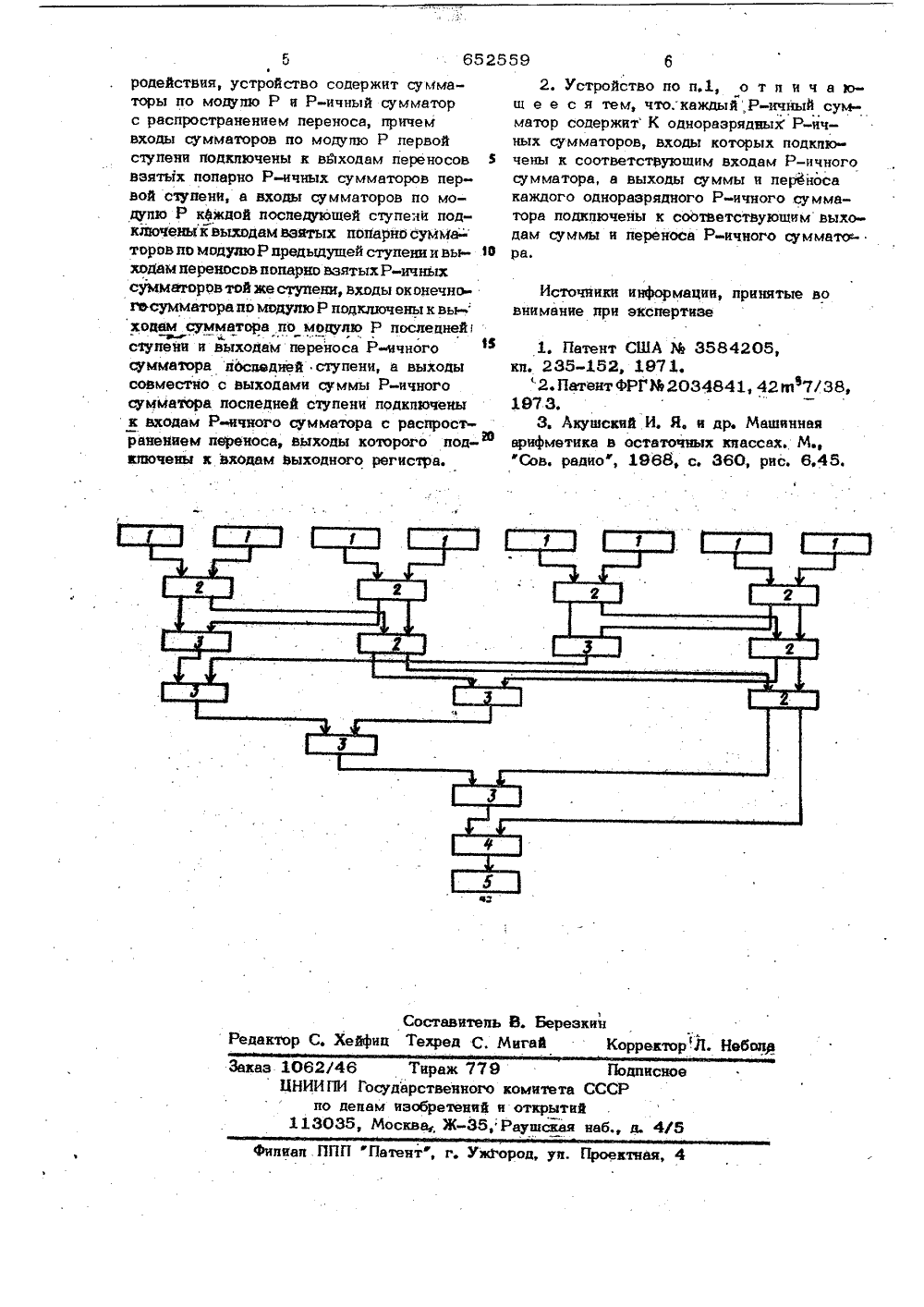

ОП ИСАНИЕИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДИТВЛЬСТВУ Сотов СоввтенихСфцнаеетнцесюеРвсаублин)М. К 385 присоединением зая евударвтввккмй кенктет СССР лакам юзФбра 19 ккк к еткрнтий(72) Автор изобретения Е. И. Брюхов ина институт кибернетики АН Украинской С(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММ К-РАЗРЯДНЫХ . Р-ИЧНЫХ ЧИСЕЛеды ых сумма 1Изобретение относится к области вы- чиспитепьной техники и предназначено дпя споження групп чисел в системах счисления с большими основаниями.Известны устройства, в которых выпопнение арифметических и погических операций осушествпяется путем обращения к матрице ГЦМЭти устройства характеризуются бопь шой сложностью управления и невозможностью одновременной обработки бопьшого копичества операндов.Наиболее бпиэким по технической сущ ности к изобретению является устройство для вычисления суммы и К-разрядных чисеп, которое, в частности, может быть испопьзовано дпя спожения чисеп в Р-ичной системе счиспения. Это устройство содержит П входных регистров, выходной регистр и сумматоры, входы сумматоров первой ступени подкшочены к выходам попарно взятых входных регистров, а входы сумматоров каждой поспедующей ступени подкпючены к выходам суммы попарно взят торов пр душейступени 31,Однако такое устройство обладаетнедостаточным быстродействие м ввидутого, что в каждом из сумматоров каждойступени происходит поспедоватепьноераспространение переноса от младшихразрядов к старшим.Целью изобретения явпяется увепичение быстродействия.Это достигается тем, что предлагаемое устройство дпя вычиспения суммый К-разрядных Р-ичных чисел, содержащее И входных регистров ( И С Р+1),выходной регистр и Р-ичные сумматоры,причем входы Р-очных сумматоров первойступени подключены к выходам попарновзятых входных регистров, а входыР-ичных сумматоров каждой поспедуюшей ступени подкпючены к выходам попарно взятых Р-ичных сумматоров предыдущей ступени, вкпючает в себя сумматоры по модулю Р и Р-ичный су рс распространением переноса, причемторов 3 по модущо Р и лишь в юнце 46операции суммнруются: с некорректированным результатом на сумматоре 4 с рас, нространением переноса. 1. Устройство для вычисления суммы-И К-разрядных Р-ичнык чисел, содержа- - шее а входных регистров ( И С Р+1), выходной регистр и Р-ичные сумматоры,причем входы Р-ичных сумматоров первой ступени подключены к выходам попарно взятых входных регистров, а входы Р-ичных сумматоров каждой доследующей ступени подключены к выходам суммы попарно взятых Р-ичных сумматоровпредыдущей ступени, о т л и ч а ю ш ее с я тем, что, с целью увеличения быстЗаходы сумматоров по модулю Р каждой первой ступени подключены к выходам переносов взятых попарно Р-ичных сумматоров первой ступени, а входы сумматоров по модулю Р каждой последующей ступени подключены .к выходам взятых попарно сумматоров по модущо Р предыдущей ступени и выходам переносов . попарно взятых Р-ичных сумматоров той же ступени, входы оконечного сумматора по модулю Р подключены к выходам сумматора но модулю Р последней ступени и выходам переноса Р-ичного сумматора последней ступени, и выходы совместно с выходами суммы Р-нчного сумматора последней ступени подкщочены ко входам Р-ичного сумматора с распространением переноса, выходы которого подкщочены ко входам выходного рег истра.Кроме того, каждый Р-ичный сумматор может содержать К одноазрйдных Р-ичных сумматоров, входы которых подключены к соответствующим входам Р-ичного сумматора, а выходы суммы и переноса каждого одноразрядного Р-ичного сумматора подкщочены к соответствующим выходам суммы и переноса Р-ичного сумматора.На чертеже изображена структурная36 схема описываемого устройства, содержащего п входных регистров 1 (где .И 4 Р+1), Р-ичные сумматоры 2, сумматоры 3 по модулю Р, Р-ичный сумматор 4 с распространением переноса, выходной регистр 8.С выходов регистров 1 слагаемые, каждый Р-ичный разряд которых представлен в коде "1 из Р, поступают пбпарно на входы сумматоров 2 первой ступени, каждый, из которых содержит М одноразрядных Р-ичных сумматоров. На выходах атих одноразрядных Р-ичных сумматоров образуется сумма по модулю4Р данного разряда и перенос в соседний старший разряд. Выходы суммы попарно, взятых сумматоров 2 нарвой счупе ни подключены ко входам соответствующих разрядов сумматоров 2 второй ступе ни, на выходах которых также образуют ся сигналы суммы по модущо Р и переноса в соседний старший разряд. Выходы переноса попарновзятйх сумматоров 2 первой ступени подключены ко входам сумматоров 3 по модулю Г первой ступени, на выходах каждого из которых образуются:сигналы поразрядной су ммы по модущо Р. Выходы сумматоров 3 по модулю Р второй ступени подключены к выходам взятых попарно сумматоров 3 по модулю Р первой ступени, к выходам переносов взятых попарно Р-ичных сумматоров 2 второй ступени, Иодключение Р-ичных сумматоров 2 и сумматоров 3 по модулю Р последующих ступеней производятся аналогично описанному. Входи оконечного суьветора 3 по модулю Р подключены к выходам переноса Р-ичного суммато ра 2 и сумметора 3 по модулю Р последней ступени, а выходы его совмест но с выходами суммы Р-ичного сумматора 2 последней ступени подкщочены ко входам Р-ичного сумматора с распространением переноса 4, выходы которого подключены ко входам регистра 5, на который поступает результат операции в коде "1 из Рф,Одноразрядные сумматоры, образующие К разрядные Р-нчные сумматоры 2 для максимального повышения быстродействия, могут быть выполнены по мат ричной схеме. Из таких же сумматоров образованы сумматоры 3 по модулю Р с той лишь разницей, что они не образуют сигналов переноса в соседний старший разряд,Повышение быстродействия в данном устройстве происходит за счет того, что в Р-ичных сумматорах 2 не производится распространения Сигнала переносаза искщочением сумматора, на которомполучается окончательный результат,а сигналы переноса, образованные одновременно с сигналами сумм, сумми-,руются параллельно с помощью суммаФормула изобретения. Хейфид Техред С, Мигай КорректорЛ, Небоп Реда каз 1262/46 Тираж 779 Подпис ЦНИИ ПИ Государственного комитета СССР по делам изобретений и открытий 113235, Москва Ж,Раушская наб., д. 4тф, г. УМГород, ул, Прое Филиал ППП г 6525родействия, устройство содержит сумматоры по модулю Р и Р-ичный сумматор с распространением переноса, причем входы сумматоров по модулю Р первой ступени подклочены к вйходам переносов 3 взятых попарно Р-ичных сумматоров первой ступени, а входы сумматоров по модулю Р каждой последующей ступени подключенык выходам взятых попарно сумма-" торов по модулю Р предыдущей ступени и вы ходам переносов попарно взятых Р-ичных сумматоров той же ступени, входы оконечнь гв сумматора по модулю Р подключены к вы- ходам сумматора по модулю Р последней стуйени и выходам переноса Р-ичного ф сумматора последней ступени, а выходы совместно с выходами суммы Р-ичного сумматора последней ступени подключены к входам Р-ичного сумматора с распростИ ранением переноса, выходы которого подключены к входам Выходного регистра. 2. Устройство по п.1, о т л и ч а юш е е с я тем, что. каждый,Р-ичный сумматор содержит К одноразрядньцС Р-ичных сумматоров, входы которых подключены к соответствующим входам Р-ичного сумматора, а выходы суммы и переноса каждого одноразрядного Р-ичного сумматора подключены к соответствующим выходам суммы и переноса Р-ичного суммато- ра. Источники информации, принятые вовнимание при экспертизе 1. Патент США % 3584225,кл. 235-152, 1971.2. Патент фРГЬ 2034841, 42 в 7/38 в197 3.3. Акушский И. Я, и др. Машиннаяарифметика в остаточных классах. М.,

СмотретьЗаявка

2382176, 08.07.1976

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УКРАИНСКОЙ ССР

БРЮХОВИЧ ЕВГЕНИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/385

Метки: вычисления, к-разрядных, р-ичных, суммы, чисел

Опубликовано: 15.03.1979

Код ссылки

<a href="https://patents.su/3-652559-ustrojjstvo-dlya-vychisleniya-summy-p-k-razryadnykh-r-ichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления суммы п к-разрядных р-ичных чисел</a>

Предыдущий патент: Устройство для сортировки чисел

Следующий патент: Устройство для умножения десятичных чисел

Случайный патент: Способ производства мясных полуфабрикатов