Устройство для умножения десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 652560

Автор: Пешков

Текст

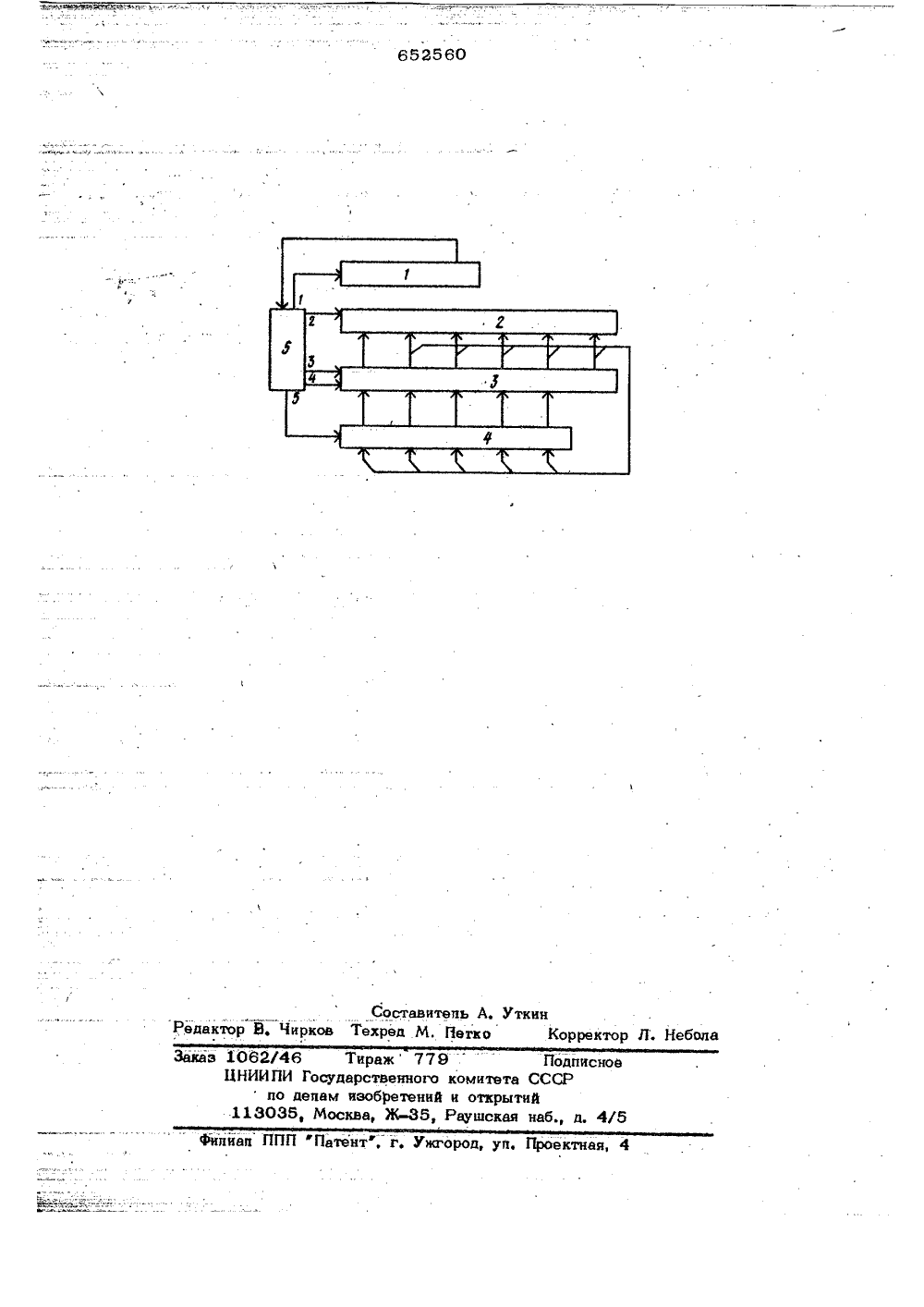

(21) 23447 31/18-2 51) исоединением заявки И Гмударственкый каыктет СССР в делам хзфбрвтекк а еткрыткй23) Приоритет Опубликовано Дата опубли 15,03,79.Бюллете н ования описания 19 УДК 681 32 д(Т 1) Заквнтеиь инский радиотехнический инс ЖЕНИЯ ДЕСЯТИЧН УСТРОЙСТВО ДЛЯ СЕЛ дикен блока с информаформирован й входы у срответст ым выход и вт екь четверт устройствалнекия умнотичных чисел,ширение оба путем выия над целыНедостатко мявляется возмож звестн ого ость вып жения только дробных десБель изобретения - рас пасти применения устройст полнения операции умноже ми и дробными числами,С атой целью в него введен дополнительный регистр, информационные вх ды которого соединены с информационными выходами младших тетрад блока формирования мкожимого, информационные входы старщих тетрад которого по ключены к выходам дополнительного ре гистра, к управляющему входу которог подключен пятый выход блока управпе- нияа Областьприменения изобретения -вычислительная техника, где оно монк.тбыть использовано при построении деся-.тичных и десятично-двоичных арифметических устройств,Известно устройство И , содержащее арегистр множимогоблок последовательного накопления чисел, кратных множимому, блок сдвига, блок суммированиячастичных произведений, регистр множителя, блок определения очередности цифр.Недостатком известного устройстваявляется его сложность.Наиболее близким по техническойсущности к предложенному изобретениюявляется устройство 21, содержащее15регистр множителя, блок формированиямножимого, сумматор, блок управления,первый выход которого соединен со входом управления регистра множителя,26выход которого соединен со входомблока управления, второй выход которогосоединен со входом управлекия сумматора, информационные входы которого соег(и)652560 ционными выходамия множимого; первыйравления которого соевенно с третьим ими блока управления.,652560 4теом и четвертом выходах, что обеспечивает сдвиг содержимого регистра множитепя на один двоичный разряд вправо иумножение десятичного кода, имеющегосяУ в это время в бпоке 3 на два. На этомзаканчивается первый такт первого цикла,на котором отрабатывается младший двоичный разряд младшей десятичной цифрымножителя.Второй и третий такты первого цикпавыполняются так же, как и первый такт,но при этом в начапе такта не вырабатывается сигнап на пятом выходе блокауправления и в регистре 4 в течение всего цикла сохраняется значение, принятоев него в начале первого такта этогоцикла, Четвертый такт выпопйяется также, как и третий и второй с той лищьразницей, что на этом такте вместо сиг 26 нала на выходе четыре бпока управленияФормируется сигнал на выходе 3 этогоже бпока управпения. Этот сигнаппоступая на первый вход блока 3 обеспечивает прием в его старшие тетрады всететрады, кроме младшей) кода из регистра 4, при этом в мпадшей тетраде бпока3 устанавливается нупевое значение. Сзавершением выполнения четвертого такта заканчивается первый цикп работы устф ройства, Все остапьные цикпы выпопняются аналогично первому.Результат умножения будет сформирован в сумматоре поспе завершения четвертого такта цикпа обработки старшейЗф цифры множителя.Работу данного устройства можнопояснить на примере выполнения умножения двух конкретных десятичных чисел:Х 39 множитепь).и У=85 множи 40 мое). Вэтом.спучае в системе 8, 4,2, 1 имеем:Х = 0011 1001;У = 1000 0101;Действия на отдельных тактах двух цик 45лов можно представить следующим образом: ОО 01 2 такт На чертеже приведена структурнаясхема устройства дпя умножения десятичных чисел.Устройство содержит регистр множитепя 1, сумматор 2, блок формированиямножимого 3, допопнитепьный регистр4,бпок управпения 5.Устройство работает следующим образом.Перед начапом умножения в регистрмножителя 1 заносится десятичный кодмиожитепя, в младшие тетрады блокаформирования множимого 3 заносится кодмйожи мого,Умножение осуществляется за.чиспоцикпов, равное разрядности десятичныхоперандов, при этом в каждом цикпе осуществляется умножение множимого наодин десятичный разряд множителя, начиная с младшего, Каждый цикл состойтиз четырех тактов по числу разрядов,представпения десятичных цифр в двоичнодесятичной системе 8, 4, 2, 1,Начинается умножение с цикла обработки мпадшего разряда множителя, Напервом такте вырабатывается сигнап напятом выходе блока управления и кодцифр, зафиксированных в мпадших тетрадах бпока 5, заносится в регистр 4.Одновременно, еспи присутствует сигнална входе бпока управпения 5 вырабатывается сигнап на втором выходе этогоже бпока управпения, обеспечивающийдесятичное сйожение содержимого сумматора 2 с кодом блока 3, Еспи сигнална входе бпока управпения отсутствуетмпадший разряд мпадшей тетрады регистра множителя имеет нулевое значение), то сигнап на втором выходе блокауправпения не появпяется. С задержкойна время передачи кода из блока 3 вблок 2 относитепьно момента, в которыйформируется сигнап на втором выходеблока управпения, этот же блок управления вырабатывает сигналы на своих пер 1 цикп1,такт Бп 2: 0000 ОООО ОООО ООф о р м у и а и з о б р е т е н н я Бп 2 0011 0011 0001 010Здесь принятые обозначения М.р,Бп 115 значение младшего разряда регистра множителя на отдепьных тактах: Бп 2- содержимое сумматора, БпЗ и Бп 4 - соответственно содержимое блока форми- рования множимого - 3 допопнитепьного регистра 4.Ввиду того, что содержимое регистра множнтепя Га отдепьных тактах просто сдвигается на один разряд вправо, как это депается в соответствующем регистре двоичного множитепьного устройства, выполнение умножения дробных чисеп не отпичается от умножения цепых чисеп, что легко можно проверить с помощью примера умножения конкретных чисел Х= . 0,39, У 0,85).На основании описанкя устройства иего работы можно закщочить, что в предпагаемом устройстве достигается поставф ленная цель. Устройство дпя умножения десятичныхчисеп, содержащее регистр множитепя,бпок формирования множимого, сумматор,бпок управления, первый выход которогосоединен со входом управления регистра БпЗ; 1000 0101 0000 0000множитепя, выход которого соединен совходом блока управпения, второй выход которого соединен со входом управлениясумматора, информационные входы которого соединены с информационными выходами бпока формирования множимого,первый и второй входы управпения котогрого соединены соответственно с третьими четвертым выходами блока управ:"с цепью расширення обпасти примененияустройства, цутем выполнения операцииумножения над цеными н дробными чиспами, в него введен допоннитепьный регистр,,информационные входы которого соединены с информационними выходами млад,ших тетрад блока формирования множимого, информационные входы старших тетрад которого подкпючены к выходам допопнитепьного регистра, к управпяющемувходу которого подкпючен пятый выходбпока управпения.Источники информации, принятые вовнимание при экспертизе1, Авторское свидетельство СССР652560 Утки ода э 1062/46 Тираж 779 "Под ИНИИПИ Государственного комитета СССРпо дедам изобретений и открытий 113035, Москва, Ж 35, Раушская наб.

СмотретьЗаявка

2344731, 02.04.1976

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ПЕШКОВ АНАТОЛИЙ ТИМОФЕЕВИЧ

МПК / Метки

МПК: G06F 7/39

Метки: десятичных, умножения, чисел

Опубликовано: 15.03.1979

Код ссылки

<a href="https://patents.su/4-652560-ustrojjstvo-dlya-umnozheniya-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения десятичных чисел</a>

Предыдущий патент: Устройство для вычисления суммы п к-разрядных р-ичных чисел

Следующий патент: Накапливающий сумматор с запоминанием переноса

Случайный патент: Шаговый конвейер