Устройство для вычисления быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 467356

Авторы: Гречишников, Степанян, Чалабов

Текст

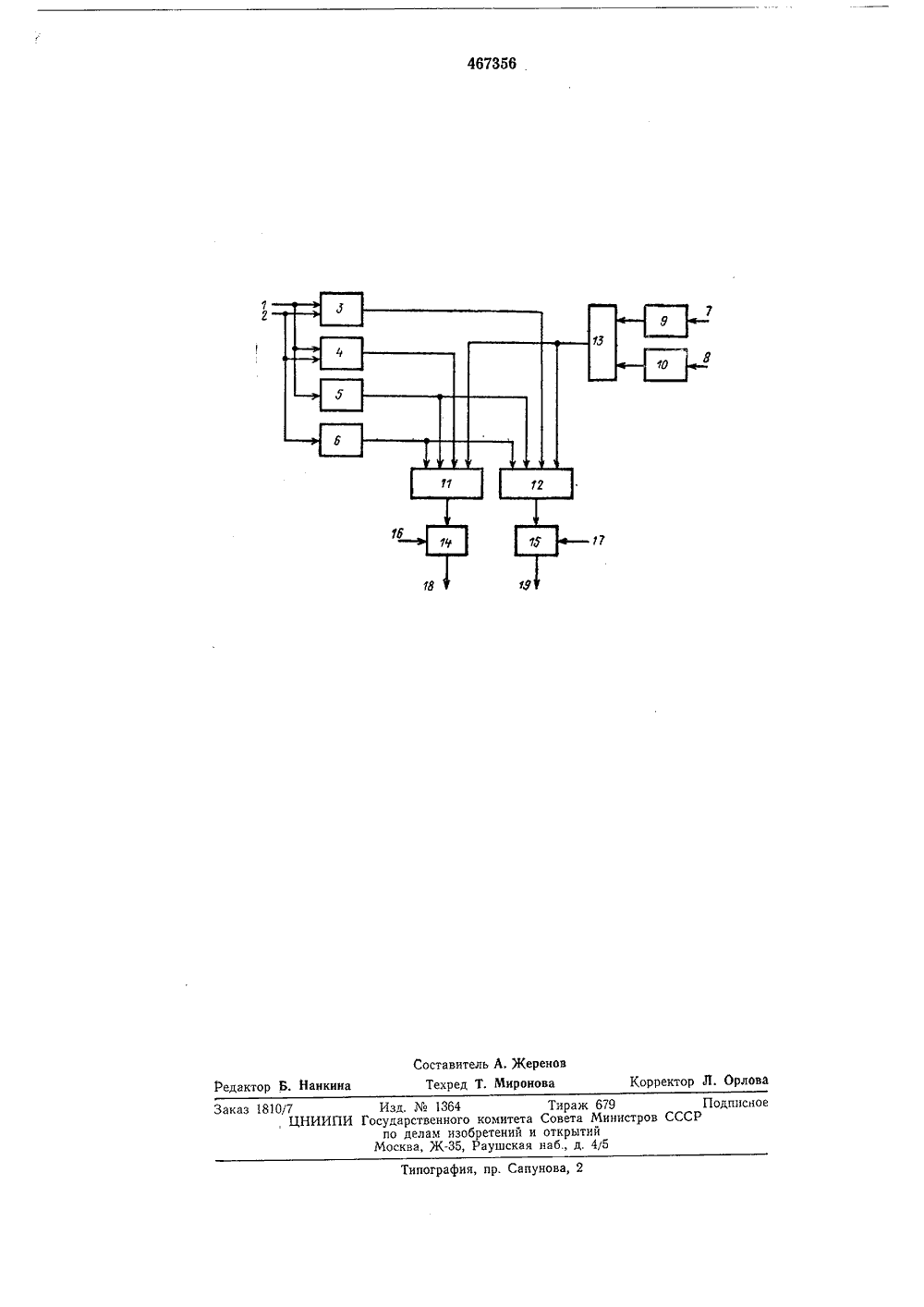

3 Долг од мт 1 е.Ф 1 т ".ь т 6 д ик чеоиуш 1 467356 Союз Советсва Социалистических Республик(51) М. Кл. б 061 15,3 Государственный конитесовета министров ССсроо делам изобретенийи открытий(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕИИЯ БЫСТРО ПРЕОБРАЗОВАНИЯ ФУРЬЕистра 5 иШина 2 одам с" т 4 и региогических огических го логичеИзобретение относится к области вычислительной техники и может быть использовано для расчета в реальном масштабе времени спектральных компонентов сложного многочастотного колебания. 5Известны арифметические устройства для для вычисления быстрого преобразования Фурье (БПФ), содержащие регистры реальной и мнимой частей комплексного весового коэффициента, регистр вещественной части 10 числа, регистр мнимой части числа, первый и второй сумматоры с запоминанием переноса.Известные устройства сложны и обладают недостаточным быстродействием. Эти отрицательные свойства являются следствием того, 15 что суммы поразрядных произведений при перемножении формируются каждый раз заново, что требует соответствующего времени и оборудования.Целью изобретения является повышение 20 быстродействия.Сущность изобретения заключается в том, что устройство содержит два сумматора чисел, входы каждого из которых подключены к первому и второму информационным входам уст ройства, и три логических блока, первые входы первого и второго логических блоков соединены соответственно с выходами первого и второго сумматора чисел, вторые, третьи и четвертые входы подключены соответственно 30 к выходам первого и второго регистров чисел и выходу третьего логического блока, входы которого соединены с выходами регистров реальной и мнимой частей комплексного весового коэффициента, выходы первого и второго логических блоков подключены соответственно ко вторым входам первого и второго сумматоров поразрядных сумм.Блок-схема предлагаемого устройства представлена на чертеже, где приняты следующие обозначения: 1 и 2 - входные числовые шины;3 и 4 - сумматоры чисел; 5 и 6 - регистры чисел; 7 - входная шина реальной части комплексного весового коэффициента; 8 - входцая шина мнимой части комплексного весового коэффициента; 9 - регистр реальной части комплексного весового коэффициента;10 - регистр мнимой части комплексного весового коэффициента; 11, 12, 13 - логические блоки; 14, 15 - сумматоры поразрядных сумм;16, 17 - входные шины чисел; 18, 19 - выходные шины устройства,Шина 1 соединена со входом рег первыми входами сумматоров 3, 4 подключена ко входу регистра 6 и вх маторов 3, 4, Выходы сумматоров 3 стров 5, 6 связаны со входами л блоков 11 и 12. Со входами этих л блоков соединен также выход третьеского блока 13, первый вход которого соединен с выходом регистра 9, а второй - регистра 10. Выход первого логического блока 11 подключен к первому входу сумматора 14, ко второму входу которого подведена шина 16, а выход сумматора 14 является выходом устройства. Связи блока 12 и сумматора 15 полностью аналогичны связям между блоком 11 и сумматором 14. В схемы логических блоков (11, 12) включены устройства перевода кода слагаемых в дополнительный код в соответствии с алгоритмом работы арифметического устройства, приведенным ниже,Устройство работает по алгоритму:Ас, ) = Ас+ Ас (КЬ Ч (1) Ас+с (К) -= Ас (у) - Ас(К) Ю=2 Ас Ц) - Ас+с(/), (11) где А с индексами - комплексные числа; Ф - комплексный весовой коэффициент.Кроме того, для перемножения двух комплексных чисел необходимо выполнить четыре операции умножения вещественных чисел, одно сложение и одно вычитание.Операнды подаются из запоминающего блока в регистры 5, 6 и сумматоры 3, 4. В сумматоре 3 образуется сумма операндов, а в сумматоре 4 - их разность. В регистры 9 и 10 по шинами 8 засылаются значения вещественной и мнимой частей К соответственно. Далее рассматривается работа логического блока 11 и сумматора 14 совместно с сумматорами 3, 4, регистрами 5, 6, 9, 10 и логическим блоком 13, так как работа остальной части устройства происходит аналогично. Ниже приводится пример вычисления суммы двух произведений. ЙеАс(К) = 1,01011 1 тАс(К) = - 0,01101 Яе Ч 7 = 0,10011 ЬиФ = 0,01010 01011 00000 1,10101 01011 01101 0,00010 00000 00000 0,00000 00000 01101 0,01101 01011 00000 1,10101Ле и 1 т - вещественные и мнимые части соответственно.Суммы поразрядных произведений, соответствующие строчке третьего столбца приведенного примера, в известных устройствах каждый раз образуются заново. Однако строка в третьем столбце может принимать толь 5101520 25 30 35 40 45 50 4ко следующие значения: 1,10101; 0,0010;0,0000; 0,01101; т, е, КеА;(К), КеА;(К)+1 сп Асф), О, 1 спА;(К). Эти значения легко сформировать заранее, при приеме информации из блока памяти и затем только подавать их в соответствующий сумматор.Логический блок 13 производит слежение за очередными разрядами многочислителей, находящихся в регистрах 9 и 10, и в соответствии с этим управляет работой логических блоков 11, 12. Работа этих блоков состоит в подаче сформированных ранее и хранящихся в сумматорах 3, 4 и регистрах 5, 6 поразрядных сумм. Окончательное значение рассчитываемых коэффициентов образуется в сумматорах 14, 15 после подачи туда числа в соответствии с формулами (1) и (11),Информация из сумматоров 14, 15 выводится по шинам 18, 19. На этом цикл обработки заканчивается,Предмет изобретения Устройство для вычисления быстрого преобразования Фурье, содержащее регистры реальной и мнимой частей комплексного весового коэффициента, входы которых соединены с соответствующими входами устройства, два регистра чисел, входы которых подключены соответственно к первому и второму информационным входам устройства, два сумматора поразрядных сумм, первые входы которых соединены соответственно с третьим и четвертым информационными входами устройства, выходы подключены соответственно к первому и второму выходам устройства, отл и ч а ю щ ее с я тем, что, с целью повышения быстродействия, оно содержит два сумматора чисел, входы каждого из которых подключены к первому и второму информационным входам устройства, и три логических блока, первые входы первого и второго логических блоков соединены соответственно с выходами первого и второго сумматоров чисел, вторые, третьи и четвертые входы подключены соответственно к выходам первого и второго регистров чисел и выходу третьего логического блока, входы которого соединены с выходами регистров реальной и мнимой частей комплексного весового коэффициента, выходы первого и второго логических блоков подключены соответственно ко вторым входам первого и второго сумматоров поразрядных сумм.467356 Тираж 679 итета Совета Министров СС ний и открытий шская наб., д. 45Изд. Мо 1364 ИИПИ Государственного ко по делам изобре Москва, Ж, Раудписн Заказ 1810/ Типография, пр. Сапунов едактор Б. Нанкин ставител Техред Т Жерено иронова рректор Л, Орлов

СмотретьЗаявка

2007367, 25.03.1974

ГРЕЧИШНИКОВ АНАТОЛИЙ ИВАНОВИЧ, СТЕПАНЯН АЛЕКСАНДР КАРОВИЧ, ЧАЛАБОВ ИОСИФ ГАВРИИЛОВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: быстрого, вычисления, преобразования, фурье

Опубликовано: 15.04.1975

Код ссылки

<a href="https://patents.su/3-467356-ustrojjstvo-dlya-vychisleniya-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления быстрого преобразования фурье</a>

Предыдущий патент: Цифровой коррелометр

Следующий патент: Устройство для прогнозирования времени появления случайных событий

Случайный патент: Ручные механизированные ножницы