Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 451080

Автор: Гуртовцев

Текст

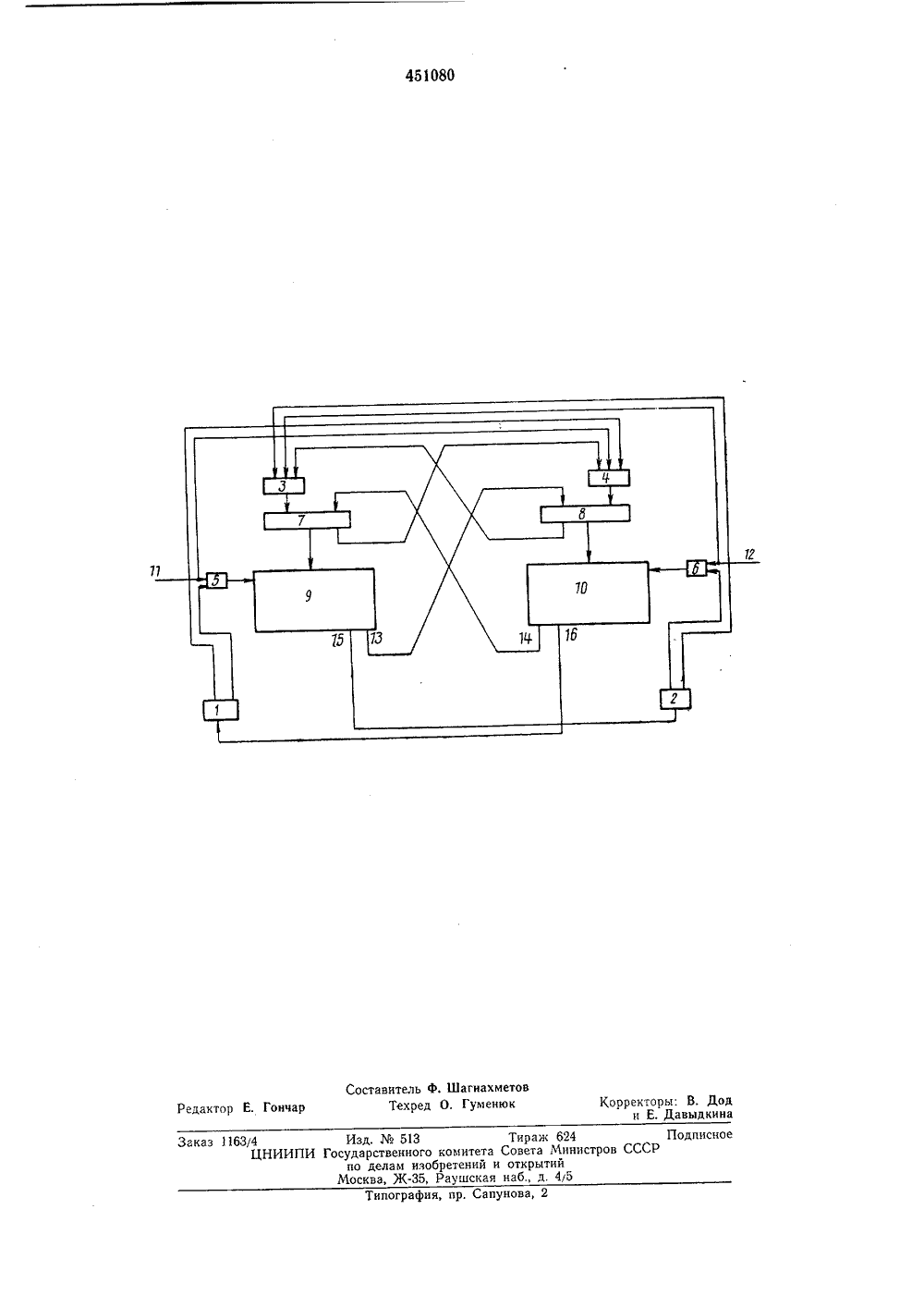

Союз Советских Социалистических Рвсоублнк(51) М, Кл. б 061 9/12 1 осуларственный комитет Совета Министров СССР ло делам изобретенийн открытий(71) Заявитель Институт электроники и вычислительной техники АН Латвийской ССР(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Изобретение относится к вычислительной технике, в частности к устройствам управления цифровых вычислительных машин.Известно микропрограммное устройство управления, содержащее два запоминающих блока, первые входы которых соединены с первыми выходами соответствующих регистров адреса, при этом первый вход одного регистра адреса соединен с первым выходом другого запоминающего блока. Однако необходимость введения пустых микрокоманд для обеспечения возможности перехода от нечетных микрокоманд к нечетным и от четных к четным микрокомандам увеличивает затраты оборудования,Цель изобретения - упрощение устройства. Для осуществления этой цели предлагаемое устройство содержит две схемы И, два триггера, два коммутатора, причем выход каждого коммутатора соединен с вторым входом соответствующего регистра адреса, выход каждой схемы И соединен с вторым входом соответствующего запоминающего блока, вторые входы запоминающих блоков соединены со счетными входами соответствующих триггеров, единичный выход одного триггера соединен с первым входом другой схемы И, второй вход одной схемы И соединен с первым входом другого коммутатора и с соответствующим входом устройства, второй вход каждого коммутатора соединен с нулевым выходом соответствующего триггера, а третий вход одного коммутатора соединен с вторым выходом другого регистра адреса.5 На чертеже приведена блок-схема устройства.Микропрограммное устройство управлениясодержит триггеры 1 и 2, коммутаторы 3 и 4, схемы И 5 и 6, регистры адреса 7 и 8, запо минающие блоки 9 и 10. Входы устройства 11и 12 и первые выходы 13 и 14 и вторые выходы 15 и 16 запоминающих блоков.Устройство работает следующим образом.Пусть в исходном состоянии триггеры 1 и 2 15 находятся в единичном состоянии и пусть нарегистре адреса 7 (8) находится адрес микро- команды, подлежащей считыванию. Так как триггер 1 (2) находится в единичном состоянии, то он разрешает прохождение поступив шего на вход 11 (12) тактового импульса через схему И 5 (6) и запрещает передачу содержимого регистра адреса 7 (8) через коммутатор 4 (3) на регистр адреса 8 (7). С приходом на вход схемы И 5 (6) первого такто вого импульса на выходе запоминающего блока 9 (10) через некоторое время появится считанная микрокоманда. В том случае, когда отсутствует необходимость перехода от нечетной (четной) микрокоманды к нечетной (четной) 30 микрокоманде, со второго выхода 15 (16) запоминающего блока 9 (10) считывается каждый раз нулевой сигнал, который не производит никаких изменений в состоянии триггеров 1 и 2. При этом разблокированы схемы И 5 и 6, но заблокированы коммутаторы 3 и 4, Устройство в этом случае работает аналогично известному. При необходимости перехода от нечетной (четной) микрокоманды к нечетной (четной) на втором выходе 15 (16) запоминающего блока 9 (10) в считываемой микрокоманде в дополнительном разряде записывается единица, которая устанавливает триггер 2 (1) в противоположное состояние, т. е. в нулевое, При этом триггер 2 (1) блокирует прохождение тактового импульса через схему И 6 (5) и разблокирует коммутатор 3 (4), При этом адрес следующей микрокоманды, занесенный адресной частью считанной микро- команды на регистр адреса 8 (7) первым тактовым импульсом, перезаписывается через коммутатор 3 (4) на регистр адреса 7 (8). Таким образом, к приходу второго тактового импульса на схему И 5 (6) на регистре адреса 7 (8) уже установлен адрес считываемой микрокоманды. Если после этой считЫваемой микрокоманды необходимо вновь перейти к четной (нечетной) микрокоманде, то в считываемой микрокоманде появится сигнал, который по второму выходу 15 (16) запоминающего блока 9 (10) установит триггер 2 (1) в противоположное, т. е. в единичное состояние. Далее процесс повторяется аналогично описанному,5 Предмет изобретенияМикропрограммное устройство управления,содержащее два запоминающих блока, первые входы которых соединены с первыми вы ходами соответствующих регистров адреса, апервый вход одного регистра адреса соединен с первым выходом другого запоминающего блока, отличающееся тем, что, с целью упрощения устройства, оно содержит две схе мы И, два триггера, два коммутатора, при.чем выход каждого коммутатора соединен с вторым входом соответствующего регистра адреса, выход каждой схемы И соединен с вторым входом соответствующего запоминающе го блока, вторые выходы запоминающих блоков соединены со счетными входами соответствующих триггеров, единичный выход одного триггера соединен с первым входом другой схемы И, второй вход одной схемы И соеди нен с первым входом другого коммутатора исоответствующим входом устройства, второй вход каждого коммутатора соединен с нулевым выходом соответствующего триггера, а третий вход одного коммутатора соединен с ЗО вторым выходом другого регистра адреса.Составитель ф. Шагиахметов Редактор Е. Гончар Техред О. Гуменюк Корректоры: В, Дод и Е. Давыдкина Заказ 1163/4 Изд.513 Тираж 624 Подписное ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий Москва, Ж, Раушская наб., д. 45 Типография, пр, Сапунова, 2

СмотретьЗаявка

1860814, 15.12.1972

ИНСТИТУТ ЭЛЕКТРОНИКИ И ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ АН ЛАТВ. ССР

ГУРТОВЦЕВ АРКАДИЙ ЛАЗАРЕВИЧ

МПК / Метки

МПК: G06F 9/12

Метки: микропрограммное

Опубликовано: 25.11.1974

Код ссылки

<a href="https://patents.su/3-451080-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Множительное устройство последовательного действия

Следующий патент: Устройство для контроля аппаратуры обработки данных

Случайный патент: Способ выделения тетрахлордипропиловых эфиров из органической фазы хлоргидрината