Программируемый контроллер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1780086

Автор: Сендульский

Текст

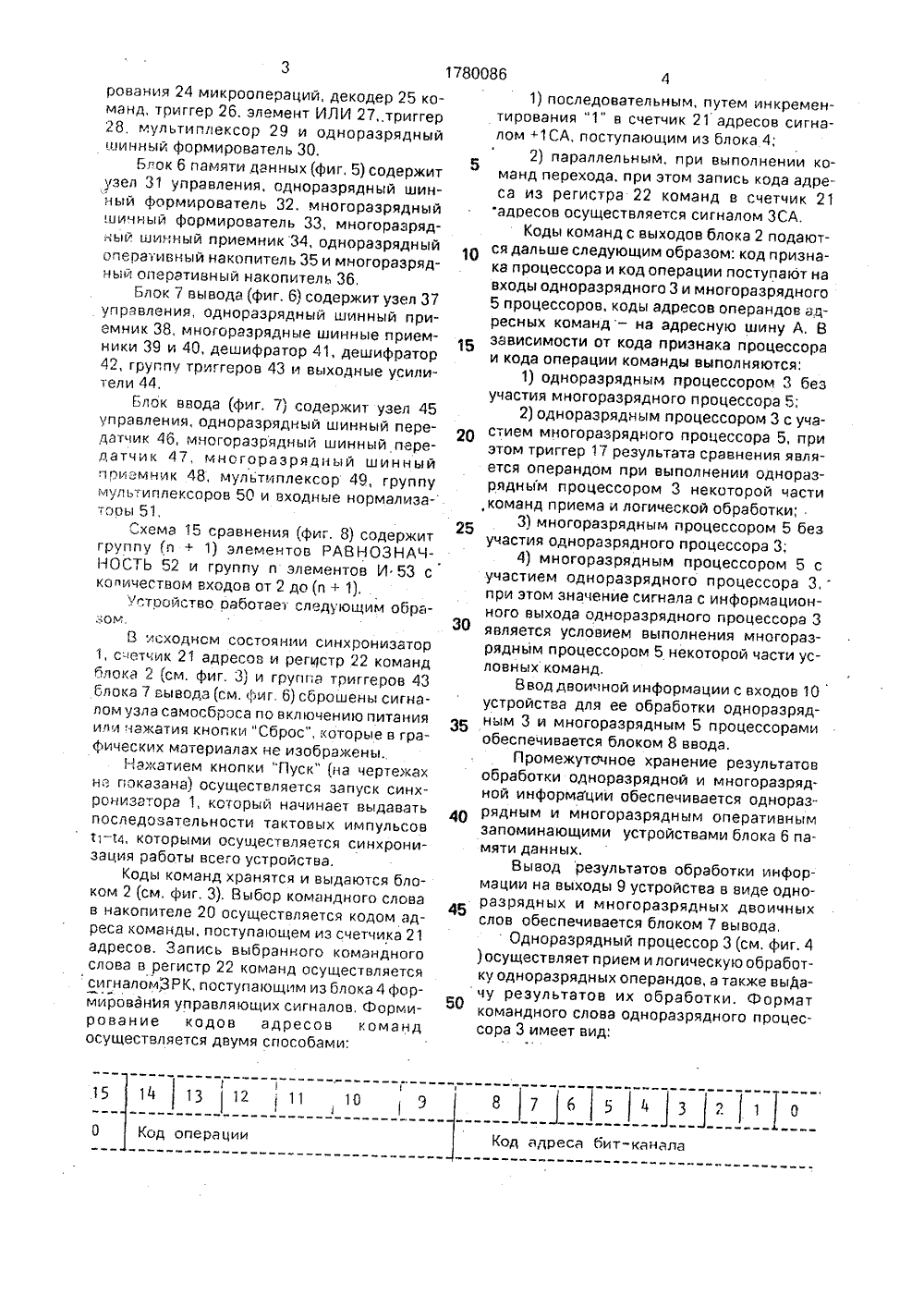

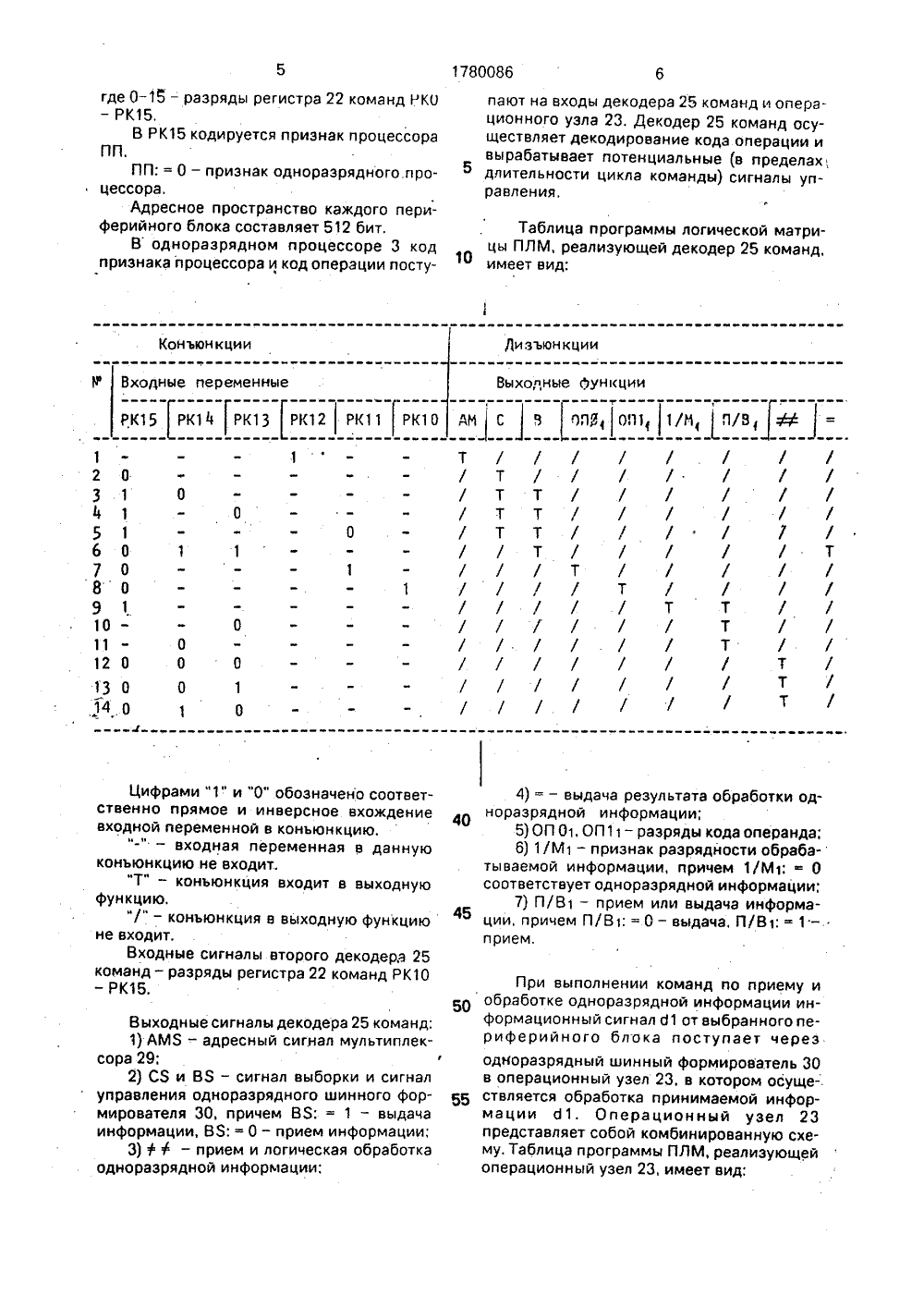

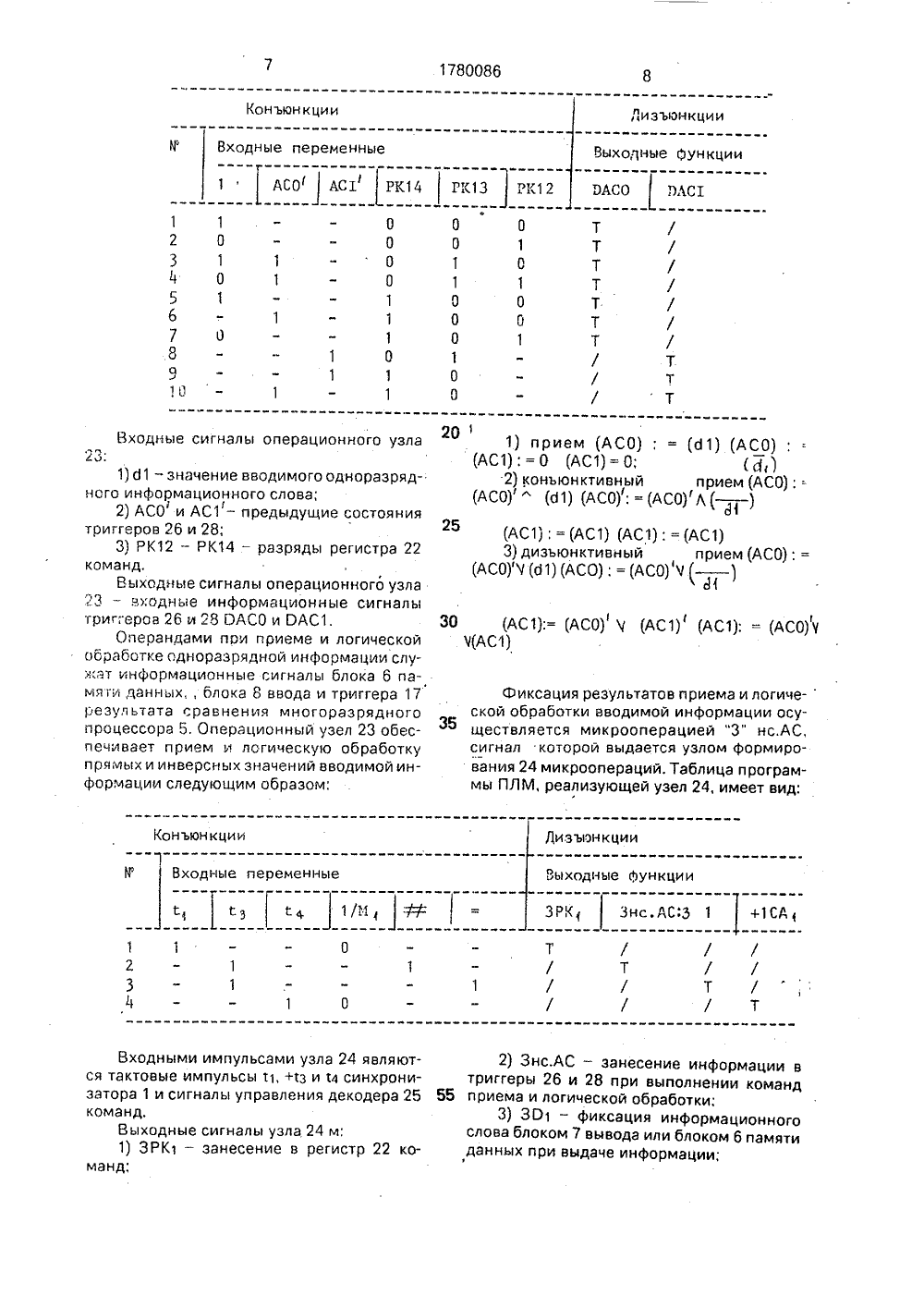

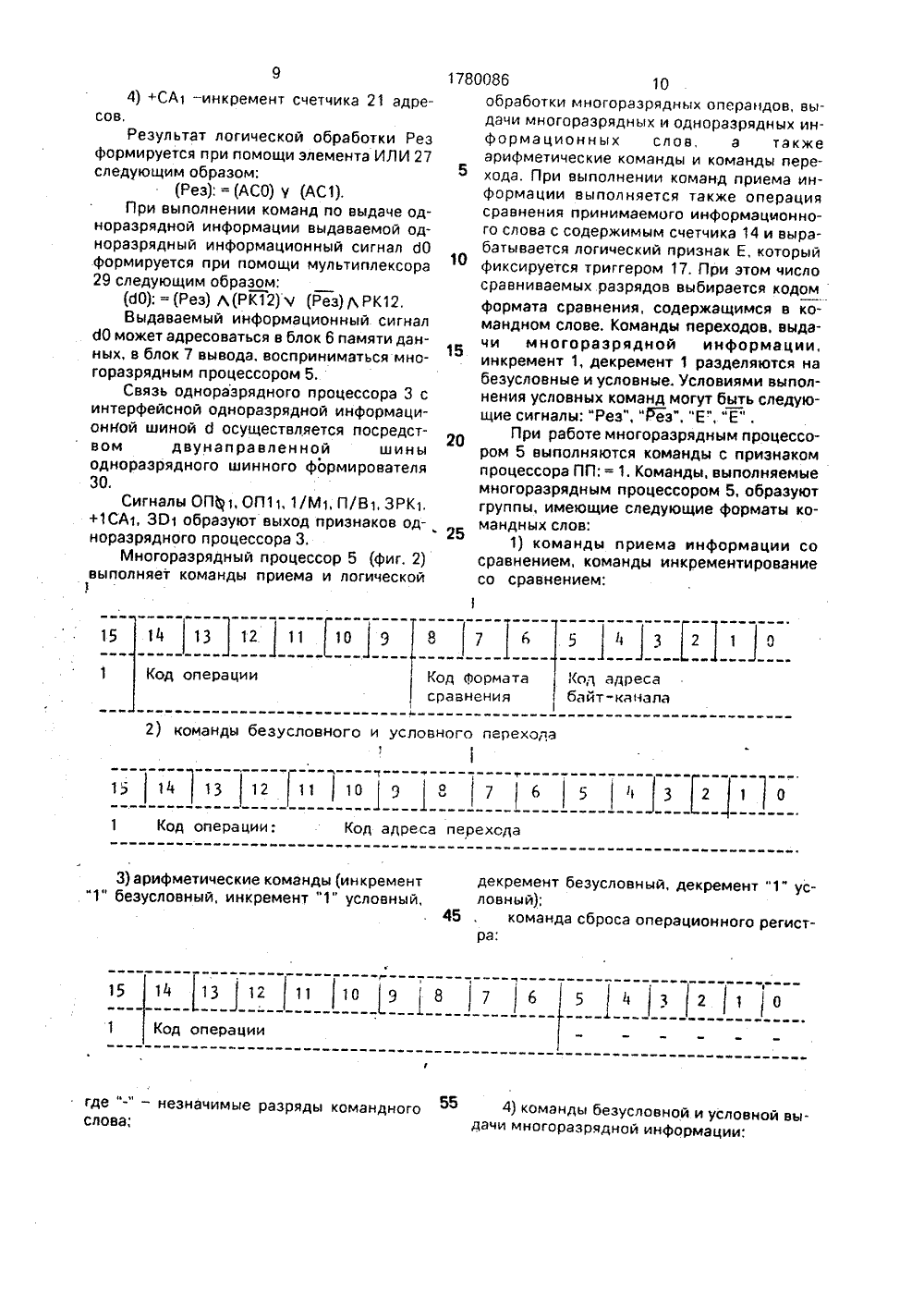

06 3 СО ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(57) Изобретение относится к автоматике ивычислительной технике и может быть использовано для программной реализациибыстродействующих дискретных устройств Изобретение относится к автоматике и вычислительной технике и может быть использовано для программной реализации быстродействующих дискретных устройств управления технологическим оборудованием, в частности в системах дозирования, управления испытательным оборудованием. в технике научного эксперимента, а также для управления автоматическими линиями и робототехнологическими комплексами и т,п,Цель изобретения - повышение производительности.На фиг. 1 изображена структурная схема контроллера; на фиг. 2 - структурная схема многоразрядного процессора; на фиг.3 - структурная схема блока программного управления; на фиг. 4 - структурная схема одноразрядного процессора; на фиг. 5 - функциональная схема блока памяти данных; на фиг, 6 - функциональная схема блока вывода; на фиг. 7 - функциональная схема блока ввода; на фиг. 8 - функциональная схема узла сравнения; на Фиг. 9 - вреуправления технологическим оборудованием, в частности в системах доэирования, управления испытательным оборудованием, в технике научного эксперимента. а также для управления автоматическими линиями и робототехнологическими комплексами и т.п. Цель изобретения - увеличение производительности. Контроллер содержит синхронизатор, блок программного управления, одноразрядный процессор, блок формирования урравляющих сигналов управления, многоразрядный про-, цессор, блок памяти данных, блок вывода, блок ввода, выходы и входы устройства. 11 менные диаграммы сигналов ороопераций устройства; на фима команд одноразрядного прфиг, 11 - система команд мно р р д процессора,Программируемый контроллер содержит синхронизатор 1, блок 2 программного управления, одноразрядный процессор 3, блок 4 формирования управляющих сигналов, многоразрядный процессор 5, блок 6 памяти данных, блок 7 вывода, блок 8 ввода, выходы 9 и входы 10 устройства.Многоразрядный процессор 5 содержит декодер 11 команд, мультиплексор 12, узел формирования 13 микроопераций, счетчик 14, узел 15 сравнения, одноразрядный (первый) шинный формирователь 16, триггер 17, мультиплексор 18 и многоразрядный (второй) шинный формирователь 19.Блок 2 программного управления (фиг, 3) содержит накопитель 20. счетчик 21 адресов и регистр 22 команд.Одноразрядный процессор 3 (фиг. 4) содержит операционный узел 23, узел форми 19 1780086информационной шине д и логическая обработка одноразрядным процессором 3 сигнала состояния триггера 17 результатасравнения "Е",При выполнении многоразряднымпроцессором 5 соответствующей части условных команд сигнал, определяющий ихвыполнение, поступает по одноразряднойинформационной шине б из одноразрядного процессора 3 в виде сигнала "Рез" - результата логической обработки,предварительно произведенной одноразрядным процессором 3,Временные диаграммы формированияосновных микроопераций представлены нафиг, 6: при выполнении команд по приему илогической обработке информации Ц 1;арифметических команд и команды сбросасчетчика Ц 2; команд по выдаче информацииЦЗ; команд перехода Ц 4,Приведенные выше программы ПЛШ,реализующие декодер 25 команд, операционный узел 23, узел 24, декодер 11 команд,узел 13, соответствуют представленным нафиг, 10 и 11 системам команд одноразрядного 3 и многоразрядного 5 процессоров. При описании примера конкретноговыполнения заявленного устройства и вграфических материалах приняты следующие обозначения и индексы:и - разрядность многоразрядного процессора 5;в- разрядность кода адреса одноразрядного операнда;- разрядность кода адреса и-разрядного операнда;и - разрядность кода адреса бита в лраэрядном слове, причеми+ 1 =о 92(и+ 1); ги.=1+ и+ 1;3+ 1 - количество адресуемых одноразрядных каналов ввода, вывода, одноразрядных ячеек блока памяти данных,причем Я + 1 = 2;г+ 1 - количество адресуемых и-разрядных каналов ввода, вывода и-раэрядныхячеек блока памяти данных,причем (г+1) =2(3 + 1) = (и + 1) (г + 1),Формула изобретения 1. Программируемый контроллер. содержащий синхронизатор, блок программного управления, блок формирования управляющих сигналов, одноразрядный и многоразрядный процессоры, блок памяти данных, блок вывода и блок ввода, причем выход синхронизатора соединен с тактовыми входами одноразрядного и многоразрядного процессоров, входы кода команды 5 10 15 20 30 35 40 50 55 которых соединены с выходом блока программного управления и с адресными входами блока памяти данных, блока ввода и блока вывода, первый информационный вход-выход блока памяти данных, первый информационный вход блока вывода и первый информационный вход блока ввода обьединены и соединены с первым информационным входом-выходом многоразрядного процессора, выходы признаков одноразрядного и многоразрядного процессоров соединены соответственно с пеовым и вторым информационными входами блока формирования управляющих сигналов, первый выход которого соединен с входом синхронизации блока программного управления, второй выход блока формирования управляющих сигналов соединен с входом управления записью-чтением блока памяти данных, входом управления выдачей блока вывода и входом управления приемом блока ввода, инормационный выход блока вывода и информационный вход блока ввода являются соответственно выходом и входом данных программируемого контроллера, отл и ча ю щеес ятем, что, с целью повышения производительности, второй информационный вход-выход многоразрядного процессора соединен с информационным входом-выходом одноразрядного процессора, с вторым информационным входом-выходом блока памяти данных, с вторым информационным входом блока вывода и с вторым информационным выходом блока ввода, причем многоразрядный процессор содержит декодер команд, узел формирования микроопераций, первый и второй шинные формирователи, триггер, первый и второй мультиплексоры, счетчик и узел сравнения, причем тактовый вход многоразрядного процессора соединен со стробирующим входом узла формирования микроопераций, первый и второй выходы которого соединены соответственно с синхровходом триггера и с входом занесения счетчика, третий выход счетчика объединен с выходом декодера команд и соединен с выходом признаков многоразрядного процессора, первый и второй информационные входы-выходы которого соединены соответственно с входами-выходами первого и второго шинных формирователей, управляющие входы которых соединены с входом кода операции узла формирования микроопераций и с выходом декодера команд, информационный вход которого соединен с входом кода команды многоразрядного процессора и с управляющими входами первого и второго мультиплексоров, выход первого шинногоформирователя соединен с информационным входом счетчика и с первым информационным входом узла сравнения, второй информационный вход которого соединен с выходом счетчика и информационным входом первого шинного формирователя, выходы узла сравнения соединены с информационными входами первого мультиплексора, выход которого соединен с информационным входом триггера, выход которого соединен с информационным входом второго шинного формирователя и с первым информационным входом второго мультиплексора, второй информационный вход и выход которого соединены соответственно с выходом второго шинного формирователя и с входом условия узла формирования микроопераций,2, Контроллер по и. 1, о т л и ч а ю щ и йс я тем, что выходы узла формирования микроопераций с четвертого по шестой соединены соответственно с входом прибавления единицы. с входом вычитания единицы и с входом установки в "0" счетчика,178008 о Обб Ю Е А ЛРФ Ад ЮУР 1 А ВУб А ЗРРЖг аД /TПУ Редактор Корректор У. Демчик1,.р,:,н Техред Заказ 4437 Тираж ПодписноеВНИИПИ Государственного комитета оо изобретениям и открытиям при ГКНТ СССР113035, москва, Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 Юююаюд кааыЬ Я ЛаУЯсРЩБФ1780086 20м ее1 Ц ( 13 ) 1211 10Э 8 ) 76 5 (321 О Код адреса бит-канала Код операции рования 24 микроопераций, декодер 25 команд, триггер 26, элемент ИЛИ 27 триггер 28, мультиплексор 29 и одноразрядный шинный формирователь 30.Блок 6 памяти данных (фиг, 5) содержит узел 31 управления, одноразрядный шинный формирователь 32, многоразрядный шинный формирователь 33, многоразрядный шинный приемник 34, одноразрядный оперативный накопитель 35 и многоразрядный оперативный накопитель 36,Блок 7 вывода (фиг. 6) содержит узел 37 управления, одноразрядный шинный приемник 38, многоразрядные шинные приемники 39 и 40, дешифратор 41, дешифратор 42, группу триггеров 43 и выходные усилители 44,Блок ввода (фиг. 7) содержит узел 45 управления, одноразрядный шинный передатчик 46, многоразрядный шинный передатчик 47, мнсгоразрядный шинный приемник 48, мультиплексор 49, группу мультиплексоров 50 и входные нормализатооы 51,Схема 15 сравнения (фиг. 8) содержит группу (и + 1) элементов РАВ Н ОЗ НАЧНОСТЬ 52 и группу и элементов И 53 с количеством входов от 2 до (и + 1),Устоойство работает следующим образом.В исходном состоянии синхронизатор 1, счетчик 21 адресов и регистр 22 команд блока 2 (см, фиг. 3) и группа триггеров 43 блока 7 вывода (см. фиг, 6) сброшены сигналом узла самосброса по включению питания или нажатия кнопки "Сброс", которые в графических материалах не изображены,Нажатием кнопки "Пуск" (на чертежах не показана) осуществляется запуск синхронизатора 1, который начинает выдавать последовательности тактовых импульсов т 1-14, которыми осуществляется синхронизация работы всего устройства.Коды команд хранятся и выдаются блоком 2 (см, фиг. 3). Выбор командного слова в накопителе 20 осуществляется кодом адреса команды, поступающем из счетчика 21 адресов, Запись выбранного командного слова в регистр 22 команд осуществляется сигналомДРК, поступающим из блока 4 формирования управляющих сигналов, Формирование кодов адресов команд осуществляется двумя способами: 1) последовательным, путем инкрементирования "1" в счетчик 21 адресов сигналом +1 СА, поступающим из блока 4;2) параллельным, при выполнении команд перехода, при этом запись кода адреса из регистра 22 команд в счетчик 21 адресов осуществляется сигналом ЗСА,Коды команд с выходов блока 2 подаются дальше следующим образом: код признэка процессора и код операции поступают на входы одноразрядного 3 и многоразрядного 5 процессоров, коды адресов операндов эдресных команд - на адресную шину А, В зависимости от кода признаа процессораи кода операции команды выполняются:1) одноразрядным процессором 3 безучастия многоразрядного процессора 5; 2) одноразрядным процессором 3 с учас",ием многоразрядного процессора 5, при этом триггер 17 результата сравнения является операндом при выполнении одноразрядным процессором 3 некоторой части,команд приема и логической обработки; .3) многоразрядным процессором 5 безучастия одноразрядного процессора 3;4) многоразрядным процессором 5 сучастием одноразрядного процессора 3,при этом значение сигнала с информационного выхода одноразрядного процессора 330 является условием выполнения многоразрядным процессором 5 некоторой части условных команд.Ввод двоичной информации с входов 10устройства для ее обработки одноразрядным 3 и многоразрядным 5 процессорамиобеспечивается блоком 8 ввода.Промежуточное хранение результатовобработки одноразрядной и многоразрядной информации обеспечивается одноразрядным и многоразрядным оперативнымзапоминающими устройствами блока 6 памяти данных,Вывод результатов обработки информации на выходы 9 устройства в виде одноразрядных и многоразрядных двоичныхслов обеспечивается блоком 7 вывода,Одноразрядный процессор 3 (см. фиг. 4) осуществляет прием и логическую обработку одноразрядных операндов, а также выдачу результатов их обработки, Форматкомандного слова одноразрядного процессора 3 имеет вид;1780086 где 0-15 - разряды регистра 22 команд РКО - РК 15,В РК 15 кодируется признак процессора ПП.ПП: = 0 - признак одноразрядного.процессора,Адресное п 5 ост 5 анствр каждого периферийного блока составляет 512 бит.В одноразрядном процессоре 3 код признака процессора и код операции поступают на входы декодера 25 команд и операционного узла 23. Декодер 25 команд осуществляет декодирование кода операции и вырабатывает потенциальные (в пределах, длительности цикла команды) сигналы управления,Таблица программы логической мат 5 ицы ПЛМ, реализующей декодер 25 команд, имеет вид: 10 Конъюн кции Диэъюнкции Входные переменныеГ Выходные йункциит1С В Ю 8, ОП 1, 1/И, П/В,РК 15 РК 14 РК 13 РК 12 РК 11 РК 10 0 0 1 О Цифрами "1" и "0" обозначено соответственно прямое и инверсное вхождение входной переменной в конъюнкцию.40"-" - входная переменная в данную конъюнкцию не входит."/" - конъюнкция в выходную функцию не входит.Входные сигналы второго декодерэ 25 команд - разряды регистра 22 команд РК 10 - РК 15,4) = - выдача результата обработки одноразрядной информации;5) ОП 01, ОП 11 - раз 5 яды кода операнда; б) 1/М 1 - признак разрядности обрабатываемой информации, причем 1/М 1: " О соответствует одноразрядной информации;7) П/В 1 - прием или выдача инфо 5 мации, причем П/В 1: = 0 - выдача, П/В 1: = 1 - прием. При выполнении команд по приему и обработке одноразрядной информации информационный сигнал б 1 от выбранного периферийного блока поступает через одноразрядный щинный формирователь 30 в операционный узел 23, в котором осуще-. ствляется обработка принимаемой информации б 1, Операционный узел 23 представляет собой комбинированную схему, Таблица программы ПЛМ, реализующей операционный узел 23, имеет вид: 50 Выходные сигналы декодера 25 команд: 1) АМЗ - адресный сигнал мультиплексора 29;2) СЗ и ВЗ - сигнал выборки и сигнал управления одноразрядного щинного фо 5- 55 ми 5 ователя 30, причем ВЗ: = 1 - выдача информации, ВЯ: = 0 - прием информации;3) Ф Ф - прием и логическая обработка одноразрядной информации; 2 О 3 1 4 1 5 1 6 О 7 О 8 О 9 1 10- 11 12 О 13 О 14. О Т ав /1780086 Конъюнкции изъюнкции Входные переменные Выходные функции 1АСО АС 1 РК 14 ЭАСО 1 ЛС 1 Т Т Т Т Т / / / 2 О 11) прием (А СО): = (с 31) (А СО)(АСО)Ч(а) (дСО): =(дСО) (с 11 Входные сигналы операционного узла 23:1) д 1 - значение вводимого одноразрядного информационного слова;2) АСО и АС 1 - предыдущие состояния триггеров 26 и 28;3) РК 12 - РК 14 - разряды регистра 22 команд.Выходные сигналы операционного узла 23 - входные информационные сигналы триггеров 26 и 28 ВАСО и ОАС 1.Опеоандами при приеме и логической осработке одноразрядной информации служат информационные сигналы блока 6 памяти данных блока 8 ввода и триггера 17 результата сравнения многоразрядного процессора 5. Операционный узел 23 обеспечивает прием и логическую обработку прямых и инверсных значений вводимой информации следующим образок ЗО (АС 1):= (дСО)(дс 1) (ДС 1): = (ДСО)Ъ М(АС 1) Фиксация результатов приема и логической обработки вводимой информации осуществляется микрооперацией "3" нс,АС, сигнал которой выдается узлом формирования 24 микроопераций, Таблица и рограммы ПЛМ, реализующей узел 24, имеет вид: Дизъюнкции Конъюн кции Выходные функции Входные переменные/ / / / Т / / Т 1 02 1311 0 2) Знс,АС - занесение информации в триггеры 26 и 28 при выполнении команд 55 приема и логической обработки; 3) 301 - фиксация информационного слова блоком 7 вывода или блоком 6 памяти данных при выдаче информации;Входными импульсами узла 24 являются тактовые импульсы ц 1, +тз и И синхронизатора 1 и сигналы управления декодера 25 команд,Выходные сигналы узла 24 м:1) ЗРК 1 - занесение в регистр 22 команд; 1 12 03 1 14 0 15 16 - 17 0810 1 0 О 0 0 1 1 1 0 1 11 0 0 0 1О 1 1 О 0 0 0 0 1 10а 08 7 Код адресабайт-канала Код операции Код Форматасравнения 2) команды безусловного и условного перехода 1 313 12 11 10 9 Я 7 6 5 1 3 2 1 1 14 о Код операции: Код адреса перехода 3) арифметические команды (инкремент"1" безусловный, инкремент "1" условный,1 ч 13 12 11 1 СЯ у Код операции где "-" - незначимые разряды командного 5 4) команды безусловной и условной вы 55 слова; дачи многоразрядной информации:4) +СА 1 -инкремент счетчика 21 адресов,Результат логической обработки Рез формируется при помощи элемента ИЛИ 27 следующим образом:(Рез); = (АСО) у (АС 1).При выполнении команд по выдаче одноразрядной информации выдаваемой одноразрядный информационный сигнал бО формируется при помощи мультиплексора 29 следующим образом:(оО): =(Реэ) Л(РК 12) ч (Рез) ЛРК 12, Выдаваемый информационный сигнал бО может адресоваться в блок 6 памяти данных, в блок 7 вывода, восприниматься многоразрядным процессором 5.Связь одноразрядного процессора 3 с интерфейсной одноразрядной информационной шиной б осуществляется посредством двунаправленной шины одноразрядного шинного формирователя 30.Сигналы ОПТ 1, ОП 11, 1/М 1, П/В 1, ЗРК 1, +1 СА 1, 301 образуют выход признаков одноразрядного и роцессора 3.Многоразрядный процессор 5 (фиг, 2) выполняет команды приема и логической 1 178008 б 10обработки многоразрядных операндов, выдачи многоразрядных и одноразрядных информационных слов. а также арифметические команды и команды перехода. При выполнении команд приема информации выполняется также операция сравнения принимаемого информационного слова с содержимым счетчика 14 и вырабатывается логический признак Е, который фиксируется триггером 17. При этом число сравниваемых разрядов выбирается кодом формата сравнения, содержащимся в командном слове, Команды переходов, выдачи многоразрядной информации, инкремент 1, декремент 1 разделяются на безусловные и условные. Условиями выполнения условных команд могут быть следующие сигналы: "Реэ", "Реэ". "Е", "Е" .При работе многоразрядным процессором 5 выполняются команды с признаком процессора ПП: = 1. Команды, выполняемые многоразрядным процессором 5, образуют группы, имеющие следующие форматы командных слов:1) команды приема информации сосравнением, команды инкрементирование со сравнением: декремент безусловный, декремент "1" условный);45, команда сброса операционного регистра:11 1780086 12 53 2 1 0 КГзд адресабайт-канала Код операции 5) команды выдачиинформации; одноразрядной 12 1 13 12 11 10 9 Код адреса бит-канала Код операции В многоразрядном процессоре 5 код признака и код операции декодируется декодером 11 команд, который представляет собой комбинационную схему и формирует на своих выходах потенциальные(в течение цикла команды) сигналы управления,Таблица программы ПЛМ, реализующей декодер 11 команд, имеет вид; При зом информационный объем блока ." составляет 2 К(2048) 16-разрядных слов и ограничивается в данном случае разрядностью кода адреса перехода команд перехода. Адресное пространство каждого из периферийных блоков блока 6 памяти данных, блока 7 вывода, блока 8 ввода) составляет 512 бит и(или) 64 байта,Диэъонкции Коиъиг ции Выколные Функции11-"-ъ - - В 51 ИБ ИУ ЛБ 1 ЛУ ЗР ЗЕ СР ПБ ПУОПС,Пи/М /ВВБ ВУ ППОкоцные оорсненныо 1 Рк 01 Рк 9 Рк 5 1 РК МРк 5 1 Рк 2 РК13 1780086 1 изъонкции Конъюнкции Риходние функции/Т / / Т / Т / / / / / / / / / / / / / Р / / / // / 12 - 13 -1367 -вэ1 О1112134 Входные сигналы декодера 11 команд разряды регистра 22 команд РКб- РК 15,Выходные сигналы декодера 11 команд;1) СЯп и ВЯп - сигнал выборки и сигнал управления многоразрядного шинного формирователя 19, причем ВЯп 5: = 1 - выдача информации. ВБ,: = С - прием информации;2) СЯ и ВЬ - сигнал выборки и сигнал управления одноразрядного шинного формирователя 16, причем ВБ: = 1 - выдача информации, ВЯ: = 0 - прием информации;3) ПП - признак процессора;4) ИБ - инкремент безусловный;5) ИУ - инкремент условный;6) ДБ - декремент безусловн ый;7) ДУ - декремент условный;8) ЗР - занесение в счетчик 14;9) ЗЕ - занесение в триггер 27 результата сравнения;10) СР - сброс счетчика 14;11) ПБ - переход безусловный;12) ПУ - переход условный;13) ОП м, ОП 1 м код операнда;14) 1/Мм - признак разрядности обраВходными сигналами узла 13 являются тактовые импульсы т 1-т синхронизатора 1, сигналы управления декодера 11 команд и информационный сигнал условия выполнения условных команд ОУ, который поступает с выхода мультиплексора 12.Выходными сигналами формирователя 13 являются сигналы микроопераций:1) +1 Р - инкремент счетчика 14;2) -1 Р - декремент счетчика 14;3) ЗнсР - параллельное занесение в, счетчик 14;4) ЗнсТЕ - занесение в триггер 17 результата сравнения;,5) Я - сброс счетчика 14;6) ЗРКе - занесение в регистр 22 команд; батываемой инфоРмаЦии, 1/Ми: - : 0 - оДно разрядная информация,.1/М; = 0 многоразрядная информация;15) П/Вм - прием или выдача информации, П/Ве. = 0 - выдача, П/Ве; = 1 - прием;16) ВБ - выдача информации безусловная;17) ВУ - выдача информации условная.10 Узел 15 сравнения (фиг, 8) функционально представляет собой совокупность схем сравнения с разрядностью от и 1 н до (и + 1) и формирует на своих выходах результаты сравнения одно. двух, , и+ 1 (восьми) раз рядов вводимой информации и сигналов свыходов счетчика 14. Выбор результата сравнения осуществляется при помощи мультиплексора 18 кодом формата сравнения.20 Узел формирования 13 микрооперацийпредставляет собой комбинационную схему и выдает импульсные сигналы микроопераций,Таблица программы ПЛМ. реализую щей узел 13. имеет вид: 7) +1 САм - инкремент счетчика 21 адресов;45 8) ЗСАМ - параллельное занесение всчетчик 21 адресов кода адреса перехода;9) 3041 - фиксация информационногослова периферийным блоком при выдачеинформации.50 Команды многоразрядного процессора5 реализуется путем последовательного выполнения микроопераций, инициируемыхсигналами микроопераций:1) команда приема информации со 55 сравнением(РО - Р 7): = (010 - 017);2) команды инкрементирования со срав- нением(Е): = (РО - Р Ф) =- (010 - 01 Ф);3) команда безусловного перехода(САО-СА 11); = (РКО-Р К 11);4) команды условных переходов,РО-Р 7): = (РО-Р 7) - 1, если (0 У): = 1;9) команда сброса счетчика(РО-Р 7), = 0016,10) команды безусловной выдачи многоразрядной информации(000 - 007): = (РО - Р 7);11) команды условной выдачи многоразрядной информации(000-007); = (РО), если (0 У): = 1;12) команда выдачи одноразрядной информацли(О О)=(Е),Принятые при этом обозначения;1) (Е) - содержимое триггера 17 результата сравнения;2) (РО-Р 7) - содержимое счет чика 14;3) (010-017) - принимаемое многоразрядное информационное слово;4) (РО-РФ) и (010-01 Ф - усеченныетрехразрядным кодом формата сравненияинфиомационные слова, Ф (0-7);5) (РО - Р 7) - предыдущее состояниесчетчика 14,б) (САО-СА 11) - содержимое счетчика 21адресов,7) (РКО - РК 11) - код адреса переход какчасть командного слова;8) (0 У) - информационный сигнал условия выполнения условных команд, (0 У)бРез, Рез, Е, Е );9) (000 - 007) - выдаваемое многоразрядное информационное слово;10) (бО) - выдаваемое одноразрядноеинформационное слово,Связь многоразрядного процессора 5 синтерферейной одноразрядной информационной шиной б осуществляется посредством двунаправленной шиныодноразрядного шинного формирователя16, с интерфейсной многоразрядной информационной шиной 0 - посредством двунаправленной шины многоразрядного шинногоформирователя 19.Сигналы ОП 6, ОП 1 м, 1/Мм, П/Вм, ЗРКм,+1 САм ЗСАм 30 м образуют выход признаков многоразрядного процессора 5,16В блоке 4 при использовании сигналовпризнаков одноразрядного 3 и многораз.рядного 5 процессоров вырабатываются общие сигналы управления, а такжеформируется из сигналов узла самосбросаАВ и кнопки СБРОС сигнал установки в ис ходное состояние УО,Первая часть сигналов управления подается в блок 2, вторая часть образует группу интерфейсных сигналов управления С,Логически сигналы управления формируются при помощи восьми элементов ИЛИ иодного повторителя согласно следующимвыражениям:1,1. ЗРК; =ЗРК 1 Ч ЗРКм,1.2, +1 СА 1; =+ 1 САЧ+1 САм,1 3. ЗСА: =-ЗСАм,1,4, УО: = АВЧ СБРОС.2.1. СОП: = ОП 1 ЧОПм2.2. СОП 1: = ОП 1 Ч ОП 1 м,2,3, С 1/М: = 1/М 1 Ч 1/Мм,2,4. СП/В; = П/В 1 УП/Вм,2 5. С 30: 301 У 30 м,Блок б памяти данных (фиг, 5) предназначен для записи, хранения и выдачи одноразрядных и многоразрядных1 информационных слов, Код адреса ячейкипамяти поступает из блока 2 по адреснойшине А через многоразрядный шинный при 30 емник 34 на адресные входы одноразрядного 35 и многоразрядного 36 оперативныхнакопителей, Обмен одноразрядной информацией между одноразрядным оперативным накопителем 35 и одноразряднойинформационной шиной б осуществляетсяпосредством одноразрядного шинного формирователя 32. Обмен многоразрядной информацией между многоразряднымоперативным накопителем Зб и многоразрядной информационной шиной 0 осуществляется посредством многоразрядногошинного формирователя 33. Внутренняя организация работы блока б памяти данныхосуществляется при помощи узла 31 управ 45 ления, который представляет собой комбинационную схему.В узле 31 управления, используя сигналы шины управления С, формируютсяследующие внутриблочные сигналы управления:1) СЗз 2,з 5 = С ОП ф Л соп Л с (/м2) ВЯз 2: = СОПЧЛ СОП 1 Л с/мЛПЯ3) СЯзз,з 6: = СОПфЛ снапЛ С 1/Ал;55 4) ВЯзз: = СОПЕЛЛС 1/МЛСЧ/Ь5) СЯз 4: = СОП фЛ соп)6) О//В 3530: = СОПфЛ С п Асп ЛсЮгде 32-36 - индексы, соответствующие позиционным номерам элементов блока 6 памяти данных,При обращении одноразрядного процессора 3 к блоку 6 памяти данных возможны запись или чтение одноразрядного информационного слова. При обращении многоразрядного процессора 5 к блоку 6 памяти данных возможны запись или чтение многоразрядного информационного слова, а также запись одноразрядного информационного слова.Блок 7 вывода (фиг. 6) предназначен для выдачи на выходы 9 устройства результатов обработки информации одноразрядным 3 и многоразрядным 5 процессорами в виде одноразрядных и многоразрядных слов,Код адреса канала вывода поступает с адресной шины А через многоразрядный шинный приемник 40 следующим образом:1) на входы дешифратора 41, кроме входа с весом 20, поступает код адреса бит-канала;2)на входы дешифратора 42 поступает код адреса байт-канала,Внутренняя организация работы блока 7 вывода осуществляется при помощи узла 37 управлегния, который представляет собой комбинационную схему. В узле 37 управления, используя сигналы шины управления С, формируются следующие внутриблочные сигналы управления:1) СЯзв: = -ЛСОП 1 Л2) СЗЗ 9: = - -- -у Л СОП 1 Л3) СЯ 40 - СОП б Л СОП 4 л С4) СЕ 41 сопФлсоп 1 лс (мл спр лспо5) СЕ 42= Опф ОПаЛС 1/МЛсп ЛСЪ 2, 1780086 5 10 15 20 25 ЗО 35 40 18Блок 8 ввода (фиг, 7) предназначен для обеспечения приема одноразрядным 3 и многоразрядным 5 процессорами выбранных информационных сигналов с входов 10 устройства для их последующей логической обработки,Код адреса канала ввода поступает с адресной шины А через многоразрядный шинный приемник 48 следующим образом:1) на адресные входы мультиплексора 49 поступает код адреса бит-канала в информационном байте;2) на адресные входы группы мультиплексоров 50 поступает код адреса байт-канала,Вся совокупность входных цифровых сигналов с входов 10 устройства через входные нормализаторы 51 поступает на соответствующие информационные входы мультиплексоров группы мультиплексоров 50, благодаря которым на многоразрядную информационную шину О через многоразрядный шинный передатчик 47 мультиплексируется выбранное кодом адреса байт-канала многоразрядное информационное слово. Кроме тога, указанное многоразрядное информационное слово мультиплексируется при помощи мультиплексора 49 в одноразрядный информационный сигнал, который через одноразрядный шинный передатчик 46 поступает на одноразрядную информационную шину б.Внутренняя организация работы блока 8 ввода осуществляется при помощи узла 45 управления, который представляет собой комбинационную схему, В узле 45 управления, используя сигналы шины управления С, формируются следующие внутриблочные сигналы управления:1) СЯ 48 сопф лсОп 1 лсп/с 1 М 2) СЯ 47: - СЛСОП 4 ЛСП 16 Л С 4 3 М3) СЯ 48: = - ЛСОП 4 Л СПЬ СОПШестой сигнал - сигнал й 4 з, формируется схемой самосброса по включению питания, входящей в узел 37 управления;38 - 43 - индексы, соответствующие позиционным номерам элементов блока 7 вывода.При обращении одноразрядного процессора 3 к блоку 7 вывода осуществляется выдача одноразрядного информационного слова.При обращении многоразрядного процессора 5 к блоку 7 вывода возможны выдача одноразрядного или многоразрядного йнформационного слова.где 46 - 48 - индексы, соответствующие позиционным номерам элементов блока 8 ввода.При обращении одноразрядного процессора 3 к блоку 8 ввода осуществляется прием одноразрядного информационного слова. При обращении многоразрядного процессора 5 к блоку 8 ввода 6 существляется прием многоразрядного информационного слова.При обращении одноразрядного процессора 3 к многоразрядному процессору 5 осуществляется прием по одноразрядной

СмотретьЗаявка

4744581, 28.09.1989

ЧЕРНОВИЦКОЕ ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "ЭЛЕКТРОНМАШ"

СЕНДУЛЬСКИЙ НИКОЛАЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 15/80, G06F 9/00

Метки: контроллер, программируемый

Опубликовано: 07.12.1992

Код ссылки

<a href="https://patents.su/19-1780086-programmiruemyjj-kontroller.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый контроллер</a>

Предыдущий патент: Устройство расширения по входу для микрокомпьютера

Следующий патент: Устройство для распределения заданий процессорам

Случайный патент: Соединительная головка для тормозной системы автопоезда