Устройство для отладки программ цифровых процессоров обработки аналоговых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1640696

Авторы: Журавлев, Трахтенберг, Шор

Текст

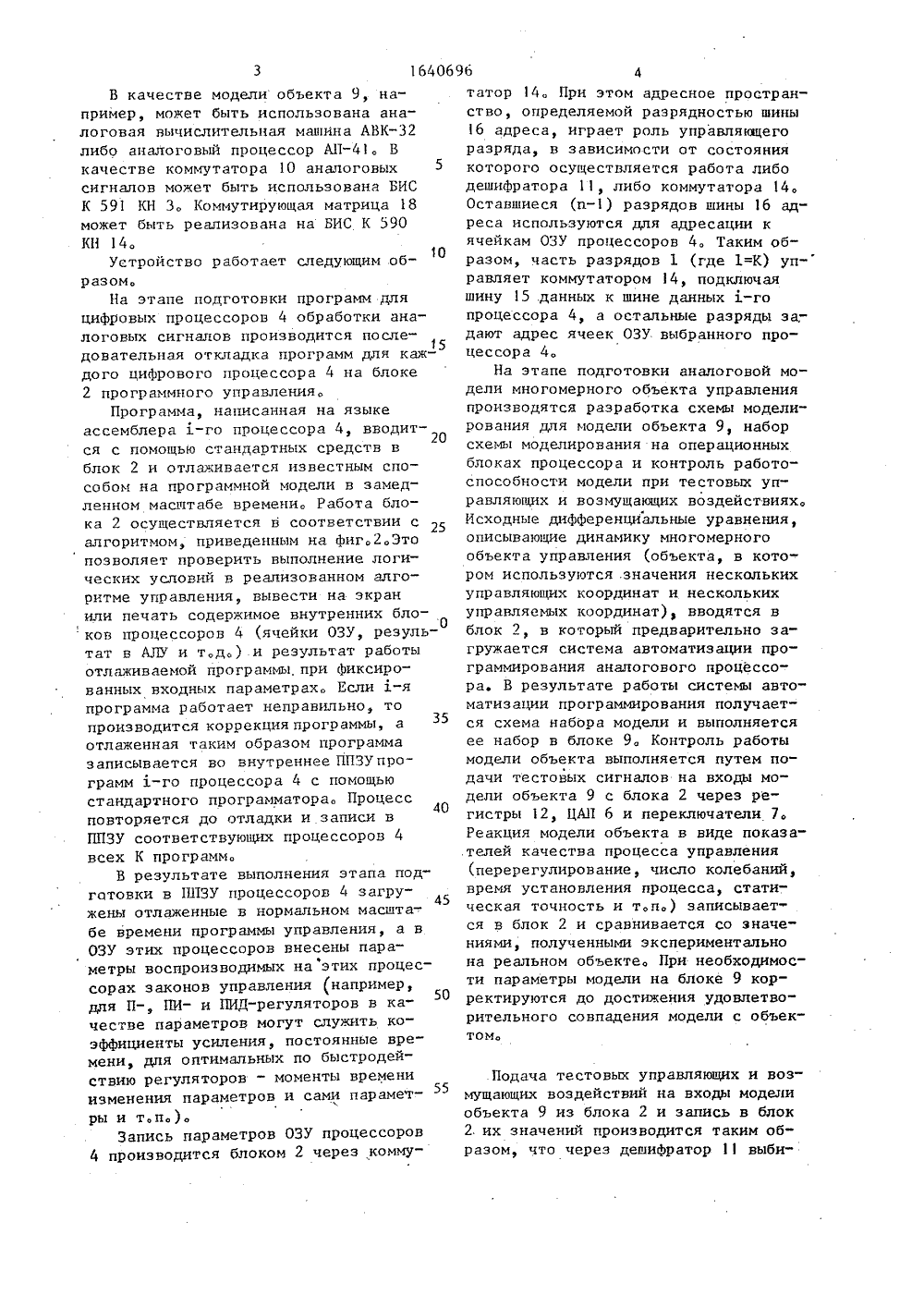

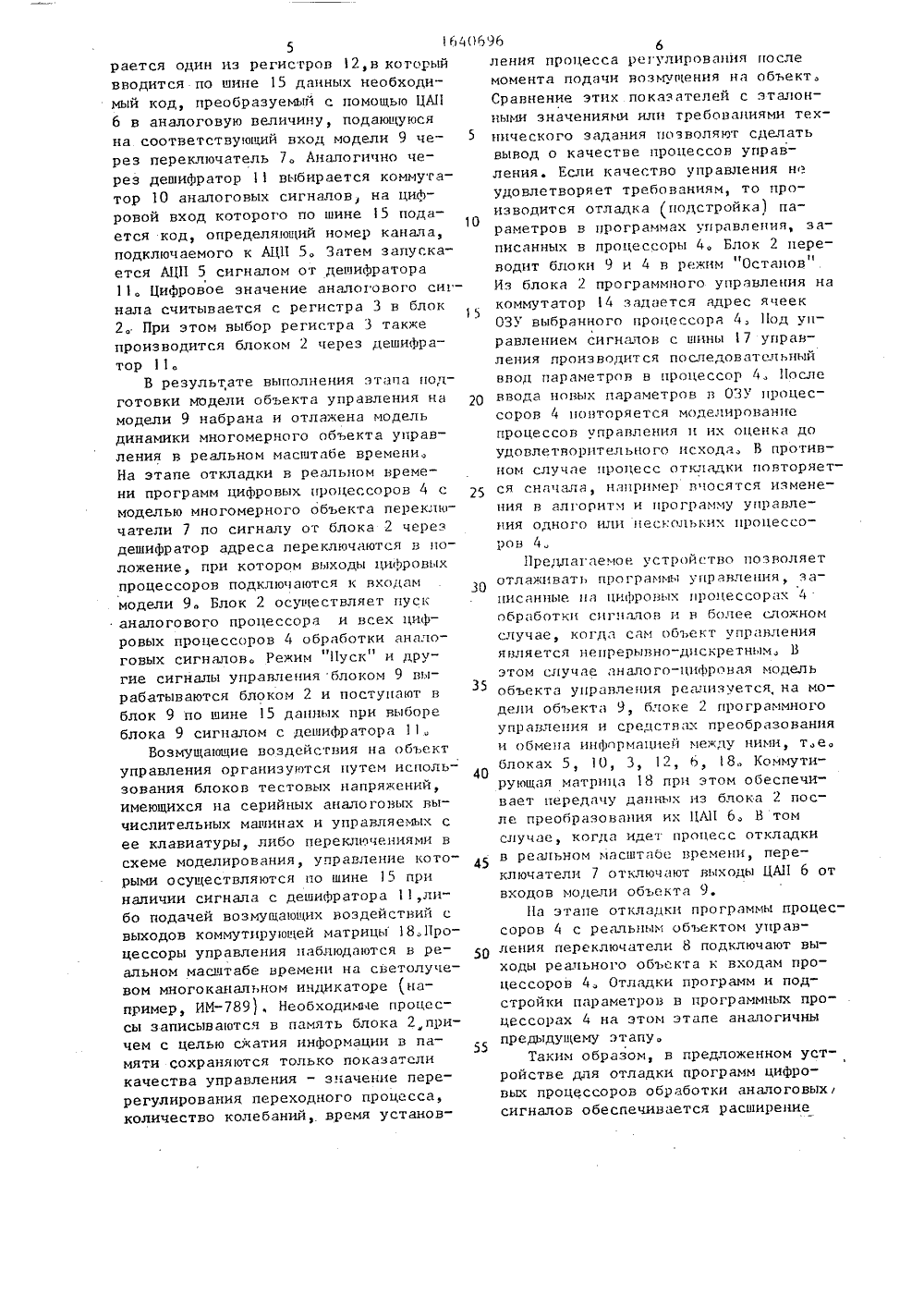

(51 РЕТЕНИ АВТОРСКО ВИДЕТ Т ескои кибернетиахтенберг етельство СССР Р 11/28, 1987. ельство СССРР 11/28, 1987. ЛАДКИ ПРОГРАММ БРАБОТКИ АНисли исполь мас м мно мног о-диасши стен усттладки алесс на блок-схема обр На чертеже из аж устройства.Кроме устройства 1 программ цифровых про ботки аналоговых сиги изображен блок 2 прог отладкиров обрана Аиг.1ого упра аммн ОСУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМРИ ГКНТ СССР ОПИОАНИЕ(71) Отдел знергетики АН МССР(56) Авторское свидУ 1327112, кл. С 06Авторское свидетВ 1339570, кл. С 06 54) УСТРОЙСТВО ДЛЯ ОТЦИФРОВЫХ ПРОЦЕССОРОВ О АОГОВЬИ СИГНАЛОВ57) Изобретение относится к вычисИзобретение относится к вьтельной технике и может бытьзовано для отладки в реальноштабе времени цифровых прогрпроцессорных систем управленимерными непрерывными и непрескретными объектами.Целью изобретения являетсрение функциональных возможнройства за счет обеспеченияв реальном масштабе временилельно работающих цифровых иров. ЯО 1640696 лительной технике и может быть использовано для отладки в реальноммасштабе времени цифровых программмногопроцессорных систем управления,Цель изобретения - расширение функциональных возможностей. Устройствосодержит регистр ввода, аналого-цифровой преобразователь, К цифроаналоговых преобразователей, два переключателя аналоговых сигналов, модельобъекта, коммутатор аналоговых сигналов, дешифратор, К регистров вывода,коммутатор, коммутирующую матрицу.Устройство обеспечивает отладку в реальном масштабе времени параллельноработающих цифровых процессоров.1 ил. ленияустройство 1 содержит регистр 3 ввода, К циФровых процессоров 4 обработки аналоговых сигналов, аналогией го-циФровой преобразователь 5, К цифроаналоговых преобразователей б, пе- .4 аь реключатели 7 и 8 аналоговых сигналов, модель объекта 9, коммутатор 10 (, аналоговых сигналов, дешифратор 11, ( К регистров 12 вывода, выходы 13 ре ального объекта управления, коммутатор 14, выходные шины 15 - 17 соответственно данных адреса и управления устройства 1, причем шина 15 является двунаправленной, коммутирующую 3 ф матрицу 18. Для пояснения работы устройства 1 к шинам 15 - 17 подключен блок 2 программного управления, в ка"честве которого может быть использована мини- или микро-ЭВМ с соответст-, вующими кросс-системами.1640696 4татор 14. При этом адресное пространство, определяемой разрядностью шины6 адреса, играет роль управляющегоразряда, в зависимости от состояния5 которого осуществляется работа либодешифратора 11, либо коммутатора 14,Оставшиеся (и) разрядов шины 16 адреса используются для адресации к10ячейкам ОЗУ процессоров 4. Таким образом, часть разрядов 1 (где 1=К) уп-равляет коммутатором 14, подключаяшину 15 .данных к шине данных 1-гопроцессора 4, а остальные разряды за;15дают адрес ячеек ОЗУ выбранного процессора 4.На этапе подготовки аналоговой модели многомерного объекта управленияпроизводятся разработка схемы модели"20рования для модели объекта 9 наборсхемы моделирования на операционныхблоках процессора и контроль работоспособности модели при тестовых управляющих и возмущающих воздействиях.Исходные дифференциальные уравнения,описывающие динамику многомерногообъекта управления (объекта, в котором используются .значения несколькихуправляющих координат и нескольких0управляемых координат) вводятся вэь- блок 2, в который предварительно загружается система автоматизации программирования аналогового процессора. В результате работы системы автоматизации программирования получается схема набора модели и выполняетсяее набор в блоке 9. Контроль работымодели объекта выполняется путем подачи тестовых сигналов на входы модели объекта 9 с блока 2 через ре 40гистры 12, ЦАП 6 и переключатели 7.Реакция модели объекта в виде показа.телей качества процесса управления(перерегулирование, число колебаний,время установления процесса, стати 45ческая точность и т,п.) записывается в блок 2 и сравнивается со значениями, полученными экспериментальнона реальном объекте. При необходимости параметры модели на блоке 9 корректируются до достижения удовлетворительного совпадения модели с объектом. В качестве модели объекта 9, например, может быть использована аналоговая вычислительная машина АВК либо аналоговый процессор АИ. Вкачестве коммутатора 10 аналоговыхсигналов может быть использована БИСК 591 КН 3. Коммутирующая матрица 18может быть реализована на БИС К 590КН 14,Устройство работает следующим образом.На этапе подготовки программ дляцифровых процессоров 4 обработки аналоговых сигналов производится последовательная откладка программ для каждого цифрового процессора 4 на блоке2 программного управления,Программа, написанная на языкеассемблера -го процессора 4, вводится с помощью стандартных средств вблок 2 и отлаживается известным способом на программной модели в замедленном масштабе времени. Работа блока 2 осуществляется в соответствии салгоритмом, приведенным на фиг.2.Этопозволяет проверить выполнение логических условий в реализованном алгоритме управления, вывести на экранили печать содержимое внутренних блоков процессоров 4 (ячейки ОЗУ, резултат в АЛУ и т,д.) и результат работьотлаживаемой программы при фиксированных входных параметрах. Если -япрограмма работает неправильно, топроизводится коррекция программы, аотлаженная таким образом программазаписывается во внутреннее ППЗУпрограмм -го процессора 4 с помощьюстандартного программатора. Процессповторяется до отладки и записи вППЗУ соответствующих процессоров 4всех К программ.В результате выполнения этапа подготовки в 1 П 1 ЗУ процессоров 4 загружены отлаженные в нормальном масштабе времени программы управления, а вОЗУ этих процессоров внесены параметры воспроизводимых на этих процессорах законов управления (например,для П-, ПИ- и ПИД-регуляторов в качестве параметров могут служить коэффициенты усиления, постоянные времени, для оптимальных по быстродействию регуляторов - моменты времениизменения параметров и сами парамет 55ры и т.п.).Запись параметров ОЗУ процессоров4 производится блоком 2 через коммуПодача тестовых управляющих и возмущающих воздействий на входы модели объекта 9 из блока 2 и запись в блок 2.их значений производится таким образом, что через дешифратор 11 выби40696 45 50 55 5 Ерается один из регистров 12,в который вводится по шине 15 данных необходимый код, преобразуемый с помощью ЦАП 6 в аналоговую величину, подающуюсяна соответствующий вход модели 9 через переключатель 7. Аналогично через дешифратор 11 выбирается коммутатор 10 аналоговых сигналов, на цифровой вход которого по шине 15 подается код, определяющий номер канала,подключаемого к АЦП 5. Затем запускается АЦП 5 сигналом от дешифратора 11. Цифровое значение аналогового сигнала считывается с регистра 3 в блок 2. При этом выбор регистра 3 также производится блоком 2 через дешифратор 11.В результате выполнения этапа почготовки модели объекта управления на модели 9 набрана и отлажена модель динамики многомерного объекта управления в реальном масштабе времени. На этапе откладки в реальном времени программ цифровых процессоров 4 с моделью многомерного объекта переключатели 7 по сигналу от блока 2 через дешифратор адреса переключаются в положение, при котором выходы цифровых процессоров подключаются к входам модели 9. Блок 2 осуществляет пуск аналогового процессора и всех цифровых процессоров 4 обработки аналоговых сигналов. Режим "Пуск" и другие сигналы управпеция блоком 9 вырабатываются блоком 2 и поступают в блок 9 по шине 15 данных при выборе блока 9 сигналом с дешифрлтора 11Возмущающие воздействия на объект управления организуются путем использования блоков тестовых напряжений, имеющихся на серийных аналоговых вычислительных машинах и управляемых с ее клавиатуры, либо переключениями в схеме моделирования, управление которыми осуществляются по шине 15 при наличии сигнала с дешифратора 11,либо подачей возмущающих воздействий с выходов коммутирующей матрицы 18.Процессоры управления наблюдаются в реальном масштабе времени на сьетолучевом многоканальном индикаторе например, ИМ). Необходимые процессы записываются в память блока 2,причем с целью сжатия информации в памяти сохраняются только показатели качества управления - значение пере- регулирования переходного процесса, количество колебаний, время установбпения процесса регулирования после момента подачи возмущения цл объект. Сравнение этих показателей с эталонными значениями или требованиями технического задания позволяют сделать вывод о качестве процессов управления, Если качество управления не удовлетворяет требованиям, то производится отладка (подстройка) параметров в программах упрлвлеция, записанных в процессоры 4. Блок 2 переводит блоки 9 и 4 в режим "Останов" Из блока 2 программного управления на коммутатор 14 задается адрес ячеек ОЗУ выбранного процессора 4. 1 од управлением сигналов с шины 17 управ - пения производится последовательный ввод параметров в процессор 4. После ввода новых параметров в ОЗУ процессоров 4 повторяется моделирование процессов управления и их оценка до удовлетворительного исходя. В противном случае процесс откллдки повторяется сначала, цлпример вносятся изменения в алгоритм и программу управления одного или нескольких процессоров 4.Предлагаемое устройство позволяет отлаживать программы управления, записанные цл цифровых процессорах 4 обработки сигцллов и в более сложном случае, когдл слм объект управления является непрерывно-дискретным. В этом случае аналого-цифровая модель объекта управления реализуется на модели объекта 9, блоке 2 программного управления и средствах преобразования и обмена информацией между ними, т,е. блоках 5, 1 О, 3, 12, 6, 18. Коммутирующая матрица 18 при этом обеспечивает передачу данных из блока 2 после преобразования их ЦА 11 6. В том 10 5 20 25 30 35 40 случае, когда идет процесс откллдкив реальном мясштлое времени, переключатели 7 отключают выходы ЦАП 6 отвходов модели объекта 9.На этапе откладки программы процессоров 4 с релльшю объектом управления переключатели 8 подключают выходы реального объекта к входам процессоров 4. Отладки программ и подстройки параметров в программных процессорах 4 ня этом этапе аналогичны предыдущему этапу.Таким образом, в предложенном устройстве для отладки программ цифровых процессоров обработки аналоговых сигналов обеспечивается расширениекласса решаемых задач за счет отладки в реальном масштабе программ многопроцессорной системы управления, Отладка может проводиться в аналого 5 вой либо аналого-цифровой модели многосвязного объекта управления. Такой режим отладки позволяет .гладить в реальном масштабе времени программы К процессоров обработки аналоговых сигналов В случае многомерного объекта управления, в котором изменение каждого из управляющих воздействий вызывает изменение ряда управляемых величин, т.е, отлддкд управляющих 15 процессоров 4 в системе управления должна производиться одновременно (параллельно), д не друг за другом. Введение модели объекта 9 позволяет расширить границы воспроизведения ре жима реального времени на случай от - ладки цифровых многопроцессорных систем управления многомерными объектами, Кроме того, в устройстве, благодаря применению коммутатора 14, воз 25 можно автоматическое изменение по программе блока 2 параметров каждого из К каналов цифрового управления, что облегчает процесс отладки и настройки параметров цифровых систем 30 управления, находящихся в процессорах1 редложенный режим отладки программ процессоров с аналоговой (аналого-циФровой) моделью позволяет сократить число выездов к месту реальной эксплуатации многопроцессорной системы управления и уменьшить объем дорогостоящих натурных испытаний,особенно в сложных и аварийных режимах.40Формула изобретения Устройство для отладки программ цифровых процессоров обработки аналоговых сигналов, содержащее первый пе реключатель аналоговых сигналов, аналого-цифровой преобразователь, первый цифроаналоговый преобразователь, первый и второй регистры, причем первый вход устройства для подключения к первому выходу реального объекта управления соединен с первым входом первого переключателя аналоговых сигналов, вь 1 ход аналого-цифрового преобразователя соединен с информационным входом первого регистра, вшход которого через двухстороннюю мдГистраль соединен с информационным входом вто- РОГО реГистрд р выход которОГО с Оеди нен с входом первого цифроандлогово 1 о преобразователя, о т л и ч а ю -щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения отладкиВ реальном масштабе времени К программ параллельно рдботающих процессоров, В него введены модель объекта,Кпереключателей аналоговых сигналов, коммутатор, группа из Кпереключателей аналоговых сигналон, Кцифроаналоговых преобразователей, коммутирующая матрица,группа из Крегистров, дешифратори коммутатор анапоговых сигналов,и-й выход объекта реального управления (и - э 2, К) соединен с первым информационным входом соответствующегопереключателя аналоговых сигналовгруппы, выход 1-й переменной моделиобъекта (з. в -+1, К) соединен с соот -Ветствуюцим информационным входом коммутатора аналоговых сигналов и с вторым информационным входом переключателя аналоговых сигналов, выход коммутатора аналоговых сигналов соединен с входом аналого-цифрового пре -образователя, информационный входустройства через двухстороннюю магистраль соединен с управляющими входами модели объекта, коммутатора аналоговых сигналов, информационными входами Крегистров группы, входами управления коммутирующей матрицы и информационными входами коммутатора,адреснь;й вход устройства для подключения к адресным входам цифровых процессоров обработки аналоговых сигналов соединен с управляющим входом коммутатора, с входом денифратора, спервого по шестой выходы которого соединены со стробирующими входами соответственно первого регистра, аналого-цифрового преобразователя, коммутирующей матрицы, коммутатора аналоговых сигналов и моделью объекта,каждый х-й выход первой, второй итретьей групп выходов денифратора соединен с входом стробирования соответственно 1-го аналогового переключателя первой группы, 1-го аналогового переключдтеля второй группы и1-го регистра группы, старший разрядадресного входа устройства соединенс управляющим Входом коммутатора, информационные Выходы которого являютсявыходами устройства для подключенияк информационным входам соответствуюСоставитель И. СигаловРедактор А.Мотыль Техред С.Мигунова Корректор Т.Малец Заказ 1017 Тираж 417 ВНИИПИ Государственного комитет 113035, Москва, Подписноепо изобретениям и отггия Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 10 щих цифровых процессоров обработки аналоговых сигналов, управляющие входы устройства соединены с управлякщими входами цифровых процессоров обработки аналоговых сигналов, анало 5 говый вход х-го цифрового процессора обработки аналоговых сигналов соединен с выходом соответствующего переключателя аналоговых сигналов, ана логовый выход х-го цифрового процессора обработки аналоговых сигналов соедииен с первым входом соответствующего переключателя аналоговых сигналов дополнительной группы, выходи-го регистра соединен с соответствующим входом цифроаналогового преобразователя, выход каждого д-гоцифроаналогового преобразователя соединен с вторым входом соответствующего аналогового переключателя группы и соответствующим входом коммутирующей матрицы, выходы аналоговыхпереключателей группы и коммутирующейматрицы соединены с аналоговыми входами модели объекта.

СмотретьЗаявка

4470194, 20.06.1988

ОТДЕЛ ЭНЕРГЕТИЧЕСКОЙ КИБЕРНЕТИКИ АН МССР

ШОР ИЛЬЯ ЯКОВЛЕВИЧ, ТРАХТЕНБЕРГ АЛЕКСАНДР СРУЛЬЕВИЧ, ЖУРАВЛЕВ АНАТОЛИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: аналоговых, отладки, программ, процессоров, сигналов, цифровых

Опубликовано: 07.04.1991

Код ссылки

<a href="https://patents.su/5-1640696-ustrojjstvo-dlya-otladki-programm-cifrovykh-processorov-obrabotki-analogovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для отладки программ цифровых процессоров обработки аналоговых сигналов</a>

Предыдущий патент: Анализатор логических сигналов

Следующий патент: Устройство для контроля времени выполнения команд

Случайный патент: 199144