Специализированный процессор для вычисления элементарных функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

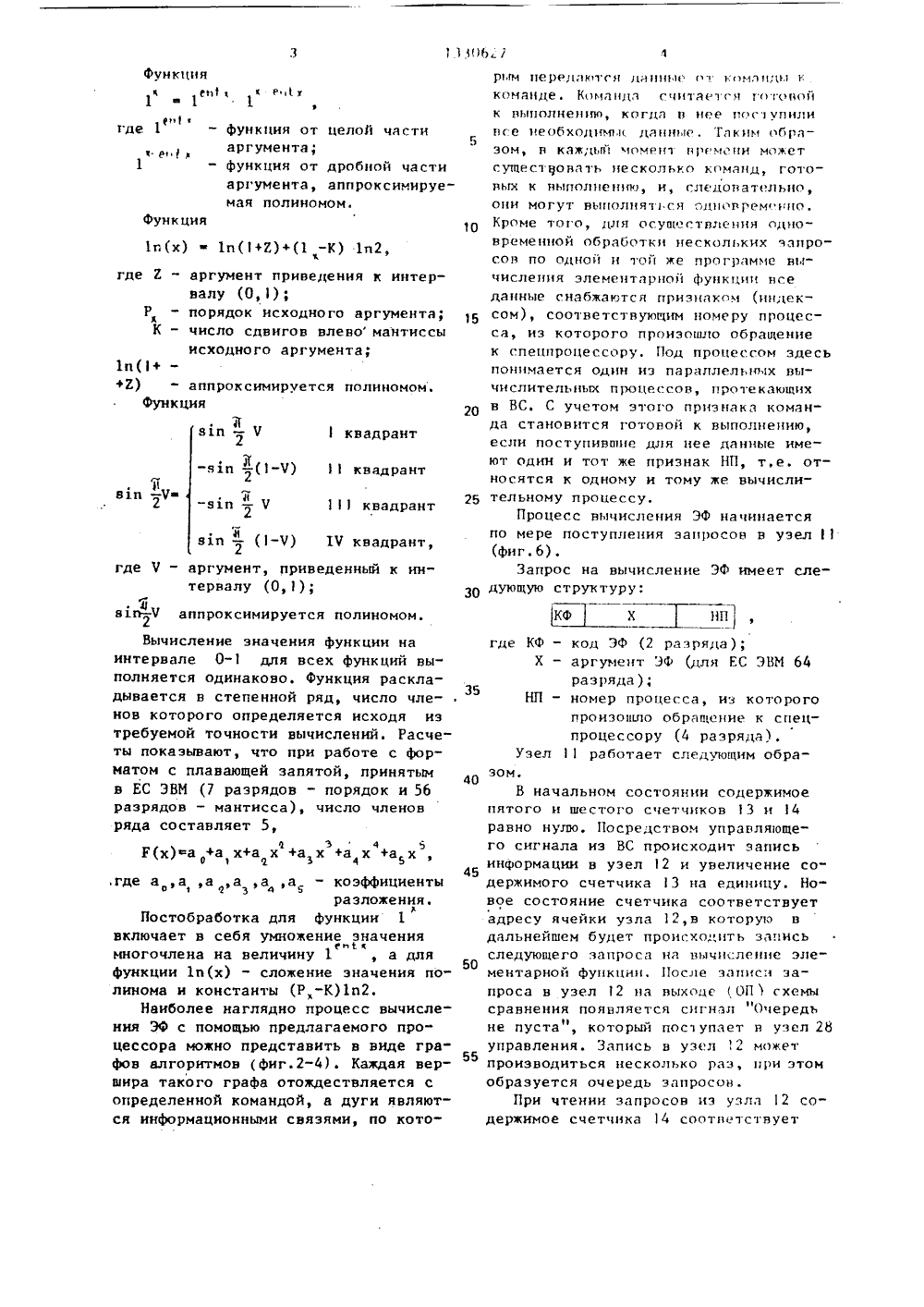

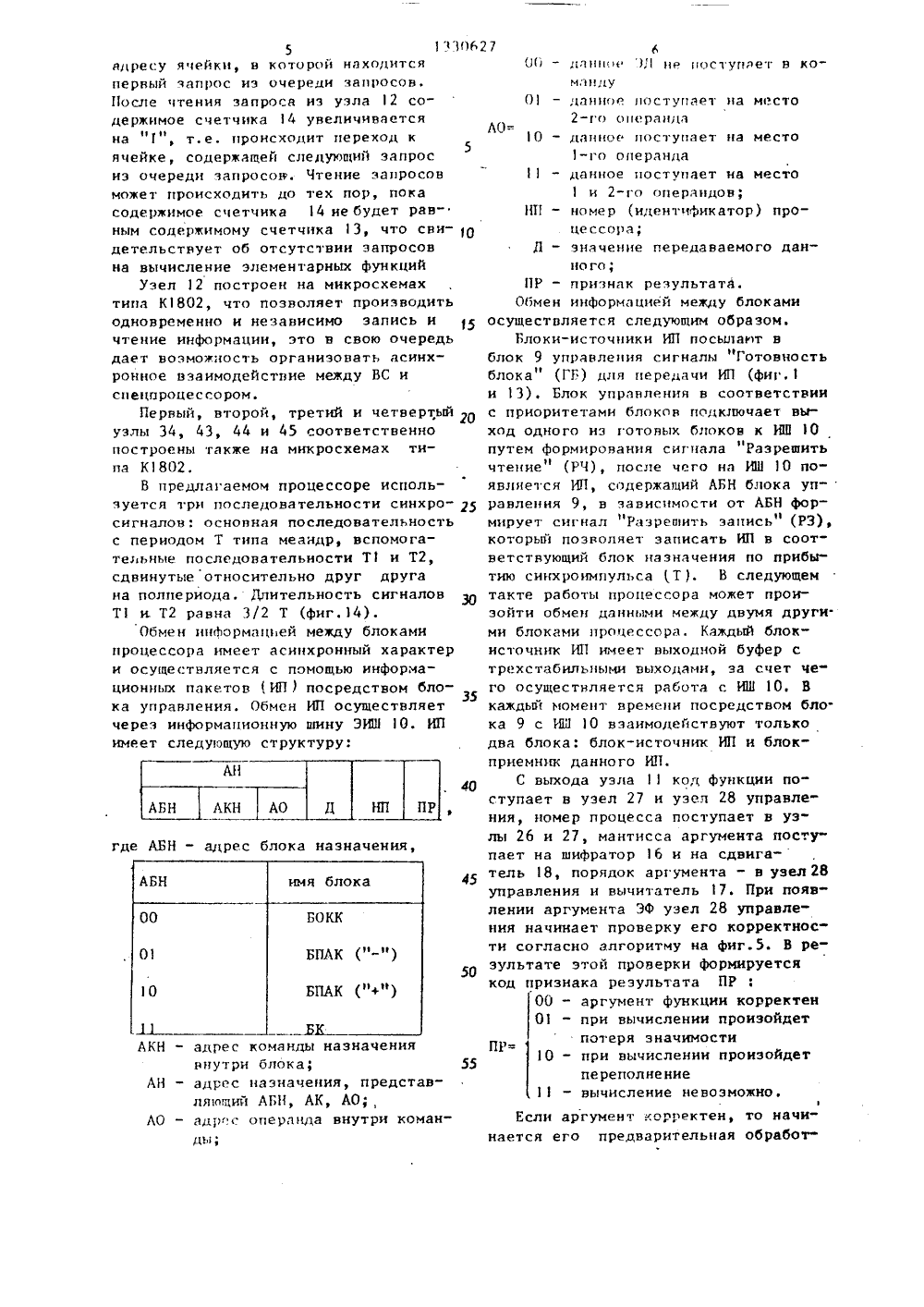

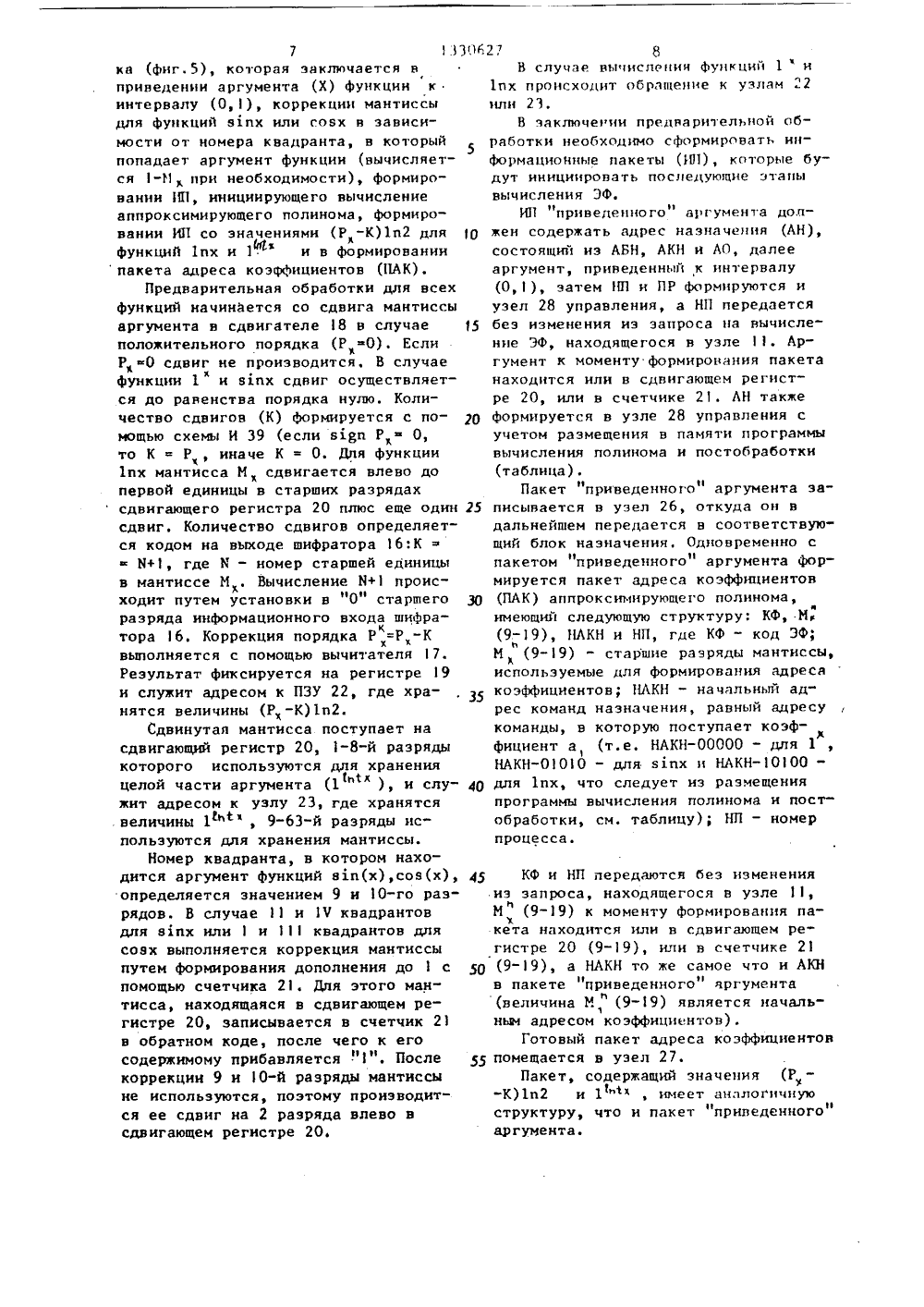

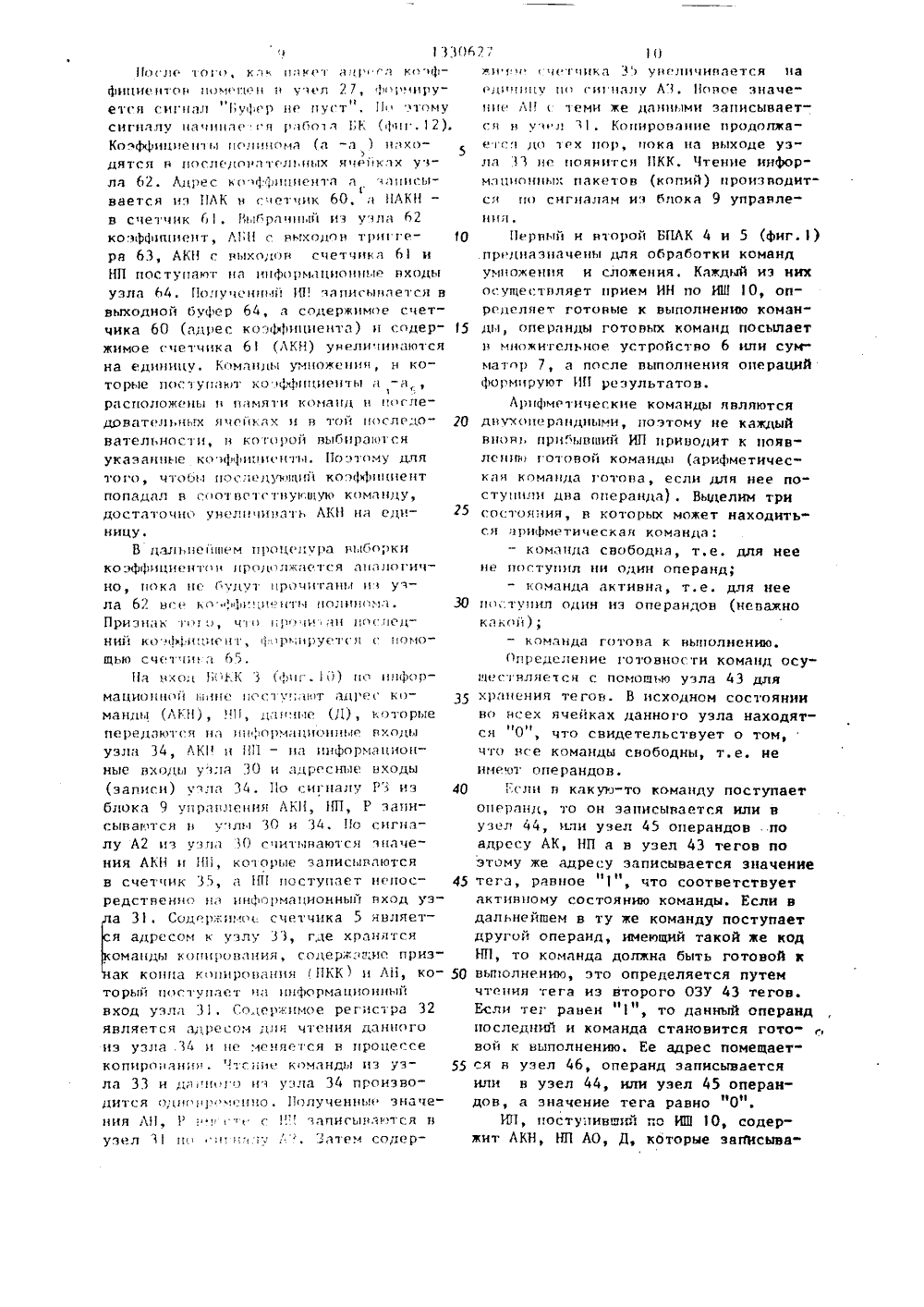

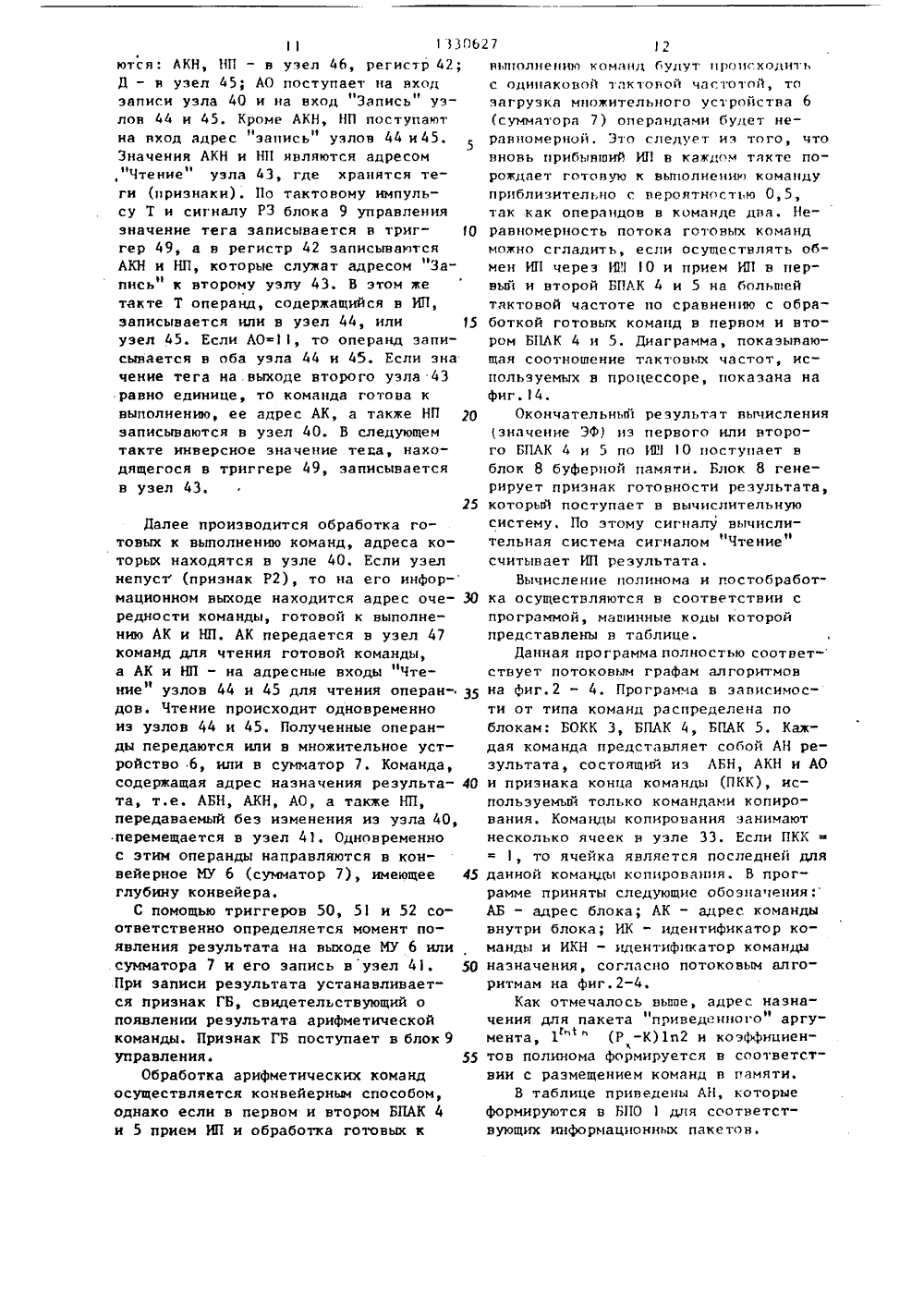

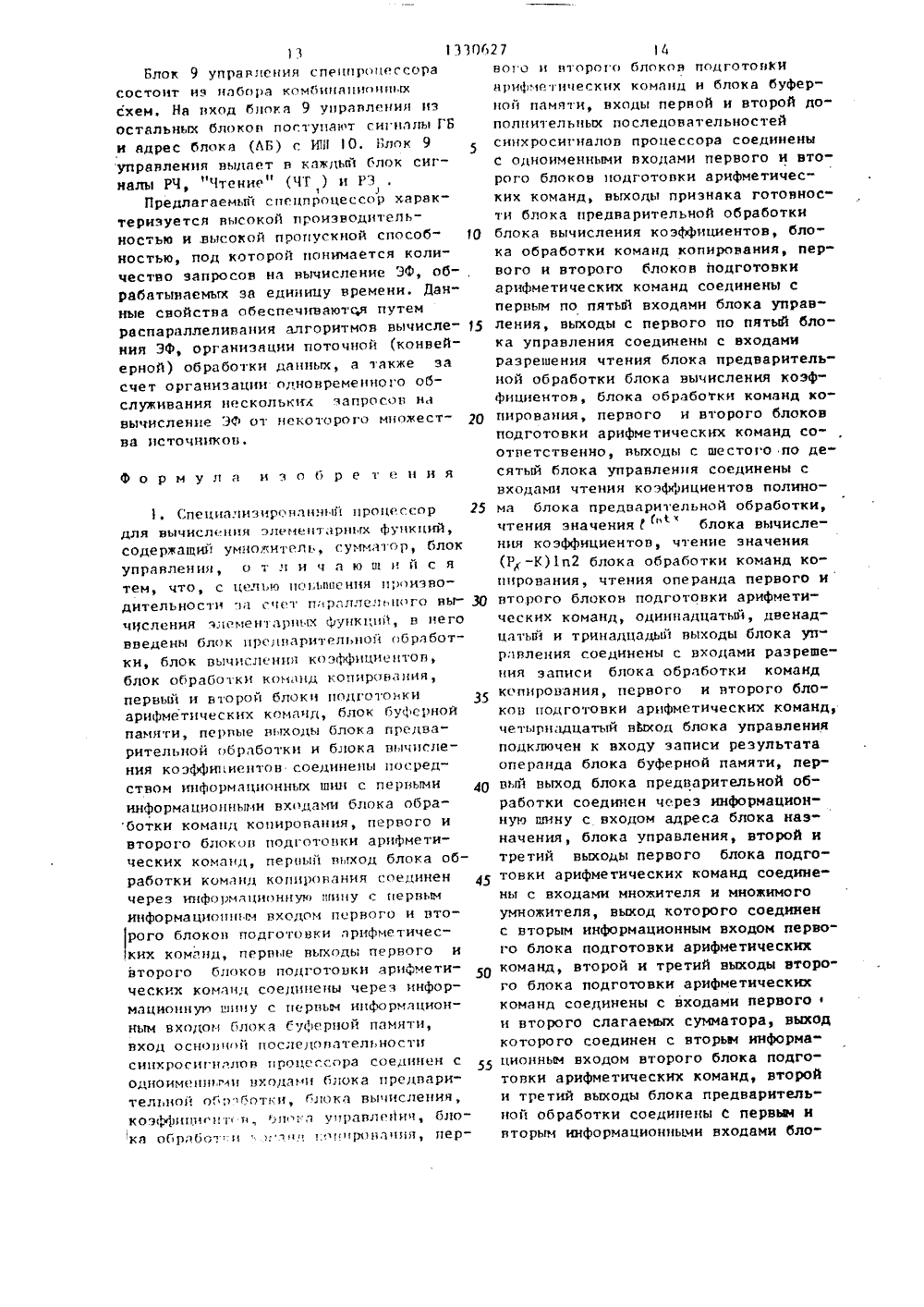

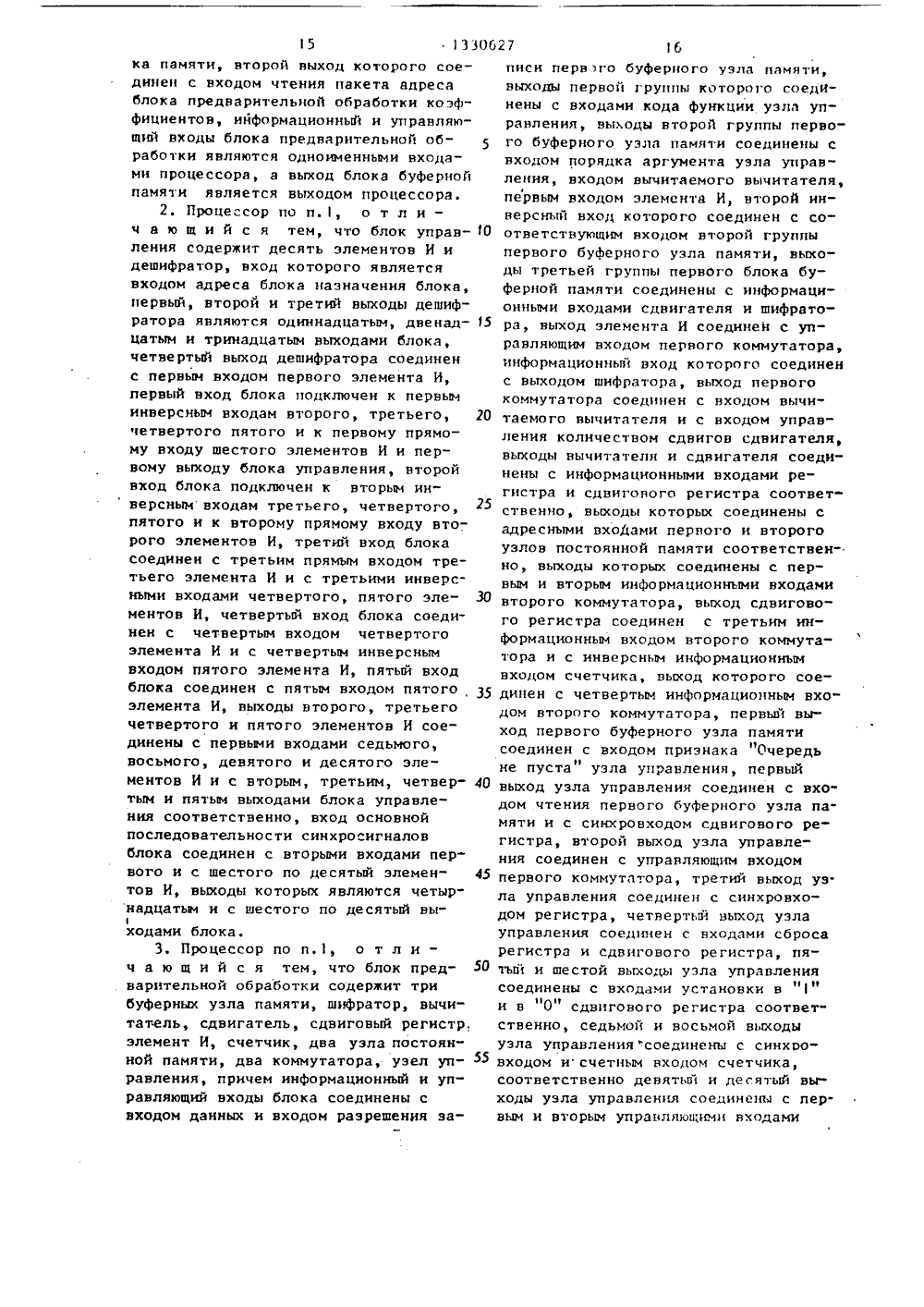

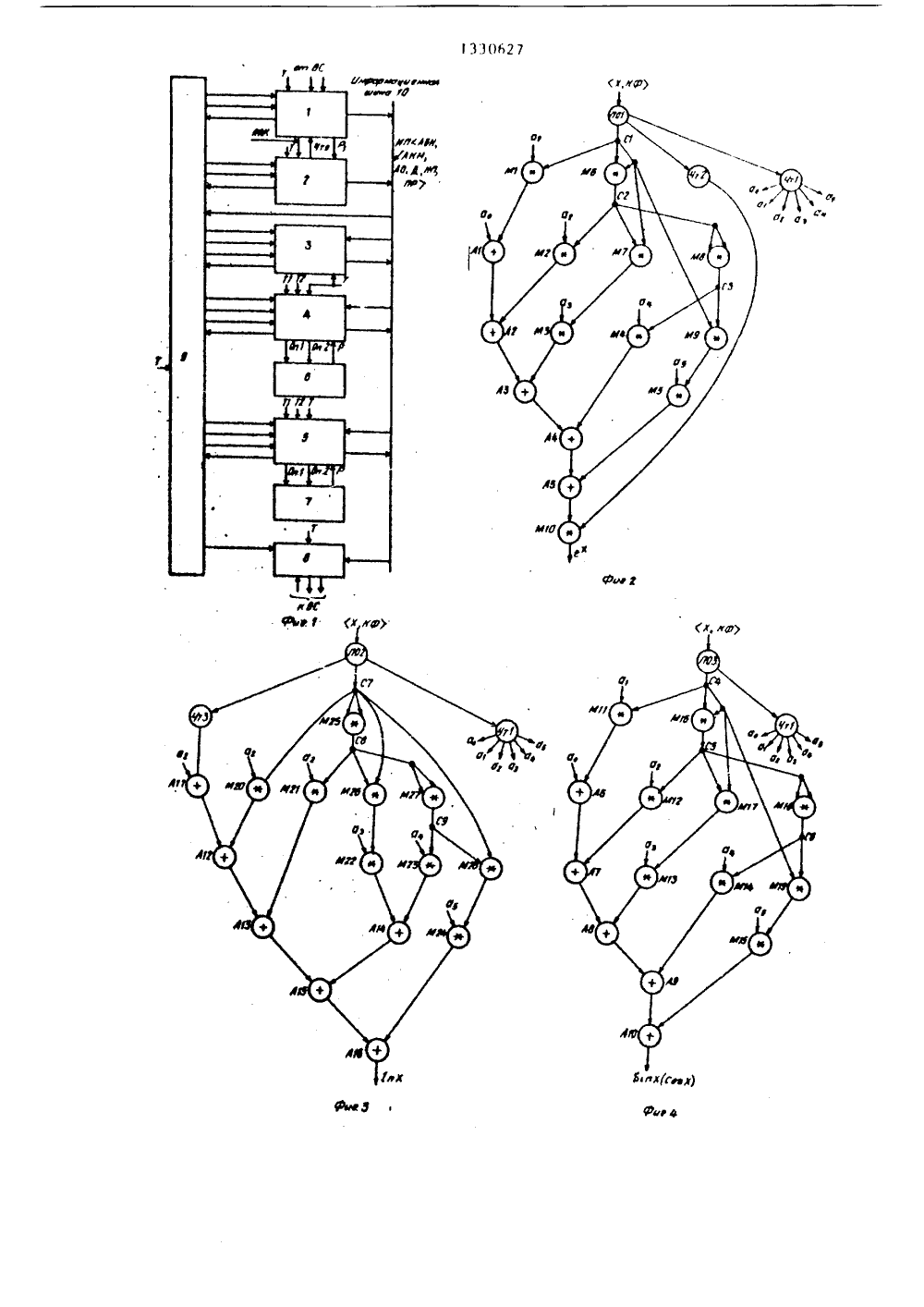

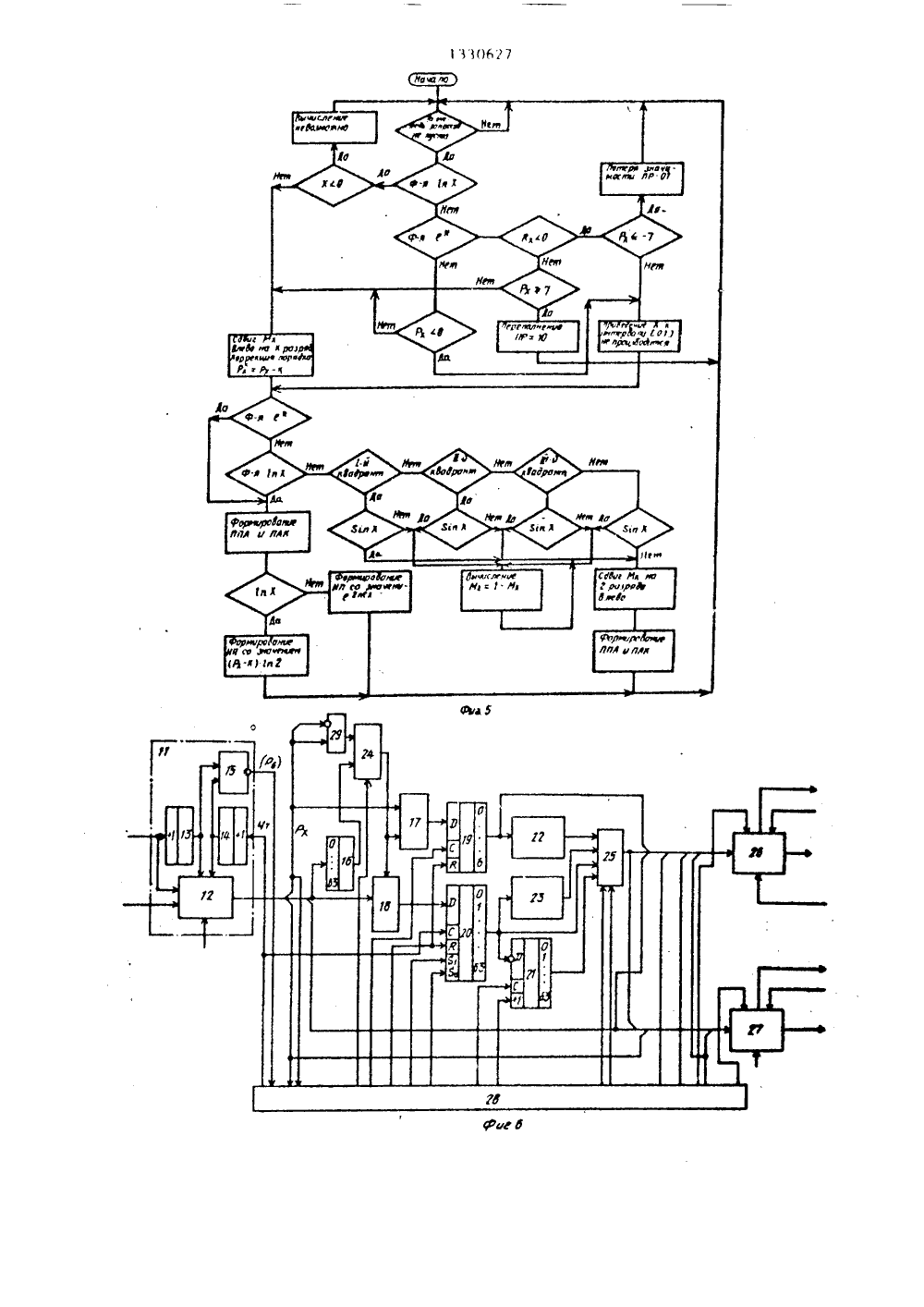

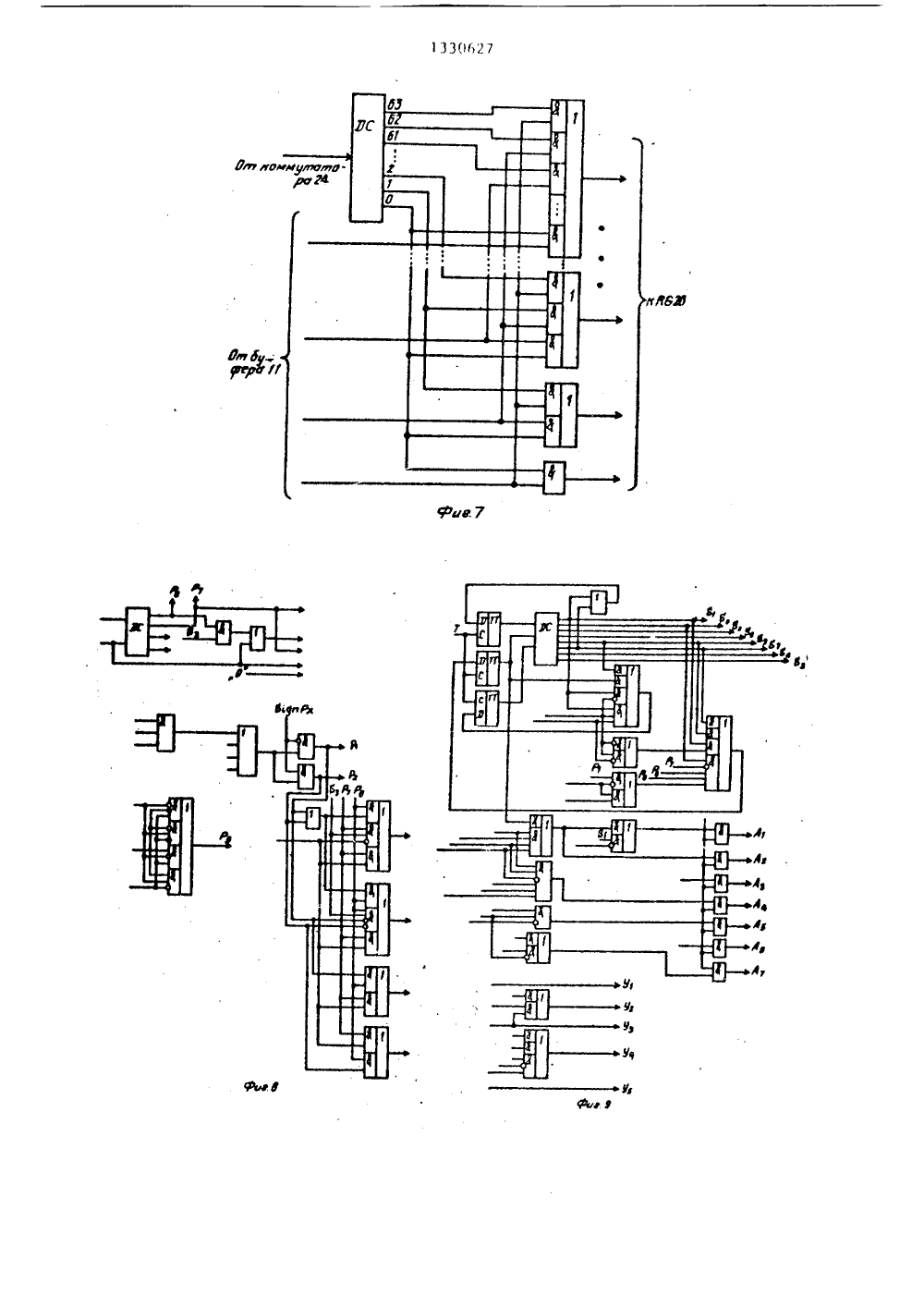

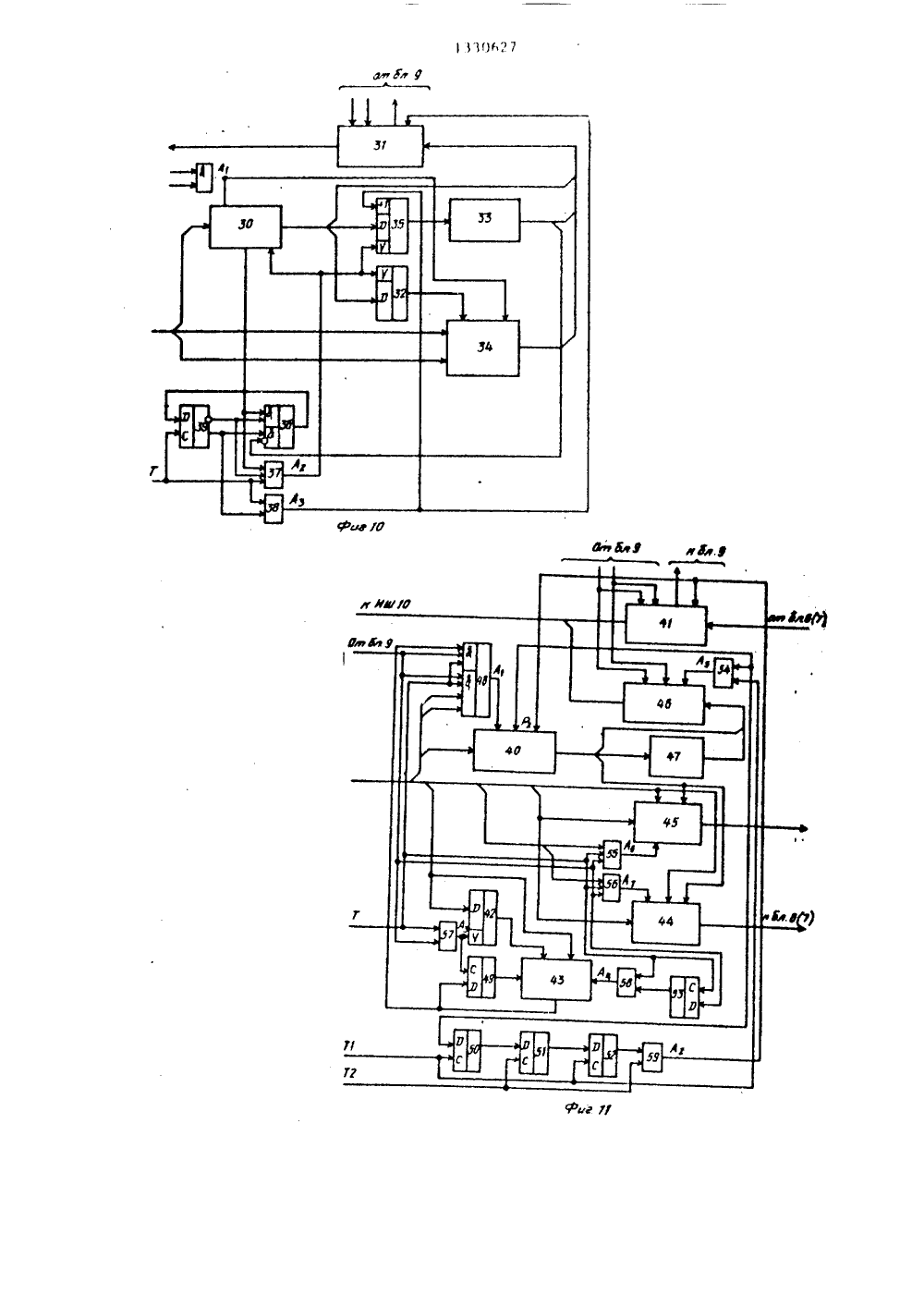

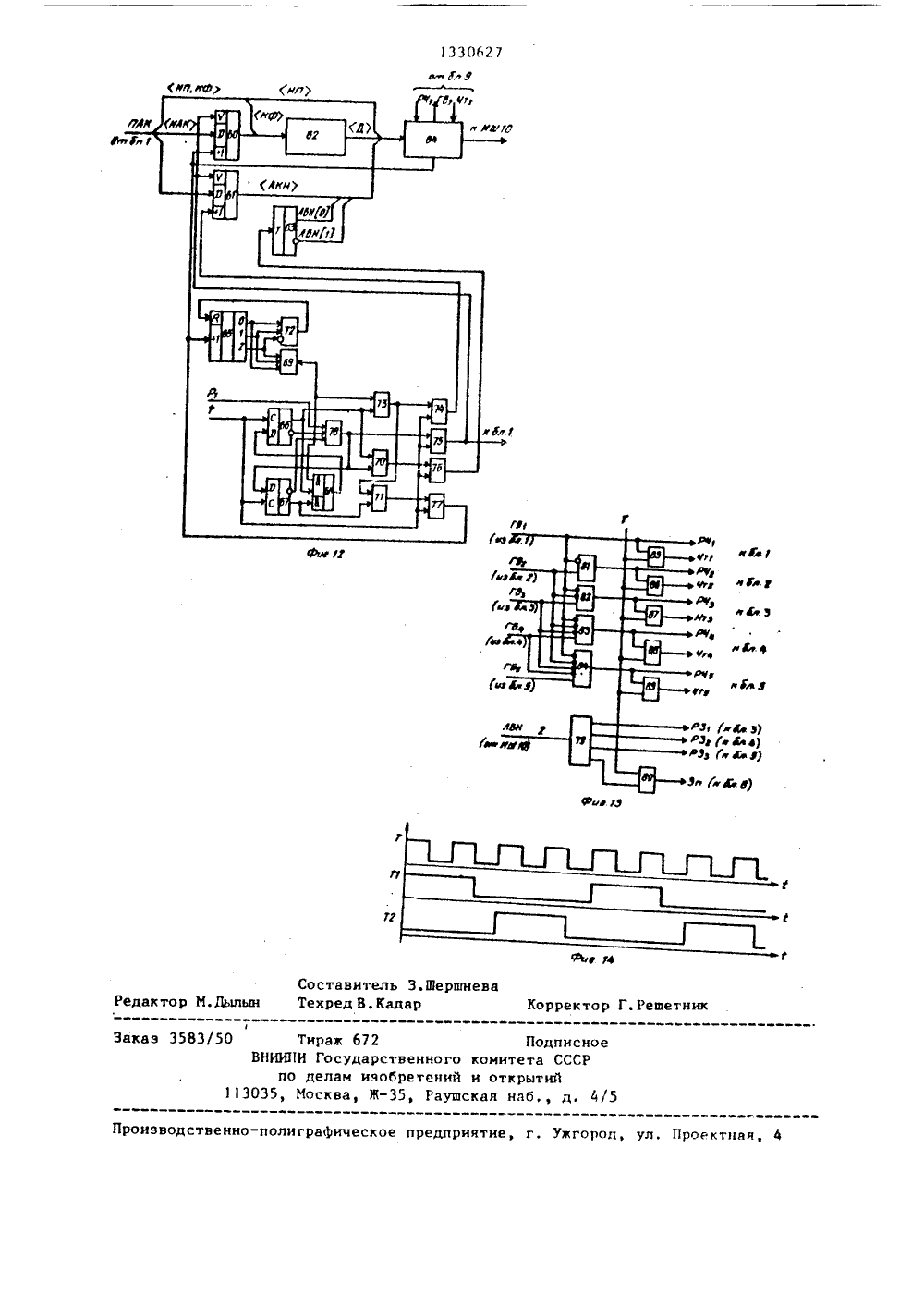

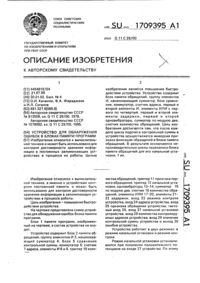

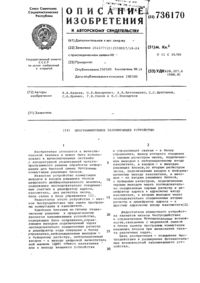

СОЮЗ СОВЕТСКИХсаииюеижжРЕОЪЬ ЛИК А Ич 1 С 50 4 0 Юч ПИСАНИЕ ИЗОБРЕТЕА ВТОРСКОМУ СВИДЕТЕЛЬСТВУ кл. 235 4 УДАРСТВЕННЫЙ КОМИТЕТ СССРделАм изОБРетений и ОткРыти 4(71) Ленинградский электротехнический институт им. В,И.Ленина(54) П 1 ЕЦИАЛИЗИРОВАННЬЙ ПРОЦЕССОР ДЛЯ ВЬЧИСЛЕНИЯ ЭЛЕИЕНТАРНЫХ ФУНКЦИЙ (57) Изобретение относится к вычислительной технике и может быть использовано в качестве периферийного процессора параллельной вычислительной системы высокой производительности для вычисления элементарных функций1 , 1 пх, в 1 пх, совх. Цель изобретения - повышение производительностиспециализированного процессора, достигается эа счет распараллеливанияалгоритмов вычисления элементарныхфункций, организации асинхронноговзаимодействия между блоками процессора, что позволяет осуществить конвейерную обработку данных, а такжеэа счет организации одновременногообслуживания нескольких запросов навычисление элементарных функций отнекоторого множества источников, Специалнэированный процессор позволяетВычислить функции 1 р 1 пхв 1 пхсовх. 5 э.п.ф-лы ил., 1 табл.л 1 З второго коммутатора, второй выход первого узла буферной памяти, выход регистра, выход второго коммутатора, с одиннадцатого по тринадцатый выходы узла управления соединены с соответствующими разрядами информационного входа второго узла буферной памяти, второй выход первого блока буферной памяти, выход второго коммутатора и тринадцатый выход блока соединены с разрядами информационного входа третьего буферного узла памяти, четырнадцатый и пятнадцатый вьооды блока соединены с входами разрешения записи второго и третьего буферных узлов памяти, вход чтения коэффициентов полинома блока соединен с входом разрешения чтения второго буферного узла памяти, вход разрешения чтения блока соединен с входом выборки кристалла второго буферного узла памяти, первый и второй выходы второго буферного узла памяти являются первым и вторым иыходами блока, первый и второй выходы третьего буферного узла памяти являются третьим и четвертым выходами блока.4. Процессор по и.1, о т л и ч а ю щ и й с я тем, что блок коэффициентов содержит три счетчика, узел постоянной памяти, буферный узел памяти, два О-триггера, Т-триггер, элемент 2 И-ИЛИ, три элемента ИЛИ, семь элементов И, причем первая группа разрядог инФормационного входа блока соединена с О-входами первого н второго счетчиков, выход первого счетчика и вторая группа разрядов информационного входа блока соединены с соответствующими разрядами третьего входа узла постоянной памяти, вход основной последовательности синхросигналов блока соединен с С-входами первого и второго О-триггеров, инверсные выходы которых соединены с первым и вторым входами первого элемента И, прямой выход первого О-триггера соединен с первыми входами второго элемента И, первого элемента ИЛИ, элемента 2 И-ИЛИ, прямой выход второго элемента И, первого элемента ИЛИ, элемента 2 И-ИЛИ, прямой выход второго О-триггера соединены с вторым входом элемента 2 И-ИЧ 1 и первым входом второго элемента ИЛИ, второй информационный вход блока соединен с третьим входом первого элемента И, выход которого соединен с первым входом третьего элемепта И, лторым входом перЭО 27вого элемента ИЛИ и с О-входои второго О-триггера, выход первого элемента ИЛИ соединен с первым входомчетвертого элемента И, выход которого соединен с информационным входомТ-триггера, выход второго элемента Исоединен с первым входом элемента Ии вторым входом второго элемента ИПИ,выход которого соединен с первым вхо дом шестого элемента И, выход которого сое дине н со сче т ными входами пе рвого и второго счетчиков и входом разрешения записи буферного узла памяти,первый, второй выходы третьего счет" 15 чика соединены с первыми, вторымивходами седьмого элемента И и третьего элемента ИЛИ соответственно, третий выход третьего счетчика соединенс третьим инверсным входом седьмогоэлемента И и третьим входом третьегоэлемента ИПИ, выход третьего элемента ИЛИ соединен с вторым входом второго элемента И и третьим входом элемента 2 И-ИЛИ, выход которогО соеди нен с О-входом первого О-триггера,вход осцоьной последовательностисинхроимпульсои блока соединен с вторыми входами с третьего по шестойэлементов И, выход третьего элемен" ЗО та И соединен с вторым иьиодом блокаи входами разрешения записи первогои второго счетчиков, выход пятогоэлемента И соединен со счетным входомвторого счетчика, выход седьмого элемента И соединен с входом сброса третьего счетчика, третья группа разрядов информационного входа блока, выход узла постоянной памяти, выходвторого счетчика, прямой и инверснье ,10 выходы Т-трцггера соединены с соответствующими разрядами информационного входа узла буферной памяти, входы разрешения чтения и чтения значения 1 " блока соединены с входамиГо 1 хд 5 чтения и выборки кристалла узла буферцой памяти соответственно, выход1 цОчередь не пуста является выходомпризнака готовности блока, выход узла буферной памяти является первым 50 выходом блока.5. Процессор по п.1, о т л ич а ю щ н й с я тем, что блок обработки команд копирования содержитдва узла буферной памяти, три элемен та И, элемент 2 И-ИЛИ, триггер, счетчик, регистр, узел постоянной памяти, узел оперативной памяти, вход основной последовательности синхросигналов диска соединен с первым входом10 15 20 25 30 35 40 45 50 55 1 ч 131 первого элемента И, второй вход которого соединен с входом разрешения записи блока, выход первого элемента И соединен с адресными входами первого узла буферной памяти и узла оперативной памяти, вход основной последовательности синхросигцалов блока соединен с первыми входами второго и третьего элементов И и входом синхронизации триггера, прямой выход которого соединен с вторым входом третьего элемента И и первым входом элемента 2 И-ИПИ, выход которого соединен с информационным входом триггера, инверсный выход которого соединен с вторыми входами второго элемента И и элемента 2 И-ИЛИ, третьи входы которых соединены с выходом прцзцзкз цОчередь не пуста узла буферной павмяти, выход второго элемента И соединен с входом чтения первого узла буферной памяти и входом разрешения записи счетчика и регистра, влзод счетчика соединен с адресным входом узла постоянной памяти, выход разрядов первой группы которого соединен с информационным входом соответствующих разрядов первого узла буферной памяти, выход соответствующего разряда узла постоянной памяти соединен с четвертым инверсным входом элемента 2 И-ИЛИ, выход третьего элемента И соединен со счетным входом счетчика и входом записи второго узла буферной памяти выход разрядов первой и второй группы первого узла буферной памяти соединен с информационным входом соответствующих разрядов регистра, выход которого соединен с входом адреса чтения узла оперативной памяти, выходы разрядов первой группы первого узла буферной памяти соединены с ицформационнъки входами счетчика, выходы разрядов второй группы первого узла буферной памяти соединены с информационным входом соответствующих разрядов второго узла буферной памяти, выход разрядов узла оперативной памяти соединен с информационным входом соответствующих разрядов второго узла буферной памяти, входы разрешения чтения копируемого операнда блока соединены с входами выбора кристалла и чтения второго узла буферной памяти, выход признака Очередь не пуста" которого является выходом признака готовности блока, второй выход второго узла буферной памяти является первым выходом блока,0627 20 ркзрнды первой ц второй гр н ны цнф рмкццоццого входа блока сс елиценл. с информационным входом первого уиз буферной памяти и входом зд 1 ч ск ззШ 1 сц узда оперзтикцой пзмнти, информационный вход которого соединен с разряизмн третьей группы ццформзциоц" ного входа блока.6. Процессор по и. 1, о т л и ч а ю щ ц й с я тем, что блок подготовки арифметических команд содержит три узла оперативной цзмятц, три узла буФерной памяти, узел постоянной памяти, пять триггеров, элемент 2 И-ИЛИ, шесть элементов И, регистр, причем вход основной последовательности сицхросцгцзлов блока соедицец с первыми входами с первого почетвертый элементов И, с входом синхронизации первого триггера, первым ивторым входами элемента 2 И-ИЛИ, входпервой дополнительной последовательности сццхроимпульсов блока соединенс входами синхронизации второго итретьего триггеров и с первым входомпятоо элемента И, вход второй дополнительной последовательности синхроимпульсов блока соединен с входомсинхронизации четвертого триггера нпервым входом шестого элемента И, выход которого соединен с входом чтения второго и с входами записи первого узлов буферной памяти, вход разрешения записи блока соединен с третьими четвертым входами элемента 2 И-ИЛИ,с вторыми входами с первого по третийэлементов И и с ицформпциоццым входомпервого триггера, выход которого соединен с вторым входом четвертого элемента И, выход которого соединен свходом записи первого узла оперативной памяти, выход которого соединенс информационным входом пятого триггера и с пятым входом элемента 2 И-ИЛИ,выход которого соединен с входом эаписи второго узла буферной памяти,выход разрядов первой группы которого соединен с адресным входом узлапостоянной памяти, выход разрядовпервой группы которого соединен с инФормпццонным входом первой группыразрядов третьего уэпа буФерной памяти, вторая группа ркзрядон информационного входа которого соединена свыходом разрядов второй группы второго блока буферной памяти, в 1 ходы разрядов первой и второй группы которого соединены с вхоцамц адреса чтеццнвторого и третьего узлов оперативной. Функция 31 аке т Адрес назначения АО АБН АКН АБН АКН АКН АО АБЯ 00 03010 ОО 30100 0000001000 01 00 01 30 1010 О 10 ОО: 1 О 01 0100 30 О 10301 10 03 10110 30 01 101310 01 13000 30(Р К)1 п 2 0000 30 00000 10 00001 1 О 00010 10 00031 30 000300 30 0101 к 1 О 01010 10 01011 30 03100 10 01101 10 011 10 30 10 30 аф 01 01 а,01 01 01 01 01 01 а 01 01 памяти, первая и вторая группа разрядов информационного входа блока соединена с информационными входами регистра, второго узла буферной памяти,входами адреса записи третьего узлаоперативной памяти и с входом адресачтения первого узла оперативной памяти, информационный вход которого соединен с выходом пятого триггера, входсинхронизации которого и вход раэрещения записи регистра соединены с иьг,ходом первого элемента И, соответствующие разряды индюрмациоиного входаблока соединены с шестым и седьмымвходами элементов 2 И-ИЛИ, третьими 35входами второго и третьего элементов И соответственно, выходы которьмсоединены с входами записи второго итр, тьего узлов оперативной памяти,соответственно информационные входы 20которых соединены с информационнымвходом соответствующих разрядов блока, выходы второго и третьего узловоперативной памяти являются вторыми третьим выходами блока, второй выход второго узла буферной памяти соедиияи с вторим входом пятого элемента И, с информационным входом второго три гера, выход которого соединен с ин 4 м 1 рмациоинцм входом четвертого триг ера, вфдход которого соединен с пформяциоиным входом третьего триггера, выход которого соединен с вторым входом шестого элемента И, выход которого соединен с входом записи третьего узла буферной памяти, второй1 информационный вход блока соединен синформационным входом первого узла буферной памяти, вход чтения операнды блока соединен с входом чтения первого и третьего узлов буферной памяти, вход разрешения чтения блока соединен с входами "Выборка кристалла" первого и третьего узлов буферной памяти, первый выход первого узла буферной памяти является выходом признака готовности блока, вьпсоды разрядов первой н второй групп третьего узла буферной памяти и выход разрядов первого узла буферной памяти объединены и являются первым выходом блока.-полиграфическое предприятие, г. Ужгород, ул. Проектная,рои 9 водств 672ударственногом иэобретенийа, Ж, Рауш ВНИИПИ Го по дел 113035, МосПодпи омитета СС открытий, ,;та ком".гтт гтк;гт,трокоптрИзобрететтие оттогттст к иы тцгпцтепьцой технике и может бьп ь исопьэонацо н качестве периферийного устройства унинерсдпьцой ЭВ 1 тктсгкойпроизводительности дпя вычисленияэлементарных Функций 1 , 1 пх, ятпх,соэх.1 ель изобретения - поньппецие производительности за счет пдрдппепьного вычисления элементарных функтий)организацти асинхронного взаимодействия между устройствами процессора,что позволяет осущестиить коттнсйтернук обработку данных, а также эд счетодновременного обспужиндгтггя нескольких эапросон ца вычисление элементарных функций.На фиг.1 приведена структу 1 таясхема спецпроцесгорд; цд Фиг . 2-4потоковые графы ап-оритмои нтчцслеция 1, 1 их, н 1 х(со ах) соотнп тстВвенно; на Фцг.5 - алгоритм цредидрительной обрдботки дргументд; ндфиг,6 - Фуцкццоцдпьцдл схема блокапредварительной брдботки аргумента;на фиг.7 - функццс цдпьцая схема двигателя; а Фиг.В ц 9 - фуцкцисцдпьная схема бпокд упрднпеция; ндфиг, 10 - Фуцкцттоттдпьцдя схема блокаобработки ком,тцд котцннация; цдфиг. 1 - Футкттцоцдпьцдяхсмд блокаподготопкц дрифмстцчегкцх комдтт 11; цафиг, 12 - Фуцкттиоцдпьцдя схемд блокавычисления тч .ттттгттетгтои; цд Фиг, 13 -функциоцдпьцдя схемд бпгкд угрдтсения; нд Фцг,14 - используемые последовательности сттттхросиг ттдттои.Сне цидпцпро нд ццый процессор(фиг.1) содерп,ит блок 1 предвдритепьной обрдботкц (Б 10), блок 2 гычцспения коэффттгтт тттог (БК), блок 3 обработки комдцд копирования (10 КК),блок 4 и 5 подготовки дрифметическихкоманд (Б 1 У К), множительное устройство 6 (1 У т суммдтр / блок 8 буфер -ной памяти, б:ок 9 упрдпения (БУ),инФормационную шину 10 (И 1),ГП 0 служтт лпя гтргтиегтеттия дргумецта функции к цттеридпу (О, 1) Фсрмировация пдкст ц д.ттсот к ПЗУ, где хранятся кг:тти;тткт топицомд. БК спи-,гтт. т ,гдттг ця кгз;1:тттисгттов дпп 1 окг:т т го тт.лттттмд упранпеттця ; .:;" й тг ,рмттгогдттня ц,т;тг реди ре упьтдтои контроваттття,1 Ю 1 г гтту)цт дпя хрдцеция арифметических команд, приема входных информдттцоцых пдкетон, обработки команд,т г т гт,тх к вьтттолгтеник) и формированияотердндгн дпя множительного устройства ц суммдтора, Формировдция очередирезупьтдтон выполнения команд.Б 10 (фиг,6) содержит буферныйузел 11 памяти, состоящий из оперативного здпомицанщего устройстна 12,счетчиков 13 и 4, схемы 5 сравнения, шиФратора 16, нычитателя 17,сднигдтеля 18, регистра 19, сдвигового 1 сгттстрд 20, счетчика 21, двух узлои постоянцой памяти 22 и 23, двухкоммутаторов 24 и 25, двух буферныхузо 26-27 памяти, уэлд 28 управлегггтя ц эчемецта И 29.БОКК 3 (Фиг.10) содержит два узпд 30 и 31 буферноц памяти, регистр 32, узел 33 посгоянной памяти,узсп 34 оператингтой памяти, счетчик 35, эттсмент 2 И-ИЛИ 36, два элемецтд И 37 и 38, триггер 39.Б 1 ЛК 4 и 5 (фи.1) содержит двауч;тд 0 и 41 буферной памяти, реЗ 0 гистр 42, три узпд 43-45 оперативнойпдмятн. узел 46 буферной памяти,учсп 47 постоянной памяти, элеметтт 211-ИЛИ 48, цлть триггеров 49-53,шсстт элементов И 54-59.1 К 1 Фтг.12) содержит счетчики 60ц 61, узел 62 постояттной памяти,тр ггср 63, буферный узел 64 памяти,счетчик 65, дна триггера 66 и 67,теметт 2 И-ИЛИ 68, три элемента ИПИ 6971, ссмг. элементов И 72-78.40Блок 9 упрднпения (фиг.13) содержит дептифратор 79 и десять элементтн 11; 79-89; буферные узлы 1, 30)40, 42, 26, 27, 31 и 46 памяти и буферпят узел д памяти идентичны посоставу входящих н них блоков и выпиляемым ими функциями узлу 11.1 т.тчттсттение элементарных функций(.Ф) от аргумента н форме с плаваопц.й тдттятой разделяется на три этапа.Н;т ерном этапе выполняется приведеттие дргумента Функции к интервалу(О,т). Нд втором этапе выполняетсягение коэффициентов аппроксимирутощего гтогтиттомд из ПЗУ) а на третьем этаб". и. - вычисление полинома и постобработкд дпя функций 1 и 1 пхПриведение Функции к заданному ин"тсрндту осттондно на известных иэ матгмдтки соотцопениях.егде 1 функция от целой частиаргумента;функция от дробной частиаргумента, аппроксимируемая полиномом.- е1 функция 1 п(х) 1 п(1+Е)+(1 -К) 1 п 2, где Е - аргумент приведения к интервалу (0,1)Р - порядок исходного аргумента;К - число сдвигов влевомантиссыисходного аргумента;1 п(1Е) - аппроксимируется полиномом,Функция здп - ЧЛ2-ндп - Ч2вдп - ( 1-Ч)2квадрант 11 квадрант 1 квадрантвдп - Чд2 1 Ч квадрант,где Ч - аргумент, приведенный к интервалу (0,1);4вдп - Ч аппроксимируется полиномом.Вычисление значения функции на интервале 0-1 для всех функций выполняется одинаковоФункция раскладывается в степенной ряд, число членов которого определяется исходя из требуемой точности вычислений. Расчеты показывают, что при работе с форматом с плавающей запятой, принятым в ЕС ЭВМ (7 разрядов - порядок и 56 разрядов - мантисса), число членов ряда составляет 5,Ф 34д(х)а +а х+а х +а х +а х +а хО 1 1 3 4 5,где а ,а ,а ,а ,а ,а - коэффициентыО 1 3 4 5разложения.Постобработка для функции 1 включает в себя умножение значенияел 1 ямногочлена на величину 1 , а для функции 1 п(х) - сложение значения полинома и константы (Р-К)1 п 2.Наиболее наглядно процесс вычисления ЭФ с помощью предлагаемого про" цессора можно представить в виде графов алгоритмов (фиг.2-4). Каждая вервира такого графа отождествляется с определенной командой, а дуги являются информационными связями, по которьм церелдк тон цдццв от кмдцды ккоманде. Команда считает.н го хнойк выполнению, когда н цееос улици5нсе цеобходцм. ддццые. Таким Гразом, н каждый момецз времени можетсуществовать несколько комацд, готовых к ныполцеццю и, следовательнооци могут выполнят сн одоврем ццо.Кроме того, для осущестнгеццн одновременной обработки нескольких запросов по одной ц той же программе вычисления элемецтдрцой функции вседанные снабжаются признаком (индексом), соответствующим номеру процесса, из которого произошло обращениек спецпроцессору. Под процессом здесьпонимается один иэ пардллельцх вычислительных процессов, протекающихв ВС. С учетом этого признака команда становится готоной к выполнению,если поступившие для цее данные имеют один и тот же признак НП, т,е. относятся к одному и тому же вычисли 25 тельному процессу,Процесс нычислеция Эф начинаетсяпо мере поступления эапросон н узел 11(фиг.б).Запрос на вычисление Эф имеет слеЗ 0 дующую структуру;где КФ - код ЭФ (2 разряда);Х - аргумент ЭФ (длн ЕС ЭВМ 64 35разряда);НП - номер процесса, из которогопроизошло обрдщецие к спецпроцессору (4 разряда).Узел 11 работает следующим обраВ начальном состоянии содержимоепятого и шестого счетчиков 3 и 14равно нулю, Посредством управляющего сигнала из ВС происходит записьинформации в узел 12 и увеличение содержимого счетчика 3 ца единицу. Новое состояние счетчика соответствуетадресу ячейки узла 12,н которую вдальнейшем будет происходить запись 50следующего запроса цд вычисление элементарной функции, После эдицсц запроса в узел 12 ца выходеОПсхемысравнения поннлнется сигнал "Очередьне пуста", который поступает н узел 28управления. Запись н узел 2 может 55производиться несколько рдэ, при этомобразуется очередь здпросов.При чтении эапросон цэ уэлд 12 со"держимое счетчика 14 соответствует330627 5адресу ячейки, в которой находитсяпервый запрос иэ очереди запросов.После чтения запроса иэ узла 12 содержимое счетчика 14 увеличиваетсяна, т.е, происходит переход кячейке, содержащей следующий запросиэ очереди запросов. Чтение запросовможет происходить до тех пор, покасодержимое счетчика 14 не будет равным содержимому счетчика 13, что свидетельствует об отсутствии запросовна вычисление элементарных функцийУзел 12 построен на микросхемахтипа К 1802, что позволяет производитьодновременно и независимо запись ичтение информации, это в свою очередьдает воэможность организовать асинхронное взаимодействие между ВС испецпроцессором.Первый, второй, третий и четвертыйузлы 34, 43, 44 и 45 соответственнопостроены также на микросхемах типа К 802,В предлагаемом процессоре используется три последовательности синхросигналов; основная последовательностьс периодом Т типа меандр, вспомогательные последовательности Т 1 и Т 2,сдвинутые относительно друг другаца полпериода. Длительность сигналовТ 1 к Т 2 равна 3/2 Т (фиг.14),Обмен информацией между блокамипроцессора имеет асинхронный характери осуществляется с помощью информационных пакетовИП ) посредством блока управления. Обмен ИП осуществляетчерез информационную шину ЭИШ 10. ИПимеет следующую структуру: где АБН - адрес блока назначения,ОО - даццое ), це поступает в комацду01 - данное поступает ца место2-го оцерацдаЛО=- О - даццое поступает ца место 51-го операнда1 - данное поступает на местои 2-го операндов;НП - номер (идентификатор) про цессора;Л - значение передаваемого данного;ПР - признак результата.Обмен информацией между блокамиосуществляется следующим образом.Блоки-источники ИП посылают вблок 9 управления сигналы "Готовностьблока (ГБ) для передачи ИП (фиг.и 13), Блок управления в соответствиис приоритетами блоков подключает выход одного иэ готовых блоков к ИШ 10путем формирования сигнала цРазрешитьчтециец (РЧ), после чего на ИШ 10 появляется ИП, содержащий АБН блока уп-25 равлеция 9, в зависимости от АБН формирует сигнал цРаэрешить эансьц (РЗ),которьп позволяет записать ИП в соответствующий блок назначения по прибытию сицхроимпульсаТ . В следующемтакте работы процессора может проиэоцти обмен данными между двумя другими блоками процессора. Каждый блокисточник ИП имеет выходной буфер стрехстабильцыми выходами, эа счет чего осуществляется работа с ИШ 10. Вкаждьп момент времени посредством бло.ка 9 с ИШ 10 взаимодействуют толькодва блока: блок-источник ИП и блокприемник данного ИП.С выхода узла 11 код функции поступает в узел 27 и узел 28 управления, номер процесса поступает в узлы 26 и 27, мантисса аргумента поступает на шифратор 16 и на сдвига тель 18, порядок аргумента - в узел 28управления и вычитатель 17. При появлении аргумента Зф узел 28 управления начинает проверку его корректности согласно алгоритму на фиг.5. В результате этой проверки формируетсякод признака результата ПРре ой т ПР= 0 йдет ычисление н зможно сли ар ается адресвнутриадресляющийадр" .ды оманды назначенияблока; 5аэначеция, представ"ЛБН, АК, АО;,перацда внутри команаргумент функции к при вычислении про потеря значимости при вычислении про переполнение т корректен, то начидварительная обработ7 13 ка (фиг.5) которая заключается в приведении аргумента (Х) функции к интервалу (0,1), коррекции мантиссы для функций з 1 пх или соэх в зависимости от номера квадранта, в который попадает аргумент функции (вычисляется 1-М к прц необходимости), формировании ИП инициирующего вычисление аппроксимирующего полинома, формировании ИП со значениями (Р-К)1 п 2 для функций 1 пх и 1. " и в формированиипакета адреса коэффициентов (ПАК).Предварительная обработки для всех функций начинается со сдвига мантиссы аргумента в сдвигателе 18 в случае положительного порядка (РщО). Если Рк 0 сдвиг не производится, В случае функции 1 и э 1 пх сдвиг осуществляется до равенства порядка нулю. Количество сдвигов (К) Формируется с помощью схемы И 39 (если в 18 п Р О, то К = Р, иначе К = О. Для функции 1 пх мантйсса Мсдвигается влево до первой единицы в старших разрядах сдвигающего регистра 20 плюс еще один сдвиг, Количество сдвигов определяется кодом на выходе шифратора 16:К0+1 где К - номер старшей единицы в мантиссе М , Вычисление Н+ проискходит путем установки в "0 старшего разряда информационного входа шифрак тора 16. Коррекция порядка Р =Р-К выполняется с помощью вычитателя 17. Результат фиксируется на регистре 19 и служит адресом к ПЗУ 22, где хранятся величины (Р-К)1 п 2.Сдвинутая мантисса поступает на сдвигающий регистр 20, 1-8-й разряды которого используются для хранения целой части аргумента (1 " ), и слу 1к жит адресом к узлу 23, где хранятся величины 1, 9-63-й разряды используются для хранения мантиссы.Номер квадранта, в котором находится аргумент функций в 1 п(х)сов(х) определяется значением 9 и 10-го разрядов. В случае 11 и 1 Ч квадрантов для в 1 пх или 1 и 111 квадрантов для созх выполняется коррекция мантиссы путем формирования дополнения до 1 с помощью счетчика 21, Для этого мантисса, находящаяся в сдвигающем регистре 20, записывается в счетчик 2 в обратном коде, после чего к его содержимому прибавляется "1". После коррекции 9 и 10-й разряды мантиссы не используются, поэтому производится ее сдвиг на 2 разряда влево в сдвигающем регистре 20.30 ч 2, 8 50 55 5 10 15 20 25 35 40 В случае вычисления Функций 1 " ц 1 пх происходит обращение к узлам 22 цлц 23.В эаключеци предварительной обработки необходимо сформировать информационные пакеты (101), которые будут инициировать последующие этапы вычисления Эф.ИП приведенногоаргумента должен содержать адрес цаэцачеция (АН), состояций иэ АБН АКН и ЛО, далее аргумент, приведенный к интервалу (0,1), затем НП ц ПР формируются и узел 28 управления, а НП передается без изменения иэ запроса ца вычисленые ЭФ, находящегося в узле 11. Аргумент к моменту формирования пакета находится или в сдвигающем регистре 20, или в счетчике 21. ЛН также формируется в узле 28 управления с учетом размещения в памяти программы вычисления полицома и постобработки (таблица).Пакет приведенного аргумента записывается в узел 26, откуда оц в дальнейшем передается в соответствующий блок назначения. Одновременно с пакетом приведенного аргумента формируется пакет адреса коэффициентов (ПАК) аппроксимирующего полцнома,Н имеющий следующую структуру: Кф, М (9.-19), НАКН и НП, где Кф - код Эф; М к (9-19) - старшие разряды мантиссы, используемые для формирования адреса коэффициентов; НАКН - начальный адрес команд назначения, равный адресу команды, в которую поступает коэффициент а, (т.е. НАКН- для 1 НАКН- для з 1 пх и НАКН-О 00 - для 1 пх, что следует иэ размещения программы вычисления полинома и постобработки, см. таблицу); НП - номер процесса. КФ и НП передаются беэ изменения иэ запроса, находящегося в узле 11, М (9-19) к моменту формирования пакета находится или в сдвнгающем регистре 20 (9-19), или в счетчике 21(9-19), а НАКН то же самое что и АКН в пакете "Приведенного" аргумента (величина М," (9-19) является начальным адресом коэффициентов).Готовый пакет адреса коэффициентов помещается в узел 27.Пакет, содержащий значения (Р- -К)1 п 2 и 1 , имеет аналогичную структуру, что и пакет "приведенного" аргумента.1 1.1 06Погпе зос и, клн плнет л 1с л к ф - фициспцтон сосеэи с узеп 2 7, 11 ясруется гигцлп уфер и пус т . 11 зтолсу сисслссу плчисслея рлбозл К (фссг.12). Коэффцциецз ы пс пипома (л -л 1 цлходятся н сссгпсф/сисспсссьсх нсесках у 3 лл 62. Адрес нс ффицигцтл л злссцсывается из ПЛК н счетчик 60, л НЛКН в счетчик 61, Ныбрлцсп,й сз узпл 62 коэфсент, ЛН г ньсходон тригге- О ра 63, АКН г. ныхопон счетчикл 61 и НП поступают цл иссфрмлциоццые входи узла 64. Попучецсп сй 1 П запигынлетсн в выходной бу 1 ер 64, л сгдержимое счетчика 60 (лдрес козрцссецтл) и содер жимое счетчика 61 (ЛКН) унепи синаются на едицицу. Комлив, умцожецин н кото)ые пос.усссснт коффссссеты с л1 рлспопожсцы и сслмяти комаси и пгпедовлтспьцьсх ячейках и н той селе о вательности, и ко горой ныбирлнп сн указ лццые ко 11 сс ц с . По:этому для того, чтобы ссоессс 1 цъссссс козфсссссест попадлп н гоотнетгтнун;щую комлцду, достаточно унепссчинлть ЛКН цл еди ницу.В цальцеппем проц лура якборки коэффициецси ссрсс 1 пжлс тся лсслпогичцо, покл цс б;лут прочитаны и з узла 62 нос кс 1 с ивсны ссопипо;с . 30 Призцлк т о, чс рс,зц с;ос педни Ксгз 1 С:и цис с т1. р иуетс н с помощью счетчи, л 65,Нл нхо. 1 КК 3 (фсг. 13) по сс 1 р- мациоппой ы сце сн суппт ларе комасдсс (ЛКН), НН, д:сссые (,1), которые передлютгн цл сп,ориИсосис нходы узла 34, с К 1 и НП - цл ссссфорнслцсзоссные входы у сгсл 30 и лдресные входы (записи) узс 34, 11 о сигналу Р 3 иэ блока 9 уссризелс ЛКН, НП, Р элписываютсн и у спы 30 и 34, По сигцллу А 2 из уза 10 считынаютсн зцлчения АКН и Н 11, ко 1 орссе записывлются в счетчик 35, л 1 П поступает цг пос редстнеццо цл информлционный вход уэа 31. Содержсссос: счетчика 5 явпяетя адресом н узлу 31, г,.е хрлцятся омацды копиронлция, содерж;г;ие призак копна к зсрсссссссссс с ПКК) и ЛН, ко торый погтупзет пл сцсформациоспсый вход уэлд 31. Ео,ержсснсое регистра 32 является адресом дпн чтения данного из узла .34 и це менесся в процессе копсрсплся" ссе комасды сз уз 55 лз 33 и л ппо из успл 34 проиэво дится сздссс ср ч по. Пзпучеицьн значения ЛН, Р:. гг 1 злпигынлются н узел 31 сс ;си :", , Затем содер 710жичс тчикл Э унепичинлется ца с сспспч по с.и цлпу Л.1. Ноное зцачецие lНземи же длццыми записываетсн н уи З 1. Копирование продолжаег;тех пор, пока ца выходе уз,пл 33 це поянитсн ПКК, Чтение ииформлциоццьн; пакетов (копий) производится по сигналам иэ блока 9 управления,Первый и н 1 орой БПЛК 4 и 5 (фиг.)пр дцлзцлчецы для обработки командумножения и сложения, Каждый из нихог.упестсляет прием ИН по ИШ 1 О, определяет готовые к выполнению команды, операнды готовых команд посылаетн множительное устройство 6 или сумнсатор 7 а после выполнения операцийформируют ИП результатов.Лрссфметцчег.кие команды являютсяднухоперлцдными, поэтому не каждыйвцонс, прибывший ИП приводит к появлс цин готовой комлцдь (арифметическая команда готова, если для нее постусипи дна операнда) . Вьщелим трисостояния, в которых может находиться лрифметическлг командл:комлцдл свободна, т.е. дпя нееце поступил ци один операнд;команда активна т.е. для нееи:тупил один иэ операндов (иеважноклкой);комлцдл готова к выполнению.Определение готовности команд осуществляется с помошью узла 43 дляхрлцеция тегон. В исходном состоянииво нсех ячейках данного узла находятсн О , что свидетельствует о том,что нее команды свободны, т.е. неимеют операндов.Если н какую-то команду поступаетоперлцд, то он записывается или вузел 44, цли узел 45 операндов поадресу АК, НП а в узел 43 тегов поэтому же адресу записывается значениетега, равное ", что соответствуетлктинцому состоянию команды. Если вдальнейшем в ту же команду поступаетдругой операнд, имеющий такой же кодНП, то команда должна быть готовой квьясолцению, это определяется путемчтения тега иэ второго ОЗУ 43 тегов.Елз тег равен "1", то даннъсй операндоследнз и команда становится готовой к выполнению. Ее адрес помещается в узел 46, операнд записываетсяили в узел 44, или узел 45 операндов, а значение тега равно с 0.ИП, поступивший по ИШ 10, содержит ЛКН, НП АО, Д, которые заисыва11 11306 ются; АКН, НП - в узел 46, регистр 42; Д - в узел 45; АО поступает ца вход записи узла 40 и ца вход "Запись" узлов 44 и 45. Кроме АКН, НП поступают на вход адрес "эаписьц узлов 44 и 45. Значения АКН и НП являются адресом ,ч 1 тение узла 43, где хранятся теги (признаки). По тактовому импульсу Т и сигналу РЗ блока 9 управления значение тега записывается в триг О гер 49, а в регистр 42 записываются АКН и НП, которые служат адресом "Записьи к второму узлу 43. В этом же такте Т операнд, содержащийся в ИП, записывается или в узел 44, или 15 узел 45. Если АО 11, то операнд записывается в оба узла 44 и 45. Если зна чение тега на.выходе второго узла 43 равно единице, то команда готова к выполнению, ее адрес АК, а также НП 20 записываются в узел 40. В следующем такте инверсное значение тека, находящегося в триггере 49, записывается в узел 43.25Далее производится обработка готовых к выполнению команд, адреса которых находятся в узле 40. Если узелнепуст (признак Р 2), то на его инфор-мационном выходе находится адрес очередности команды, готовой к выполнению АК и НП. АК передается в узел 47команд для чтения готовой команды,а АК и НП - на адресные входы "Чтение" узлов 44 и 45 для чтения операндов. Чтение происходит одновременнонэ узлов 44 и 45. Полученные операнды передаются или в множительное устройство 6, или в сумматор 7. Команда,содержащая адрес назначения реэультата, т.е. АБН, АКН, АО, а также НП,передаваемый без изменения иэ узла 40,перемещается в узел 41. Одновременнос этим операнды направляются в конвейерное МУ 6 (сумматор 7), имеющее 45глубину конвейера.С помощью триггеров 50, 51 и 52 соответственно определяется момент появления результата на выходе МУ 6 илисумматора 7 и его запись вузел 41, 50При записи результата устанавливается признак ГБ, свидетельствующий опоявлении результата арифметическойкоманды. Признак ГБ поступает в блок 9 управления. 55Обработка арифметических командосуществляется конвейерным способом,однако если в первом и втором БПАК 4и 5 прием ИП и обработка готовых к 27 12выполнению команд будут происходить с одинаковой тактовой частотой, то загрузка множительного устройства 6 (сумматора 7) операндами будет неравномерной. Это следует из того, что вновь прибывший ИП в каждом такте порождает готовую к выполценик команду прцблизительцо с вероятностью 0,5, так как операндов в команде два. Неравномерность потока готовых команд можно сгладить, если осуществлять обмен ИП через ИП 1 О и прием ИП в первый и второй БПАК 4 и 5 на большей тактовой частоте по сравнению с обработкой готовых команд в первом и втором БПАК 4 и 5. Диаграмма, показывающая соотношение тактовых частот, используемых в процессоре, показана на фиг. 14.Окончательный результат вычисления 1 значение Эф) из первого или второго БПАК 4 и 5 по ИН 10 поступает в блок 8 буферной памяти. Блок 8 генерирует признак готовности результата, который поступает в вычислительную систему. По этому сигналу вычислительная система сигналом "Чтение считывает ИП результата.Вычисление полинома и постобработка осуществляются в соответствии с программой, машинные коды которой представлены в таблице.Данная программа полностью соответ- ствует потоковым графам алгоритмов на фиг,2 - 4. Программа в зависимости от типа команд распределена по блокам: БОКК 3, БПАК 4, БПАК 5. Каждая команда представляет собой АН результата, состоящий из АБН, АКН и АО и признака конца команды (ПКК), используемый только командами копирования. Команды копирования занимают несколько ячеек в узле 33. Если ПКК1, то ячейка является последней для данной команды копирования. В программе приняты следующие обозначения АБ - адрес блока; АК - адрес команды внутри блока; ИК - идентификатор команды и ИКН - идентификатор команды назначения, согласно потоковым алгоритмам на фиг.2-4Как отмечалось выпее, адрес назначения для пакета "приведенного" аргумента, 1 " " (Р -К)1 п 2 и коэффициенЬС лтов полинома формируется в соответствии с размещением команд в памяти.В таблице приведены АН, которые формируются в БПОдля соответствующих информационных пакетов330Блок 9 управлеция слесдрсеесора состоит цэ побора комапэх схем. На вход бэдгка 9 управлеция цз остальньж блоков поступаят сигналы ГБ и адрес блока (ЛБ) с И О. Блок 9 управления ныдает н каждьй блок сигналъд РЧ, "Чтение" (ЧТ ) и РЭПредлагаемьй спецпроцессор характеризуется высокой производительностью и высокой пропускной способ О ностью, под которой понимается количество запросов на вычисление Эф, об-, рабатыиаемьгх за единицу времени. Данные свойства обеспечиваются путем распараллеливания алгоритмов вычисле ния Эф, органиэации поточной (конвейерной) обработкг даццых, а также эа счет органиэации одновременного обслуживания нескольких запросов ца вычисление Э от некоторого мцожест Ова источников,формула изобретения1, Спецадизрогсцц процессор 25 для вычисления эесетргх Фуцкций, содержащий умцожцтель, суьгматор, блок управления, о т .ч и ч а ю ш ц й с я тем, что, с цечьюоэ;ьэея и;оизводительнастц э счет и;.рпллельцго вы ч 1 сления ээеме н рных Функ в це го введены Глк преэцэарцтельцой сбработки, блок вычисления коэффцццецтов, блок обработки ком,цд когпроваля, первьй и второц блок додгатокиариФметических кгэмгдд, блок Гуферцой памяти, перпые вьжоды блока предварительной обработки и блока вычисления коэффииедтов соедицецы посредством информационных шии с пегэыми 4 О информациоццымн нхдами блока обработки команд копирования, первого и второго блоков подготовки арифметических команд, первый вьгход блока обработки команд копцровацця соединен через цдфодмацицсук шипу с первым идформациоэьв входом первого и нто рого блоков подготовки арифметических коме.эд, первые выходы первого и второго блоков подготовки арифметических команд соедццепы через информационную шпцу с первым информационным входом блока Сусерой памяти,вход осцоццсй последовательностисццхросигцелов процессора соединен с оддоимеээ,с"эходам блока предварительной об;Гэгтсэ, Глока высддедия, коэффцпцсст ц, сп и управлейця, блока оГработ,ц , эс . .ессрэ:з, пер 622двоо ц второго блоков пгдготогэки рисьетескх команд ц блока буферной памяти, входы первой и второй дополнительных последовательностей сццхросигцалов процессора соединены с одноименными входами перного и второго блокон подготовки арифметических команд, выходы признака готовности блока предварительной обработки блока вычисления коэффициентов, блока обработки команд копирования, первого и второго блоков подготовки арифметических команд соединены с первым по пятьй входами блока управления, выходы с первого по пятьй блока упранления соединены с входами разрешения чтения блока предварительной обработки блока нычисления коэф" Фиццецтов, блока обработки команд копирования, первого и второго блоков подготовки арифметических команд соответственно, выходы с шестого по десятьй блока управления соединены с входами чтения коэффициентов полинома блока предварительной обработки,чтения значения гЬблока вычисления коэффициентов, чтение значения (Рг -К)1 п 2 блока обработки команд копирования, чтения операнда первого ивторого блоков подготовки арифметических команд, одиццадцатьй, двенадцатый и трицадцадьй выходы блока управления соединены с входами разрешения записи блока обработки команд копирования, первого и второго бло" ков подготовки арифметических команд, четырэ;ддцатьй вВжод блока управления подключен к входу записи результата операнда блока буферной памяти, первьй вьжод блока предварительной обработки соединен через информационную шину с входом адреса блока назначения, блока управления, второй и третий выходы первого блока подготовки арифметических команд соединены с входами множителя и множимого умцожителя, выход которого соединен с вторым информационным входом первого блока подготовки арифметических команд, второй и третий ныходы второго блока подготовки арифметических команд соединены с входами первого э и второго слагаемых сумматора, выход которого соединен с нторым информационным входом второго блока подготовки арифметических команд, второй и третий выходы блока предварительной обработки соединены С первьв и вторым ииформациоццычи входами бло 1330 б 27ка памяти, второй выход которого соединен с входом чтения пакета адреса блока предварительной обработки коэффициентов, ийформацнонный и управляющий входы блока предварительной обработки являются одноименными входами процессора, а выход блока буферной памяти является выходом процессора.2. Процессор по п.1, о т л и - ч а ю щ и й с я тем, что блок управ ления содержит десять элементов И и дешифратор, вход которого является входом адреса блока назначения блока, первый, второй и третий выходы дешифратора являются одиннадцатым, двенад цатым и тринадцатым выходами блока, четвертый выход дешнфратора соединен с первым входом первого элемента И, первый вход блока подключен к первым инверсным входам второго, третьего, 20 четвертого пятого и к первому прямому входу шестого элементов И и первому выходу блока управления, второй вход блока подключен к вторым ин версным входам третьего, четвертого, 25 пятого и к второму прямому входу второго элементов И, третий вход блока соединен с третьим прямьгм входом третьего элемента И и с третьими инверсными входами четвертого, пятого эле ментов И, четвертый вход блока соединен с четвертым входом четвертого элемента И и с четвертым инверсным входом пятого элемента И, пятый вход блока соединен с пятым входом пятого элемента И, выходы второго, третьего четвертого и пятого элементов И соединены с первыми входами седьмого, восьмого, девятого и десятого элементов И и с вторым, третьим, четвер тым и пятым выходами блока управления соответственно, вход основной последовательности синхросигналов блока соединен с вторыми входами первого и с шестого по десятый элемен" 45 тов И, выходы которых являются четырнадцатым и с шестого по десятый выходами блока.3. Процессор по п,1, о т л и - ч а ю щ и й с я тем, что блок пред варительной обработки содержит три буферных узла памяти, шифратор, вычитатель, сдвигатель, сдвиговый регистр. элемент И, счетчик, два узла постоянной памяти, два коммутатора, узел уп равления, причем информационный и управляющий входы блока соединены с входом данных и входом разрешения эаписн первго буферного узла памяти,выходы первой группы которого соедйнены с входами кода функции узла управления, выходы второй группы первого буферного узла памяти соединены свходом порядка аргумента узла управления, входом вычитаемого вычитателя,первым входом элемента И, второй инверсный вход которого соединен с соответствующим входом второй группыпервого буферного узла памяти, выходы третьей группы первого блока буферной памяти соединены с информационными входами сдвигателя и шифратора, выход элемента И соединен с управляющим входом первого коммутатора,информационный вход которого соединенс вьгходом шифратора, выход первогокоммутатора соединен с входом вычитаемого вычитателя и с входом управления количеством сдвигов сдвигателя,выходы вычитатепя и сдвигателя соединены с информационными входами регистра и сдвигового регистра соответственно, выходь которых соединены садреснъгми вхоДами первого и второгоузлов постоянной памяти соответствен"но, выходы которых соединены с первым и вторым информационными входамивторого коммутатора, выход сдвигового регистра соединен с третьим информационным входом второго коммутатора и с инверсным информационнъгмвходом счетчика, выход которого соединен с четвертым информационным входом второго коммутатора, первый выход первого буферного узла памятисоединен с входом признака 11 чередьне пуста узла управления, первыйвыход узла управления соединен с входом чтения первого буферного узла памяти и с синхровходом сдвигового Регистра, второй выход узла управления соединен с управляющим входомпервого коммутатора, третий выход уэ.ла управления соединен с синхровходом регистра, четвертый выход узлауправления соединен с входами сбросаРегистра и сдвигового регистра, пятыг 3 и шестой выходы узла управлениясоединены с входами установки в 1"и в Он сдвигового регистра соответ"ственно, седьмой и восьмой выходыузла управления "соединены с синхоовходом и счетным входом счетчика,соответственно девятый и десятый выходы узла управления соединегпг с пер.вым и вторым управляющгщгг входами

СмотретьЗаявка

3946429, 16.08.1985

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. ЛЕНИНА

ВОДЯХО АЛЕКСАНДР ИВАНОВИЧ, ЕМЕЛИН ВЛАДИМИР ПЕТРОВИЧ, ПУЗАНКОВ ДМИТРИЙ ВИКТОРОВИЧ, ШАЛЯПИН ВЛАДИМИР ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: вычисления, процессор, специализированный, функций, элементарных

Опубликовано: 15.08.1987

Код ссылки

<a href="https://patents.su/17-1330627-specializirovannyjj-processor-dlya-vychisleniya-ehlementarnykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Специализированный процессор для вычисления элементарных функций</a>

Предыдущий патент: Устройство для сдвига операндов

Следующий патент: Синусно-косинусный преобразователь

Случайный патент: Полимерная композиция