Устройство для обнаружения ошибок в блоках памяти программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

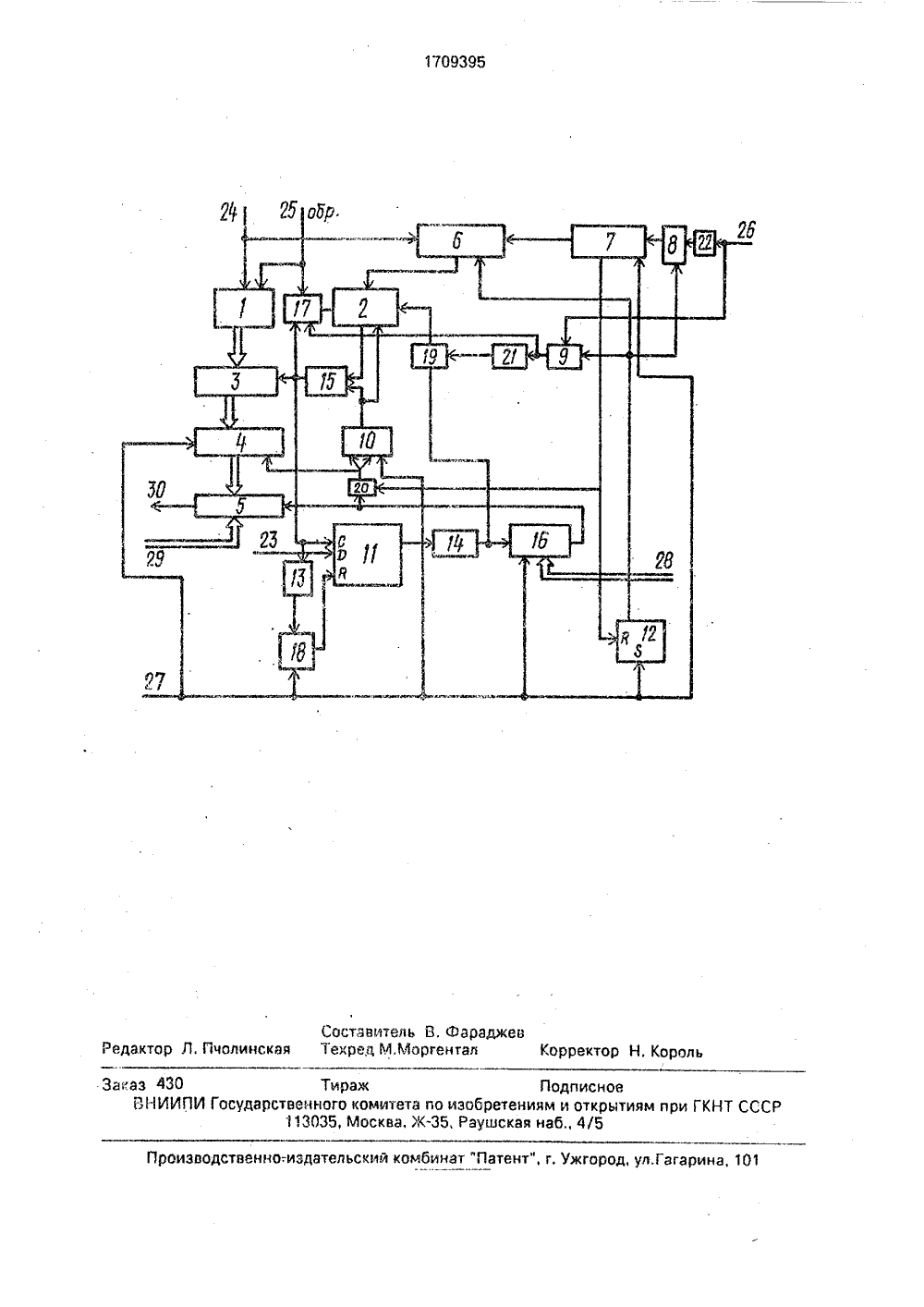

(5)5 6 1 1 С 2 ТЕН ЗОБ ОПИСАН адж ьство СССР/00, 1978,ьство СССР9/00, 1985,(54) У ОШИБ (57) И нои те контро мации ройст Изо ной тех роля и исполь хранен тройствЦел деиств ства дл програБло ный на дит. жимах: в жиме конржит блок 2 емантов И 3 4, блок 5 , коммутато И 8 и 9,триг памяти об- накапливаравнения 6, счетчик ер 10 колиройство соде ий, группу эл сумматор льной суммы а,элементыращенющийконтро7 адрес ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВ 21) 4464819/24(56) Авторское свидетеМг 813508, кл, 6 11 С 29Авторское свидетеМ 1278982, кл. 6 11 С 2 СТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОК В БЛОКАХ ПАМЯТИ ПРОГРАММ обретение относится к вычислитель- нике и может быть использовано для ля достоверности хранения инфорв постоянных запоминающих устах в процессе их работы. Целью бретение относится к вычислитель- нике. а именно к устройствам контостоянной памяти, и может быть овано для контроля достоверности ия информации в запоминающих усах в процессе работы.ь изобретения - повышение быстроя устройства.чертеже представлена схема устрой- обнаружения ошибок блока памяти 1 памяти программ, изображенртеже, в состав устройства не вхоизобретения является повышение быстродействия устройства. Устройство содержит блок памяти обращений, группу элементов И, накапливающий сумматор, блок сравнения, коммутатор, счетчик адреса, первый и второй элементы И, элементы ИЛИ с первого по четвертый, первый и второй элементы задержки, первый и второй одновибраторы, сумматор по модулю два, счетчик количества обращений. Цель изобретения достигается тем, что после каждого цикла подсчета контрольной суммы в устройстве осуществляется инверсия признака фиксации обращений в блоке памяти обращений, В результате исключаются непроизводительные циклы перезаписи блока памяти обращечий для его начальной установки. 1 ил,чества обращений, триггер 11 признака первого обращения, триггер 12 начальйой установки, одновибраторы 13 - 14, сумматор 15 по модулю два, счетчик 16 количества обращений, элементы ИЛИ 17-20, элементы 21- 22 задержки, вход 23 режима контроля устройства, вход 24 адреса устрсйства, вход 25 признака обращения устройства, тактовый вход 26, вход 27 начальной установки устройства, вход 28 количества контролируемых адресов устройства, вход 29 значения контрольной суммы устройства и выход 30 ошибки устройства.Устройство работает в двух рережиме начальной установки и ретроля,Режим начальнои установки устанавли вается при появлении положительного по тенциала на входе 27 устройства. По этомусигналу устанавливается в "О" счетчик 7, сумматор 4 и триггер 10, а В "1" - триггер 12. Зтат же сигнал, праЙДЯ через элемент ИГЛ 18, устанавливает В "О" триггер 11, Положительный потенциал с единичнога выхода триггера 12 разре 1 вэет работу элемента И 8 и 9 и переключает инфармэЦионный ВЬ 1 ход счетчика 7 11 э выход комму 1 отара 6, Первый актовый импульс, пройдя через элемент И 9 и эл 81 ент ИЛИ 17, поступает на вход обоз.1. ения Ола;,димяи, 11 Э эдаесныи ВХОД коГОРОГО чеРез кам 11 УтэтОР б пастУ пает нулеооа з 1:ачение сч 81 чикэ 7, Вь 1 ход т 1 л нтэ И 9 пройдя через элемент 21 задержки и элемент 14 ЛИ 19, поступает на В 1 од записи бло,(а 2 памяти, На информационный охад блока 2 памяти посгупает нулевоЙ потенциал с ед;1 ничнОГО оыхадэ триггера 10. Тамм образом, первым тактовым импульсам по нулевому адресу записывается О . Первый тактовый импульс, пройдя чсреэ злемен Г 22 задержкии элемент И О, пр 1,бэвдяет ксчетчика 7 единицу, описанный цикл рабаты устройстоа позтаряется да переполнения счетчи: а 7, Импульс переполнения счетчика 7 ус 1 энэвливает В "О" три 1 тер 112, нуле;эй потенциал на единичном выходе ка прага перекл 1 очает коммутатор 6 и указывает на Окончание режима начальнзй установки устройства и готовность устройства для рабаты В режиме кон Гроля. Сигнал переполнения счетчика 7, пройдя через элемент ИЛИ 20, переводит триггер 10 о еди- .11 ч 11 ое состояние и обнуляет суммат(1 р 4, В режиме контроля нэ Вход 23 устройства падается еди 11 ичный потенциал, нз Вход 24 падэ 11 тся адрес. э нв вхОД 25 - признак Об "эгдения П 11 л поступлении сиГнэлэ нэ ВКОды 24 и 25 устройства нэ Выходе блокапоявляется значени 8 када, записэ 11 на 1 О па соответствующему адресу, э нэ Выходе блока 2 памяти появляется нулевой сиГ" нал, Тэк катриггер 10 находится в единичном сОстаянии, та нэ Выходе сум 1 лэтарэ 15 по 1(юдул 1 О двэ присутс 1 вует единичный потенциал, котарыЙ разрешает Г 1 рохажден 118 через Группу элементов И 3 кода с Вь 1 хадэ блока 1 11 амяти. 11 Э сумматарг, 4 происходит сложение содержимого счи 7 аниай ячеики пэмп и с предыдущим содержанием сумматора. При этом Выход сумматора 15 па ма дуда доэ поступает нэ тактовый вход .Риггера 11, который устанавливается о "1", Г э переходу из "0" В "1" триггера 111 одна-ВИЛрэтор 14 формирует падокитедьный импу.",ьс, который прибавляет:"116 и через элемент И,11 И 19 поступает нэ Вход ээписи блока 2 пэмЯти. В блоке 2 памяти по адресу считывания записывается 5 10 20 25 30 5 40 45 единичное значение с триггера 10. Если пралсходит обращение к ячейке памяти, к которой уже обращались, то содержимое соответствующего адреса блока 2 памяти равно единице, Следовательно, на выходе сумматора 15 присутствует нулевой потенциал и содержимое данного адреса повторно не накапливается в сумматоре 4, Кроме того, в счетчике 16 не учитыва 1 атся многократные обращения к одним и тем же адресам, счетчик 16 считает только первое абрэщен 1 ле по каждому иэ адресов, Пасде того, как было обращение по всегл контрол;1- руемым адресам, счетчик 16 переполняется, оазрсшает сравнение накопленной суммы в сумматоре 4 с эталонной суммой с входа 29 устройства и устанавливает триггер 10 и су 1.матар В нулевое состояние,Если садержи 1 лос сумматора совпало с кодам на входе 29, то на выходе 30 имеется нулевой потенциал; если содержимое сумматора не совпало со значением кода на Входе 29, то на выходе 30 устройства появляется сигнал, указывающий на неверную работу блока памяти.После перекл 1 очения триггера 10 в нулевое состояние работа устройства происходит 70 чнО тэк . ж 8, кэк описано, с тай разницей, что все ячейки блока 2 памяти установлены В единицу. Па ка 5 кдому первому) обращению из блока 2 памяти считывается единичный сигнал, который, кладываясь со значением триггера 10, дает нэ выходе единичный потенциал, который Осуществляет те же действия, которые описаны, с той разницей, что в блок 2 записывается надь, Если к Ячейке блока 2 памяти производится повторное обращение, та на Вьхаде сумматора 15 имеется нулевой потенциал, который запрещает суммирование на сумматоре 4, В дальнейшем работа устройства повторяется.Таким образом, значительна повышается бь 1 страдействие устройства, поскольку нет необходимости в многократной перезаписи блока 2 памяти после каждого цикла кантооля,Формула изобретения Устройс 1 оо для обнаружения ошибок в блоках памяти программ, содержащее перВый элемент ИЛИ, первый и второй элементы И, коммутатор, информационные входы первой группы которого явля 1 отся информационными входами устройства, выходы коммутатора подключены к адресным входам блока памяти обращений, а информационные входы второй группы коммутатора соединены с выходами группы счетчика адреса, группу элементов И, первые входы которых являются информационными входами устройства, а выходы подключены к информационным входам накапливающего сумматора, выходы которого подключены к информационным входам первой группы 5 блока сравнения, информационные входы второй группы и выход которого являются соответственно входами значения контрольной суммы и выходом ошибки устройства, первый триггер, информационный вход 10 которого является входом режима контроля устройства, а выход соединен с входам первого одновибратора, выход которого подключен к счетному входу счетчика количества обращений, второй однавибра тар, о т л и ч а ю щ е е с я тем, то, с цель:а повышения быстродействия, в него введены второй, третий и четвертый элементы ИЛИ,первый и второй элементы задержки, второй и третий триггеры, сумматао па мо дулю два, причем первый вход первого элемента ИЛИ является входом обращения устройства, выход первого элемента ИЛИ соединен с входом выборки блока памяти обращений, выход которого подключен к 25 первому входу сумматора па модулю два, второй вход которого соединен с информа, ционным входом блока памяти обращений и с выходом второго триггера, Р-вход которого подключен к Я-входу третьего тригге- ЗО ра, входам начальной установки счетчика адреса, счетчика количества обращений и накапливающего сумматора, первому входу второго элемента ИЛИ и является входом начальной установки устройства, выход 35 сумматора по модулю два соединен с вторым входом элемента ИЛИ, вторыми входами элементов И группы, синхровходом первого триггера и входом второго одновибраторавыход которого подключен к второму входу второго элемента ИЛИ, выход которого соединен с входом сброса первого триггера, информационные входы счетчика количества обращений являются входами количества обращений устройства, а выход переполнения счетчика количества обращений подключен к управляющему входу блока сравнения и первому входу четвертого элемента ИЛИ, выход которого соединен со счетным входом первого триггера и входом обнуления накапливающего сумматора, вход записи блока памяти обращений подключен к выходу третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого одновибрзтора и первого элемента задержки, вход которого подключен к третьему входу первого элемента ИЛИ и выходу второго элемента И, первый вход которого является тактовым входом устройства и соединен с входом второго элемента задержки, выход которого подключен к первому входу первого элемента И, второй вход которого соединек с вторым входом второго злементз И, управляющим входом коммутатора и выходом третьего триггера, В-вход которого подключен к второму входу четвертого элемента ИЛИ и выходу счетчика адреса, счетный вход которого соединен с выходом первого элемента И,1709395 Составитель В. ФараджеьПчолинская Текред М.Моргентал Коррект оро каз 430 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва Ж, Раущская наб 4/5 изводственно-,издательский комбинат Патент", г, Ужгород, ул.Га 10

СмотретьЗаявка

4464819, 21.07.1988

ПРЕДПРИЯТИЕ ПЯ В-2655

КАЧАНКО ОЛЕГ ИВАНОВИЧ, ФАРАДЖЕВ ВАЛЕНТИН АЛЕКСАНДРОВИЧ, СИГАЛОВ ИСАЙ ЛЬВОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: блоках, обнаружения, ошибок, памяти, программ

Опубликовано: 30.01.1992

Код ссылки

<a href="https://patents.su/4-1709395-ustrojjstvo-dlya-obnaruzheniya-oshibok-v-blokakh-pamyati-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок в блоках памяти программ</a>

Предыдущий патент: Устройство для формирования адресов регенерации динамической памяти

Следующий патент: Оперативное запоминающее устройство с коррекцией ошибок

Случайный патент: Устройство для репродукции цветных оригиналов