Система передачи и приема дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1119184

Авторы: Бондаренко, Журавлев

Текст

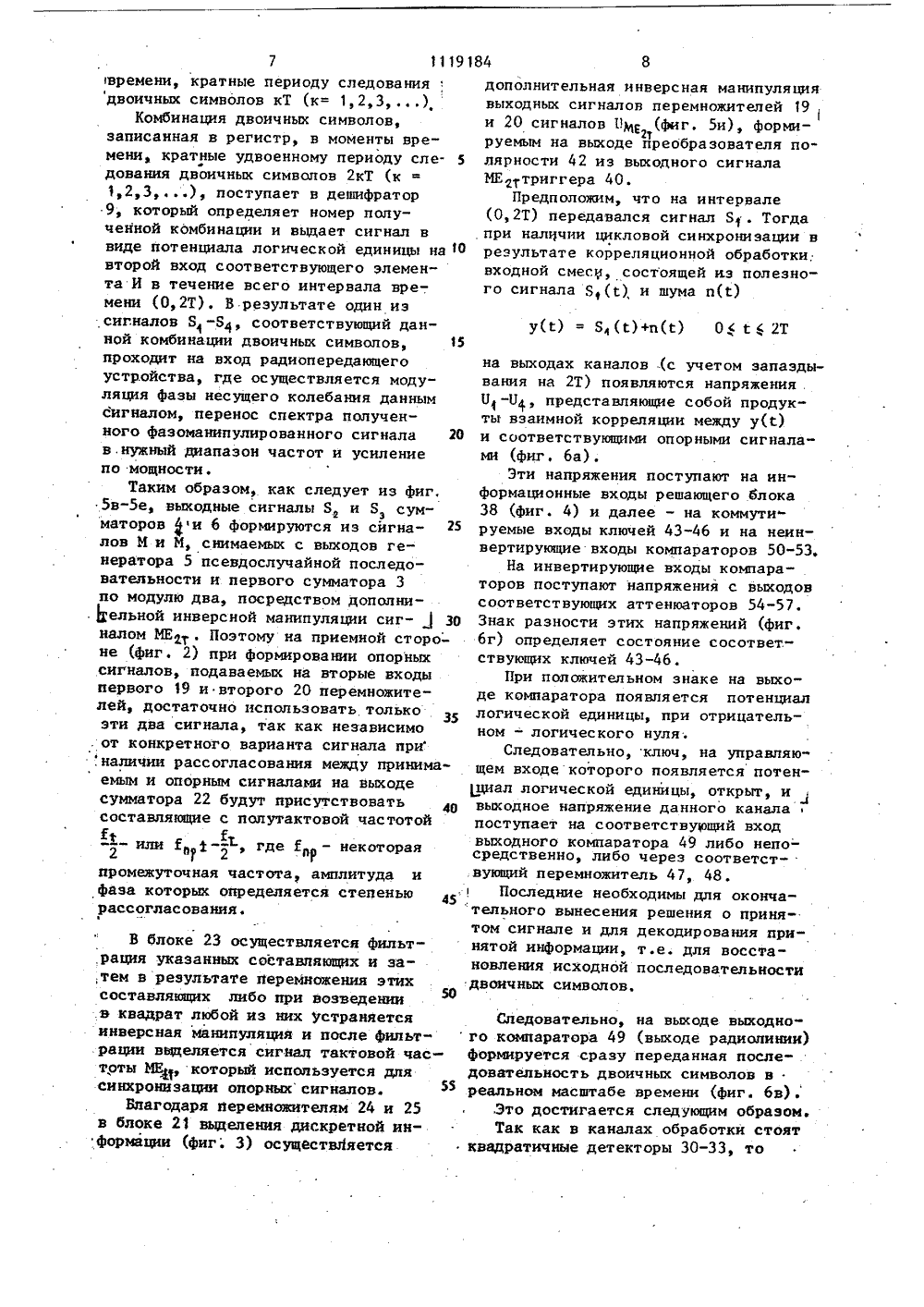

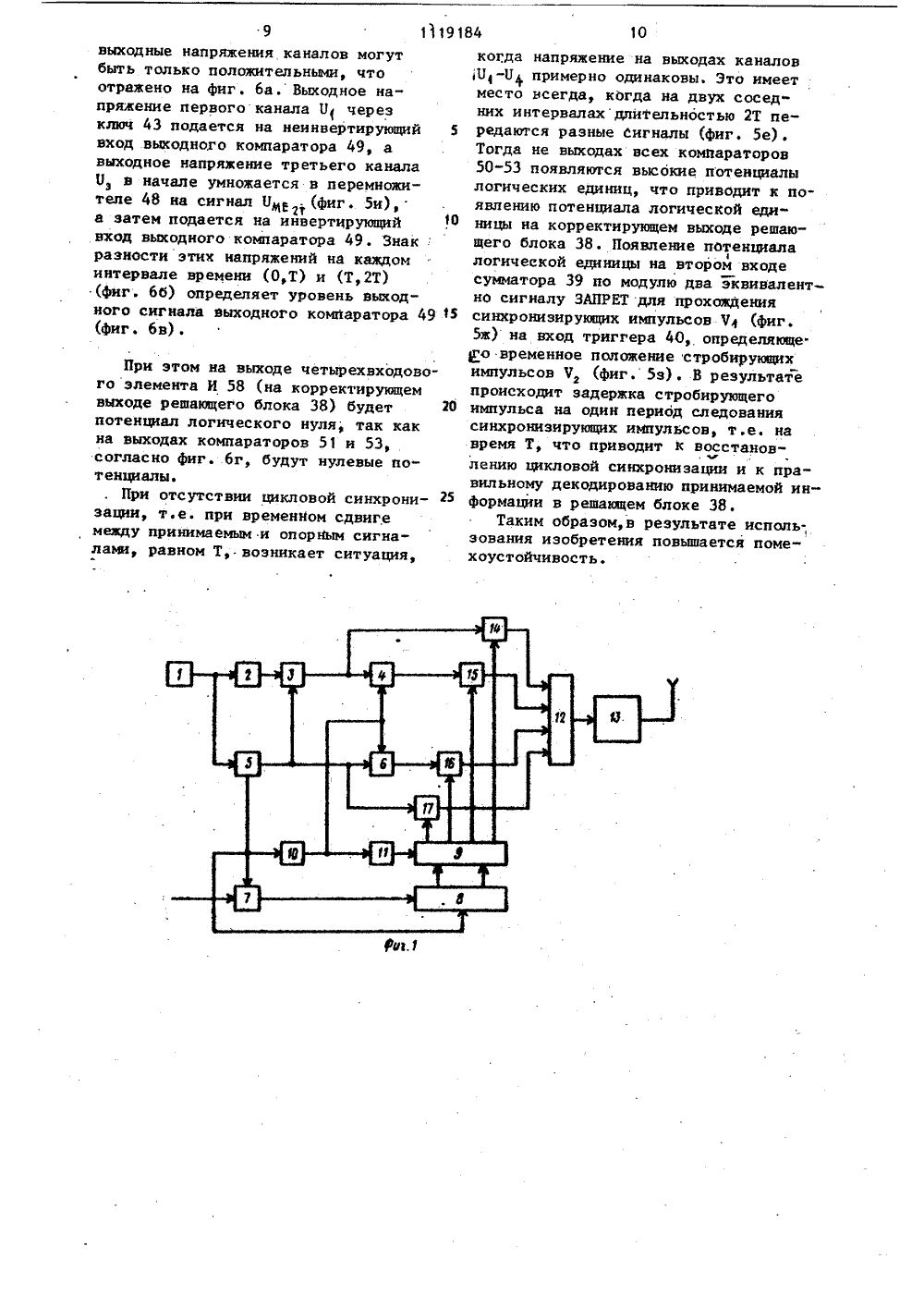

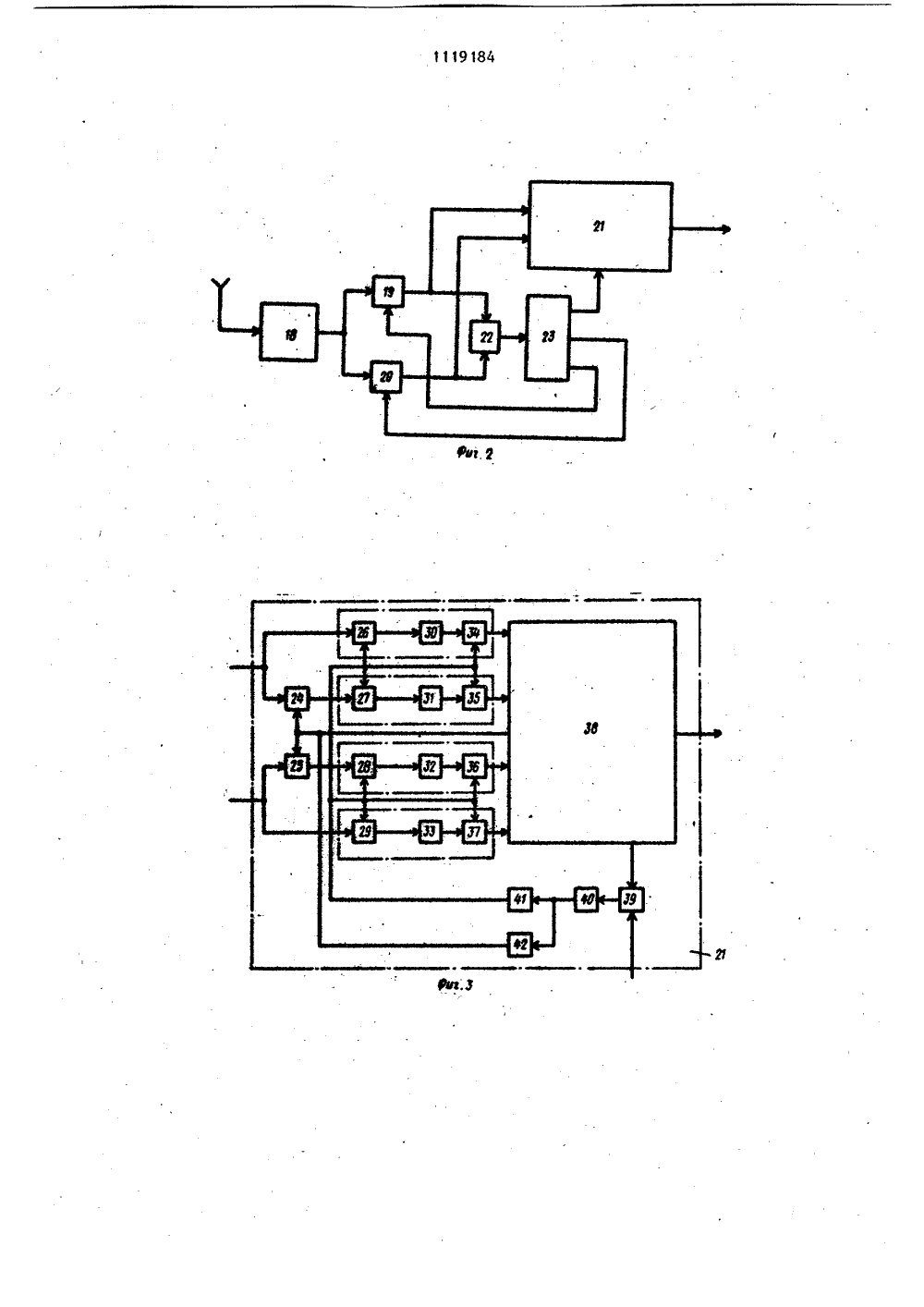

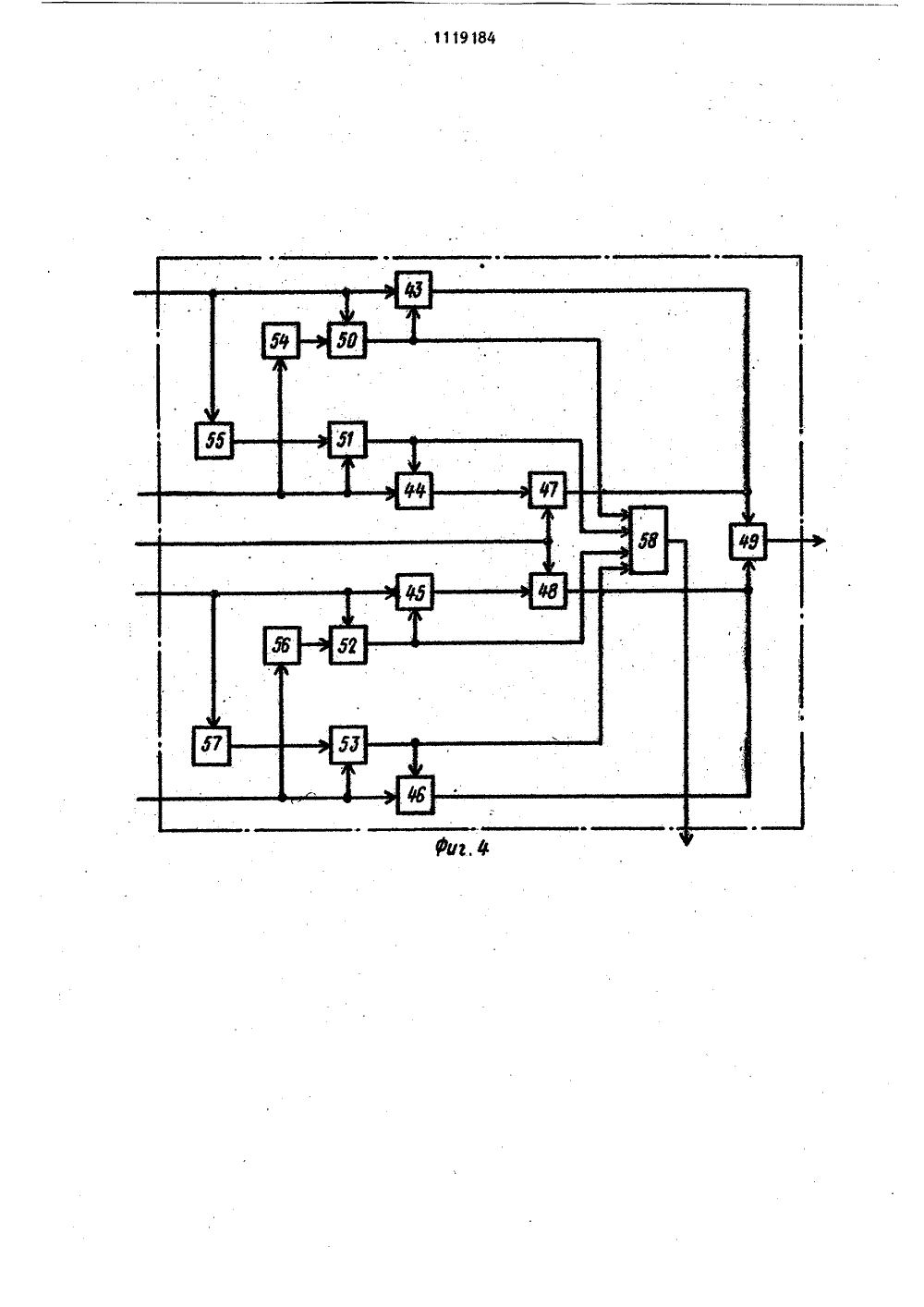

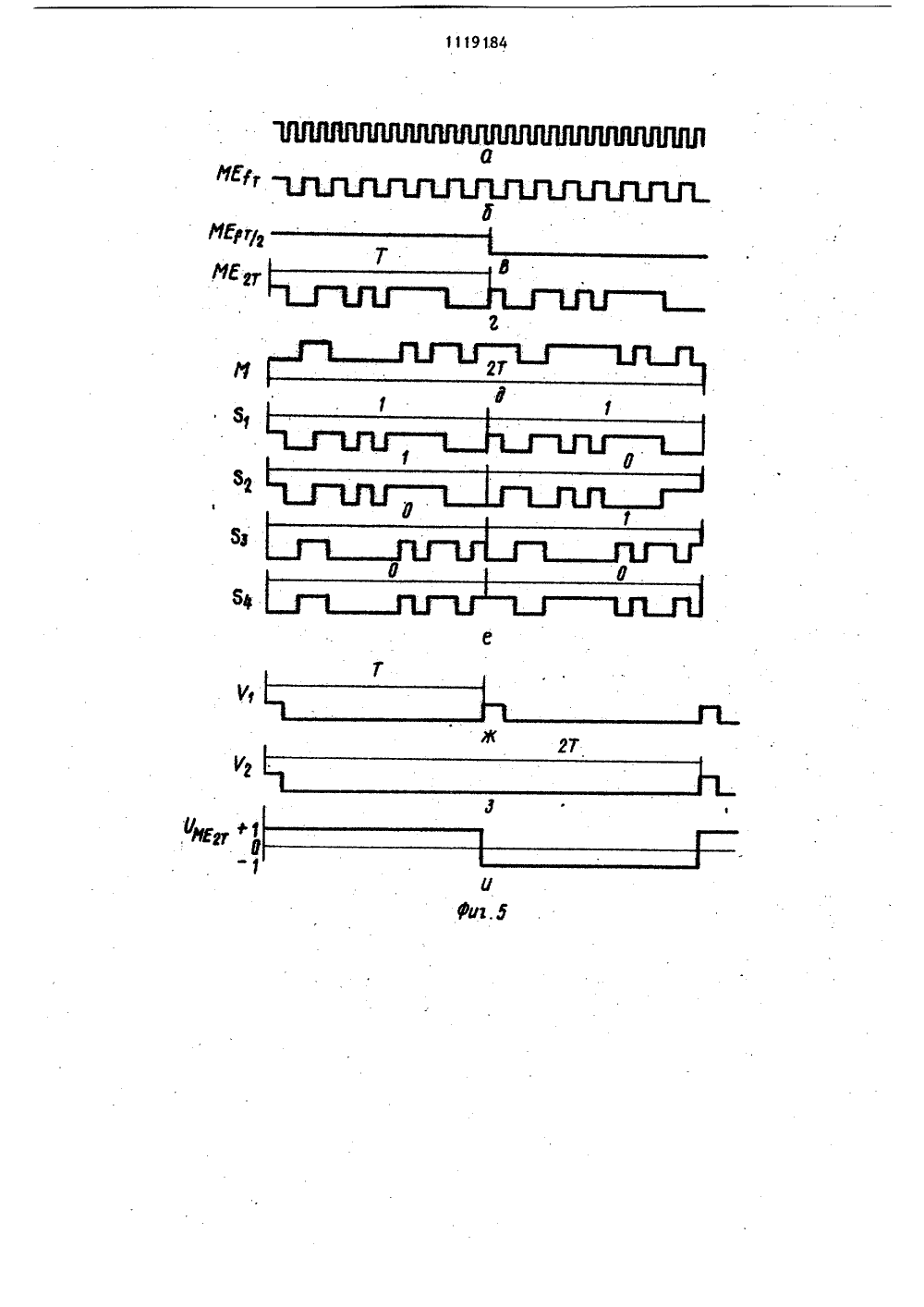

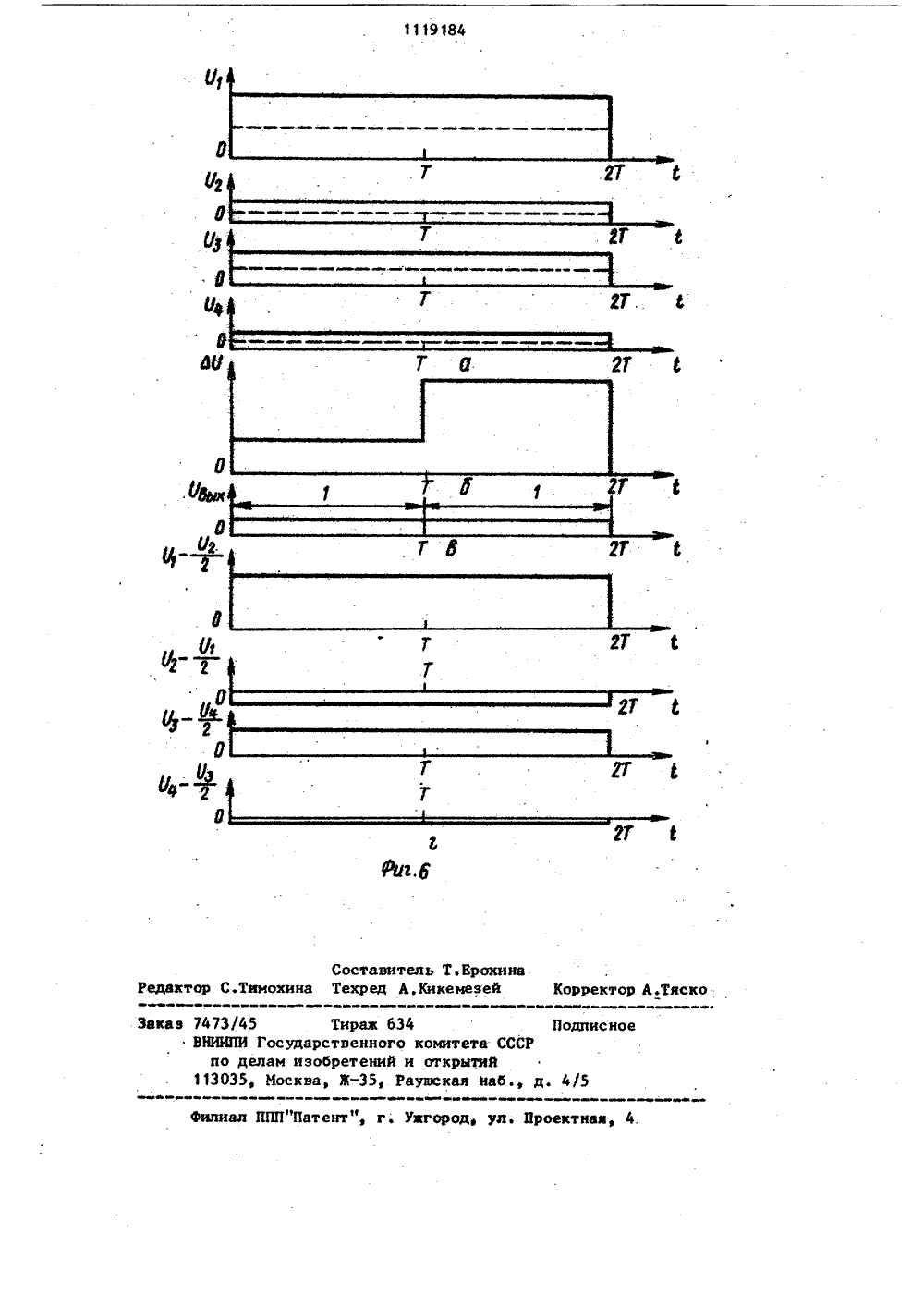

- (72) С,С.Бондаренко и В.И.Журавлев (71) Московский ордена Трудового Красного Знамени электротехнический институт связи(56) 1. Авторское свидетельство СССР В 930719, кл. Н 04 Ь 5/02, 19822, Статистическая теория связи и ее приложения. Под. ред. Балакришпана. М., "Мир", 1962, с. 139-140 (прото" тип).(54)(57) 1. СИСТЕМА ПЕРЕДАЧИ И ПРИЕ" МА ДИСКРЕТНОЙ ИНФОРМАЦИИ, содержащая на передающей стороне последовательно соединенные генератор тактовой частоты, генератор псевдослучайной последовательности и первый и второй сумматоры по модулю два, а также синхронизатор и передатчик, причем первый вход синхронизатора является информационным входом, а второй вход является синхронизирующим и сое динен со вторым выходом генератора псевдослучайной последовательности, а на приемной стороне - приемник, вы ход которого подключен к первым входам первого и второго перемножителей, вторые входы которых соединены соответственно с первым и вторым выходами блока выделения синхропараметра и формирования опорных сигналов, третий выход которого подключен к синхронизирующему входу блока выделения дискретной информации, информационный вход которого соединен с выходом первого перемножителя о т л и ч а ю щ а я с я тем, что,целью повьппения помехоуст заэ Н 04 В 7/24 Н 04 1. 27/ 0 в нее введены на передающеи стороне первый триггер, включенный между выходом генератора тактовой частоты и входом первого сумматора по модулю два, последовательно соединенные двух- разрядный регистр сдвига и дешифратор, элемент ИЛ , четыре элемента И, второй триггер, третий сумматор по модулю два и формирователь стробирующих импульсов, причем выходы первого, второго и третьего сумматоров по модулю два и первый выход генератора псевдослучайной последовательности через соответствующие элементыподключены к соответствующим вхо=дам элемента ИЛИ, выход которого под Е .ключен к передатчику, причем первый выход генератора псевдослучайной последовательности также подключен к первому входу третьего сумматора по модулю два, второй выход гене- О ратора псевдослучайной последовательности подключен ко входам второго триггера и двухразрядного ре-гистра сдвига, информационный вход которого соединен с выходом синхро.низатора, причем выход второго триггера подключен ко вторым входам второго и третьего сумматоров по модулю два и через формирователь стробирующих импульсов соединен с управ- ляющим входом дешифратора, выходы которого подключены ко вторым входам соответствующих элементов И, а на ф приемной стороне введены сумматор, входы которого соединены с выходами первого и второго перемножителей, а выход подключен ко входу блока вы деления синхропараметра и формирования опорных сигналов,.при этом выход второго перемножителя также1119184 Фи Составитель Т. ЕрохинаРедактор С.Тимохина Техред А,Кнкемевей Корректор АЛяс одписное 4 5 Патент", г Умгород роектная, 4 ал Заказ 7473(45 ВНИИПИ Госуда по делам из 113035, Иоскв111 подключен ко второму информащонному входу блока вьделения дискретной информации. 2. Система по п, 1, о т л и ч а ющ а я с я тем, что блок выделения дискретной информации вьаолнен в виде четырех идентичных каналов каждый из которых содержит последоватеньно соединенные интегратор квадратичный детектор и блок выборки и хранения информации, причем выходы блоков выборки и хранения информации всех .каналов подключены к информационным входам решающего блока, первый выход которого является выходом блока вы- деления дискретной информации, а ко второму выходу подключен первый вход сумматора по модулю два, выход кото" рого через последовательно соединен" ные триггер и формирователь стробирующих импульсов подключен к первым вхо,дам интеграторов и ко вторым входам блоков выборки и хранения информации всех каналов, причем к выходу триггера также поДключен вход преобразователя нолярности,к выходу которого подключены управляющий вход решающего блока и первые входы пер- . вого и второго перемножителей, выходы которых подключены соответственно ко вторым входам интеграторов второго и третьего каналов, вторые входы первого и ,второго перемножителей соединены соответственно со вторыми входами интеграторов первого и четвертого каналов и являются соот 9184ветственно первым и вторым информационнымн входамй блока выделения дискретной информации, а второй вход сумматора по модулю два является синхронизирующимвходом блока выделе" ния дискретной информации.3. Система по и. 2 о тл и, ч а ю"щ а я с я тем, что решающий блок выполнен в виде четырех каналов, каждый из которых содержит последовательно соединенные аттенюатор, компара" тор .и ключ, причем к выходам компараторов всех, каналов также подключены соответствующие входы четырехвходового элемента И, выход которого является вторым выходом решающе,го блока, к выходам ключей первого и четвертого каналов подключены соответственно первый и второй входы выходного компаратора, к которым также через соответствующие перемножители подключены выходы ключей второго н третьего каналов, выход выход ного компаратора является первым выходом решающего блока, вторые входы компаратора и ключа каждого канала объединеныи являются соответствующим информационным входом решающего блока, вторые входы первого и второго перемножителей объединены и являются управляющим входом решающего блока, причем входы аттенюаторов пер.. вого, второго, третьего и четвертого каналов соединены соответственно со вторым, первым, четвертым и третьим информационными входами решающего блока.1Изобретение относится к технике связи, преимущественно широкополосным системам, и может быть использо вано в радиоуправлении.Известна широкополосная система, 5 в которой для вьделения двоичной информации, передаваемой при помощи ортогональных сигналов, применяются корреляционные устройства, содер- . жащие блок вьделения синхропара метра и формирования опорных сигналов, и блок выделения информации ЦОднако помехоустойчивость систем, использующих ортогональные сигналы 3для передачи двоичной информации, в некоторых случаях оказывается недостаточной.Наиболее близким техническим решением к данному изобретению, является система передачи и приема дискретной информации, содержащая на передающей стороне последовательно соединенные генератор тактовой частоты, генератор псевдослучайной последовательности и первый И второй сумматоры по модулю два, а также синхронизатор и передатчик, причемпервый вход синхронизатора являет3 1119 ля информационным входом, а второй вход является синхронизирующнм и сое динен со вторым выходом генератора псевдослучайной последовательности, а на приемной стороне - приемник выф 5 ход которого подключен к первым входам первого и второго перемножителей, вторые входы которых соединены соответственно с первым и вторым выходаьм блока выделения синхропара О метра и формирования опорных сигна.лов, третий выход которого подключен к синхронизирующему входу блока выделения дискретной информации, информационный вход которого соединен с вы-: 15 ходом первого перемножителя 2 .Однако реальная помехоустойчивость такой системы передачи и приема дискретной информацйи невысока.Цель изобретения - повышение помехоустойчивости.Для достижения указанной цели в систему передачи и приема дискретной информации, содержащую на передающей стороне последовательно соединенные25 генератор тактовой частоты, генератор псевдослучайной последовательности и первый и второй сумматоры по модулю два, а также синхронизатор и передатчик, причем первый вход синхронизаЗО тора является информационным входом, а второй вход является синхронизирующим и соединен со вторым выходом генератора псевдослучайной последовательности, а на приемной стороне - 35 приемник, выход которого подключенк первым входам первого и второго перемножителей, вторые входы которых соединены соответственно с первым и вторым выходами блока выцелення син О хропараметра и формирования опорных сигналовтретий выход которого подключен к синхрониэирующему входу блока выделения дискретной информации, информационный вход которого соеди нен с выходом первого перемножителя введены на передающей стороне первый триггер, включенный между выходом генератора тактовой частоты и входом первого сумматора по модулю 50 два, последовательно соединенные двух разрядный регистр сдвига н дешифратор,. элемент ИЛИ, четыре элемента И, второй триггер, третий сумматор по модулю два и формирователь строби ,рующих импульсов, причем выходы первого, второго и третьего суМматоров по модулю два и первый выход гене 184 4ратора псевдослучайной последовательности через соответствующие элементы И подключены к соответствующим входам элемента ИЛИ, выход которого подключен к передатчику, причем первый выход генератора псевдослучайной последовательности также подключен к первому входу третьегО сумматора по модулю два, второй выход генератора псевдослучайной последовательности подключен ко входам второго триггера и двухразрядного регистра сдвига, информационный вход которого соединен с выходом .синхронизатора, причем выход второго триггера подключен ко вторым входам второго и третьего сумматоров по модулю два и через формирователь стробирующих импульсов соединен с управляющим входом дешифратора, выходы которого подключены ко вторым входам соответствующих элементов И, а на приемной стороне введен сумматор, входы которого соединены с выходами первого и второго перемножителей, а выход подключен ко входу блока выделения синхропараметра н формирования опорньж сигналов, при этом выход второго перемножителя также подключен ко второму информационному входу блока выделения дискретной информации. Блок выделения дискретной информа. .ции выполнен в виде четырех идентичных каналов, каждый из которых содержит последовательно соединенные интегратор, квадратичный детектор и блок выборки и хранения информации, причем выходы блоков выборки и хранения информации всех каналов подклю чены к информационным входам решающего блока, первый выход которого является выходом блока выделения дискретной информации, а ко второму выходу подключен первый вход сумматора по модулю два, выход которого через последовательно соединенные триггер и формирователь стробирующих импульсов подключен к первым входам интеграторов и ко вторым входам блоков выборки и хранения информации всех каналов, причем к выходу триггера также подключен вход преобразователя полярности, к выходу которого подклю. чены управляющий вход решающего блока и первые входы первого и второго перемножителей, выходы которых подключены соответственно ко вторым входам интеграторов второго н тре1 О На фиг, 1. представлена структурная электрическая схема передающей час" ти системы передачи и приема дискретной информациирна фиг, 2 -структурная электрическая схема приемной45 ,.части системы передачи и приема дискретной информацииф на фиг. 3 - струк турная схема блока выделения дискрет"ной информации; на фиг, 4 - структурная схема решающего блокаф, на Фиг. 5 и 6 - временные диаграммы, поясняющие работу системы.Устройство передачи и приема дискретной информации содержит на передающей сгороне генератор 1 тактовой частоты, первый триггер 2, первый сумматор 3 по модулю.два,второй сумматор 4 по модулю два, генератор 5 5 1119 тьего каналов вторые входы первого и второго перемножителей соединены соответственно со вторыми входами интеграторов первого и четвертого каналов и являются соответственно пер-, 5 вым и вторым информационными входами блока выделения дискретной информации, а второй вход сумматора по медулю два является синхронизирующим входом блока выделения дискретной информации.Решающий блок выполнен в виде четырех каналов, каждый из которыхсодержит последовательно соединенные рттенюатор, компаратор и ключ, при чем к выходам компараторов Всех каналов также подключены соответствующие входы четырехвходового элемента И, выход которого является вторым выходом решающего блока, к выходам 20 ключей первого и четвертого каналов подключены соответственно первыйЧ1 и второи входы выходного компаратора, к которым также через соответствующие перемножители.подключены выходы ключей25 второго и третьего канапов, выход выходного компаратора является первым выходом решающего блока, вторые входы компаратора и ключа каждого канала объединены и являются соответствуюЗО щим информационным входом решающего блока, вторые входы первого и второго перемножителей объединены и являются управляющим входом решающего бло. ка, причем входы аттенюаторов перво го, второго,третьего и четвертого . каналов соединены соответственно со вторым, первым, четвертым и третьим информационными входами решающего блока. псевдослучайной последовательности, третий сумматор 6 по модулю два, синхронизатор 7, двухразрядный регистр сдвига 8,дешифратор 9, второй триггер 10, формирователь 11 стробирующих импульсов, элемент ИЛИ 12, передатчик 13, элементы И 14-17, а на приемной стороне - приемник 18, первый перемножитель 19, второй перемножитель 20, блок 21 выделения дискретной информации, сумматор 22блок 23 выделения синхропараметра и формирования опорных сигналов.Блок 21 выделения дискретной информации содержит первый и второй перемножители 24 и 25, интеграторы 26-29, квадратичные, детекторы 30-33, блоки 34-37 выборки и хранения ин" Формации, решающий блок 38, сумматор 39 по модулю два, триггер 40, фор" мирователь 41 стробирующих импульсов, преобразователь 42 полярности,Решающий блок 38 содержит ключи 3-46, перемножители 47-48 выходной компаратор 49, компараторы 50-53, аттенюаторы 54-57, четырехвходовый элемент И 58. Система передачи и приема дискретной информации работает следующим образом.Сигнал тактовой частоты МЕ, (фиг.5 аб) с выхода генератора 1 одновременно поступает на входы первого триггера 2 и генератора 5 псевдослучайной последовательности, на входах которых Формируются сигналы М (меандр полутактовой частоты)1 М (ш ф последовательность) и Ч (сигнал синхронизации двоичных символов, поступающих на вход синхронизатора 7). Сигнал Ч также поступает на вход второго триггера 10, на выходе которого Формируется сигнал МЕ 2- (меЙТ андр с периодом, равным удвоенному периоду следования двоичных символов).В результате операнд суммирования по модулю два сигналов М, МЕ и МЕ. на выходах сумматоров 3, 4,образуются,три различных сигнала с периодом 2 Т.В сочетании с сигналом М они образуют ансамбль из четырех ортого нальных сигналов с периодом 2 Т (фиг, 5 е). Двоичные символы "1" и "0", пос тупающие на основной вход синхронизатора 7, записываются в двухразрядный регистр сдвига 8 в моменты7 1119184 8времени, кратные периоду следованиядополнительная инверсная манипуляциядвоичных символов кТ (к= 1,2,3,) выходных сигналов перемножител " 19еиКомбинация двоичных символов, и 20 сигналов Бь 1 (фиг. 5 и), Формизаписанная в регистр, в моменты вре- руемым на выходе йреобразователя помени, кратные удвоенному периоду сле лярности 42 из выходного сигналадования двоичных символов 2 кТ (к МЕ триггера 40.123 )гт,), поступает в дешифратор Предположим, что на интервале9, который определяет номер полу- (0,2 Т) передавался сигнал Б 1 . Тогдаченной комбинаомбинации и выдает сигнал в при наличии цикловой синхронизации ввиде потенциала логической единицы на 10 результате корреляционной обработки,второй вход соответствующего элемен- входной смеси, состоящей из полезнота И в течение всего интервала вре- го сигнала Б(е) и шума п(й)мени (0,2 Т). В результате один изсигналов Б-Б 4, соответствующий дан- у(с) = Б(с)+пИ) 0 ( е ( 2 Тной комбинации двоичных символов, 15проходит на вход радиопередающего на выходах каналов -(с учетом запаэдыустройства, где осуществляется моду- вания на 2 Т) появляются напряженияляция фазы несущего колебания данным 0,1-11, представляющие собой продуксигналом, перенос спектра получен- тй взаимной корреляции между у(0ного Фазоманипулированного сигнала 20 и соответствующими опорными сигналав.нужный диапазон частот и усиление мн (Фиг, ба).по мощности. Эти напряжения поступают на ин 5 веТаким образом, как следует из фиг, формационные входы решающег 6о л окав- е, выходные сигналы Б и Б сум (Фиг. 4) и далее - на коммутиматоров и 6 Формируются из сйгна руемые входы ключей 43-46 и на неинлов М и М, снимаемых с выходов ге- вертирующие входы компараторов 50"53.нератора 5 псевдослучайной последо- На инвертирующне входы компаравательности и первого сумматора 3 торов поступают напряжения с выходов.ел н"по модулю два, посредством дополни- соответствующих аттенюаторов 54-57.ельной инверсной манипуляции сиг-30 Знак разности этих напряжений (Фиг.кадом МЕ . ППоэтому на приемнои сторо- бг) определяет состояние сосответ. -.ие (Фиг. 2) при формировании опорных ствующих ключей 43-46.сигналов, подаваемых на вторые входы При положительном знаке на выхопервого 19 и вто ого 20 п ер о 20 перемножите- де комнаратора появляется потенциаллей, достаточно использовать тольковать. тольк З логической единицы, при отрицательэти два сигнала, так как независимо ном - логического нуля., от конкретного варианта сигнала при Следовател нледовательно, ключ, на управляю.наличии рассогласования м ежду принима- щем входе которого появляется потенемым и опорным сигиалаии на выходе 1 циал логической единицы, открыт, исумматора 22 будут присутствоватьЬ й й40 выходное напряжение данного каналасоставляющие с полутактовой частотой поступает на соответствующий вход-- или Ец 1 - ., где Г- некотораявыходного компаратора 49 либо непо-2 вР 2 ф . оР оР Я средственно, либо через соответстпромежуточная частота, амплитуда и вующий перемножитель 47, 48.фаза которых определяется степенью 4 . Последние необходимы для окончарассогласования. тельного вынесения решения о принятом сигнале и для декодирования приВ блоке 23 осуществляется Фильт- нятой информации, т .е. для восстарация указанных составляющих и за- я исходнои последовательности,тем в результаге перемножения этих двоичных символов,составляющих либо при возведении.э квадрат любой из них устраняется Следовательно, на выходе выходноинверсная манипуляция и после Фильт-го компаратора 49 (выходе радиолинии)рацИи ввщеляется сигнал тактовой час- формируется сразу переданная послетоты МЕ, который используется для довательиость двоичных символов всинхронизации опорныхсигналов. реальном масштабе времени (Фиг. бв).Бпагодаря перемножителям 24 и 25 ,Это достигается следующим образом,в блоке 21 выделения дискретной ик- Так как в каналах обработки стоятформации (Фиг. 3) осуществляется квадратичные детекторы 30-33, товыходные напряжения каналов могутбыть только положительными, чтоотражено на фиг. ба. Выходное напряжение первого канала 01 черезключ 43 подается на неиннертирующий 5вход выходного компаратора 49, авыходное напряжение третьего каналаО в начале умножается в перемножителе 48 на сигнал 0 (фиг. 5 и),а затем подается на ийвертирующийвход выходного компаратора 49. Знакразности этих напряжений на каждоминтервале времени (О,Т) и (Т,2 Т)(фиг. бб) определяет уровень выход"ного сигнала выходного компаратора 49 15(фиг, бв). При этом на выходе четырехвходовогоэлемента И 58 (на корректирующем выходе решающего блока 38) будет 20 потенциал логического нуля, так как на выходах компараторов 51 и 53, согласно фиг. бг, будут нулевые потенциалы.При отсутствии сикловой синхрони зацни, т.е. при временном сдвиге между принимаемым и опорным сигналами, равном Т, возникает ситуация,когда напряжение на выходах каналовДпримерно одинаковы. Это имеетместо всегда, кдгда на двух сосед"них интервалахдлительностью 2 Т передаются разные сигналы (фиг. 5 е).Тогда не выходах всех компараторов50-53 появляются высокие потенциалылогических единиц, что приводит к появлению потенциала логической единицы на корректирующем выходе решающего блока 38 . Появление потенциалалогической единицы на втором входесумматора 39 по модулю два эквивалентно сигналу ЗАПРЕТ для прохождениясинхронизирующих импульсов 7 (фиг,5 ж) на вход триггера 40, определяюще.;о временное положение стробирующихимпульсов 7 (фиг . 5 з) . В результатепроисходит задержка стробирующегоимпульса на один период следованиясинхронизирующих импульсов, т.е, навремя Т, что приводит к восстановлению цикловой синхронизации и к правильному декодированию принимаемой информации в решавзцем блоке 38.Таким образом,в результате исполь;зования изобретения повышается помехоустойчивость,

СмотретьЗаявка

3589616, 05.05.1983

МОСКОВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

БОНДАРЕНКО СЕРГЕЙ САВЕЛЬЕВИЧ, ЖУРАВЛЕВ ВАЛЕРИЙ ИВАНОВИЧ

МПК / Метки

МПК: H04B 7/24

Метки: дискретной, информации, передачи, приема

Опубликовано: 15.10.1984

Код ссылки

<a href="https://patents.su/10-1119184-sistema-peredachi-i-priema-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи и приема дискретной информации</a>

Предыдущий патент: Приемо-передающее устройство замкнутой адаптивной системы тропосферной связи

Следующий патент: Обнаружитель активности канала в системе с дельта модуляцией

Случайный патент: Устройство для прорезания щелей во льдуводоемов