Преобразователь двоично-десятичной дроби в двоичную дробь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 826335

Автор: Омельченко

Текст

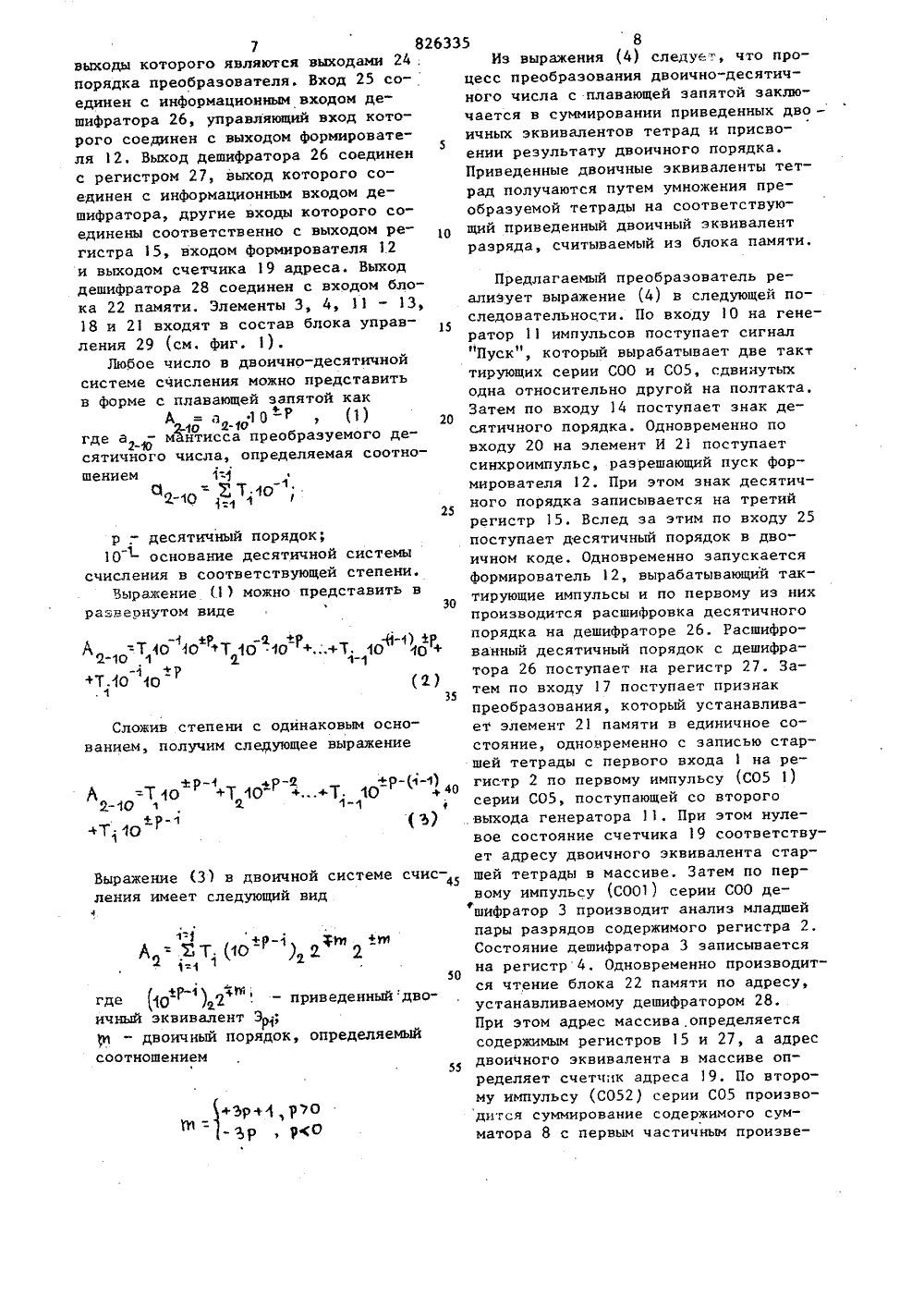

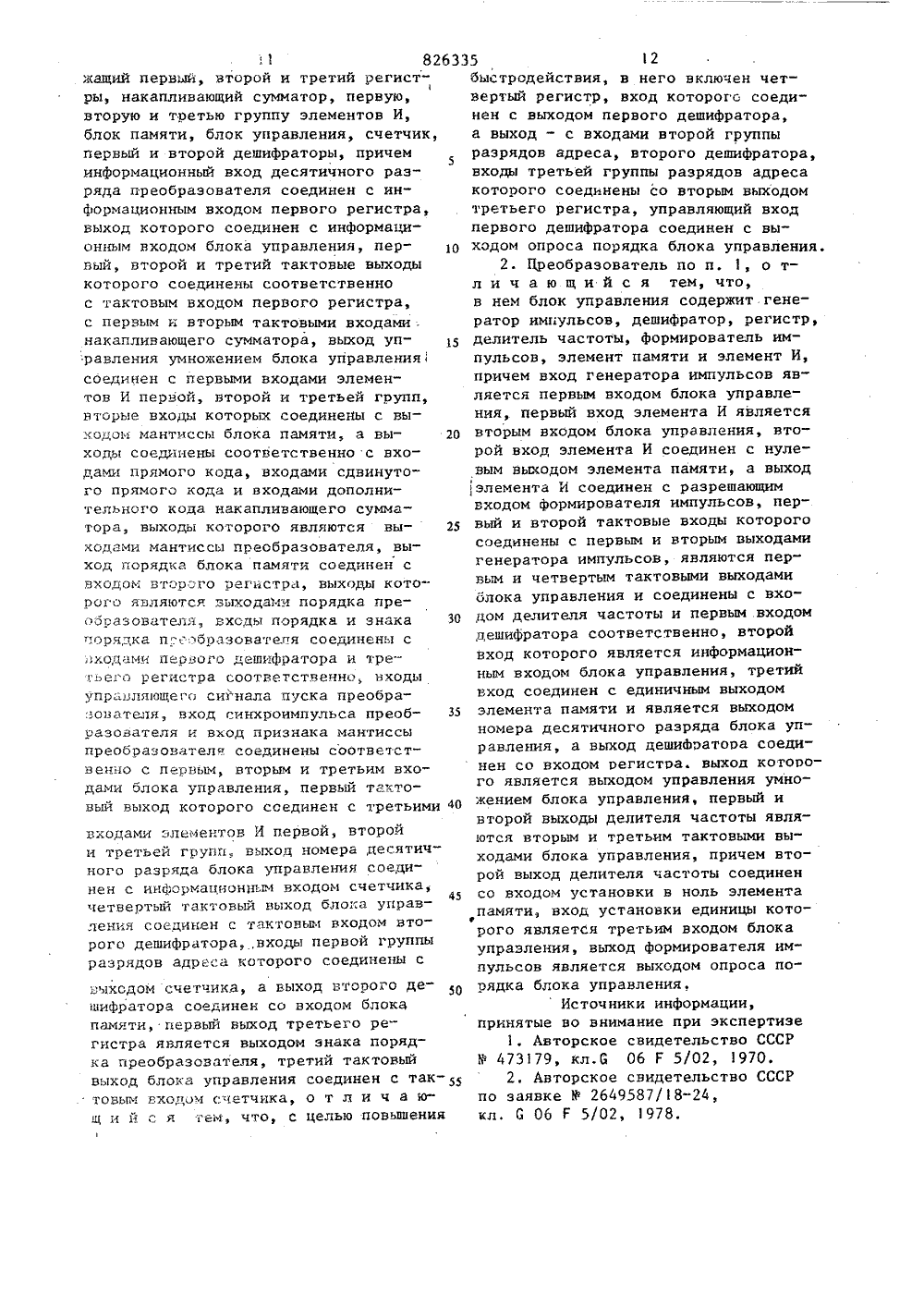

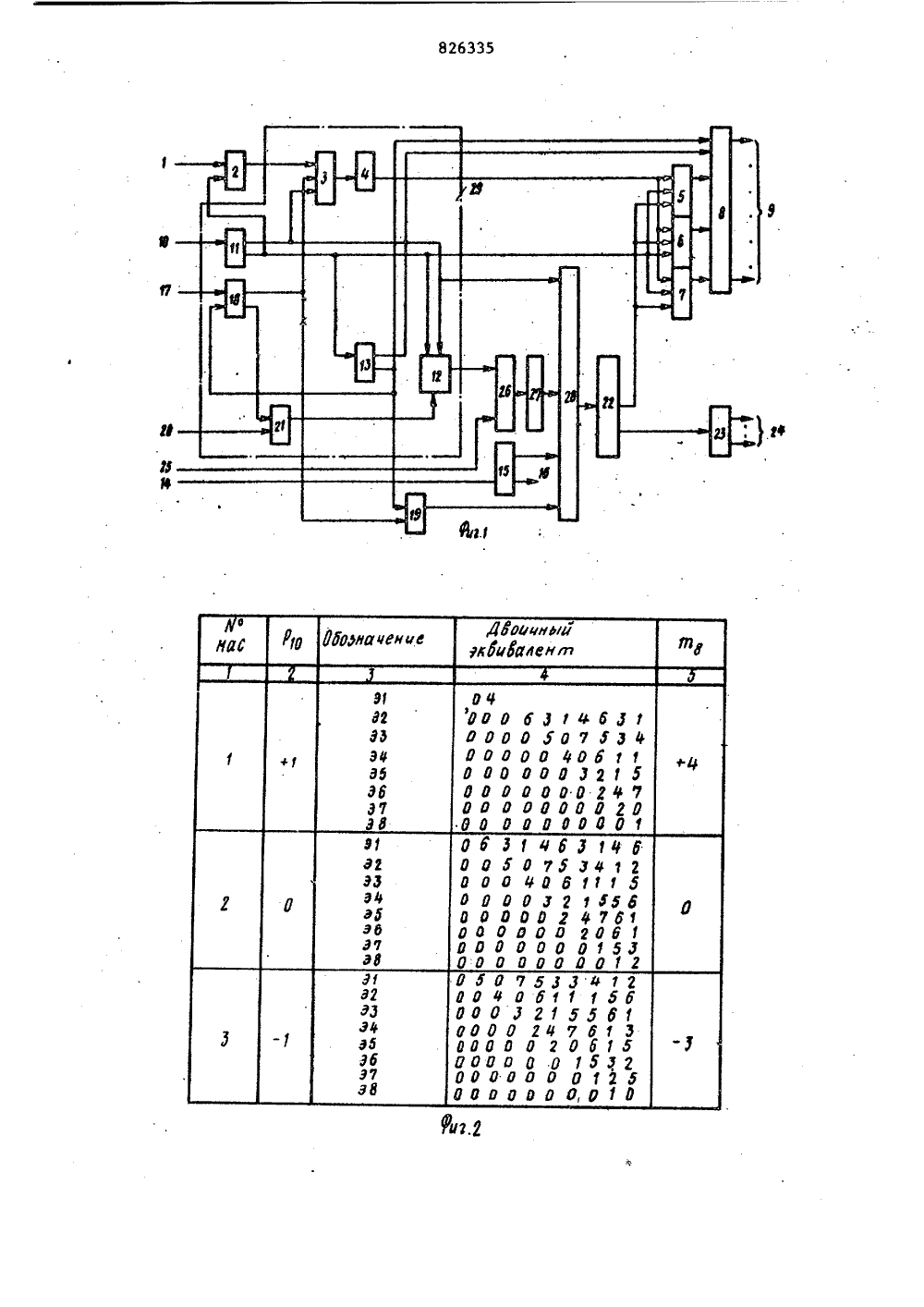

Сфез СфветскикСфциапистическмаРеспубпик ОП ИСАНИЕИЗОБРЕТЕН Ия(51)М. Кл. с присоединением заявки М 6 06 Г 5/02 ввуаарстввввй квюитвт СССР в дваан взвбрвтвиий и етврытвйИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей.Известен преобразователь двоичнодесятичного кода в двоичный код, содержащий регистр числа, блок управления, переключатель эквивалентов, рас" пределитель импульсов, блок памяти, формирователь двоичного эквивалента10 тетрады, регистр сдвига н двоичный сумматор 1 .Недостаток этого устройства состоит в том, что оно преобразует либо смешанные, либо дробные числа и не15 преобразует десятичные числа с отрицательным порядком.Наиболее близким к предлагаемому по технической сущности и схемному решению является преобразователь дво" ичко-десятичной дроби в двоичную дроб, содержащий первый, второй и третий регистры, накапливающий сумматор, первую, вторую и третью группу 2элементов И, блок памяти, блок управления, счетчик, первый и второй дешифраторы, причем информационный вход десятичного разряда преобразователя соединен с информационным входом первого регистра, выход которого соединен с информационньк входом блока управления, первый, второй и третий тактовые выходы которого соединены соответственно с тактовым входом первого регистра, с первым и вторым тактовыми входами накапливающего сумматора,выход управления умножением блока управления соединен с первыми входами элементов И первой, второй и третьей групп, вторые входы которых соединены с выходом мантиссы блока памяти, а выходы соединены соответственно с входами прямого кода, входами сдвинутого прямого 1 сода и входами дополни" тельного кода накапливающего сумматора, выходы которого являются выходами мантиссы преобразователя, выход порядка блока памяти соединен с входом6335 ф 10 50 55 3 82второго регистра, выходы которогоявляются выходами порядка преобразователя, входы порядка и знаки порядка преобразователя соединены с входами первого дешифратора и третьегорегистра соответственно, входы управ"ляющего сигнала пуска преобразователя, вход синхроимпульса преобразователя и вход признака мантиссы соедини соответственно с первым, вторыми третьим входами блока управления,первый тактовый выход которого соединен с третьими входами первой, вто-,рой и третьей групп элементов И, вы-ход номера десятичного разряда блокауправления соединен с информационным,входом счетчика, четвертый тактовыйвыход блока управления соединен с тактовым входом второго дешифратора,входы первой группы разрядов адресакоторого соединены с выходом счетчикаа выход второго дешифратора соединенсо входом блока памяти, выход третьего регистра является выходом знакапорядка преобразователя, третий тактовый выход блока управления соединенс тактовым входом счетчика 2 1,Недостаток этого преобразователясостоит в относительно низком быстро действии, связанном .с наличием двухэтапов преобразования, на втором изкоторых при учете порядка десятичногочисла производится умножение полноразрядных чисел.Цель изобретения - повышение быстродействия преобразователя,Поставленная цель достигается тем, что в преобразователь двоично-десятичной дроби в двоичную дробь, содержащий первый, второй и третий регистры, накапливающий сумматор, первую, вторую и третью группу элементов И, блок памяти, блок управления, счетчик, первый и второй дешифраторы, причем информационный вход десятичного разряда преобразователя соединен с информационным входом первого регистра, выход которого соединен с информационным. входом блока управления, первый, второй и третий тактовые выходы ко- торого соединены соответственно с тактовым входом первого регистра, с первым и вторым тактовыми входами накапливающего сумматора, выход управления умножением блока управления соединен с первыми входами элементов И, первой, второй и третьей группы, вторые входы которых соединены с выходом 15 20 25 30 35 40 45 мантиссы, блока памяти, а выходы соединены соответственно с входами прямого кода, входами сдвинутого прямого кода и входами дополнительного коданакапливающего сумматора, выходы которого являются выходами мантиссы преобразователя, выход порядка блока памяти соединен с входом второго регистра, выходы которого являются выходами порядка преобразователя, входы порядка и знака порядка преобразователясоединены с входами первого дешифратора и третьего регистра соответственно, входы управляющего сигнала пускапреобразователя, вход синхроимпульсапреобразователя и вход признака мантиссы преобразователя соединены соответственно с первым, вторым и третьим входами блока управления, первыйтактовый выход которого соединен стретьими входами элементов И первой,,второй и третьей групп, выход номерадесятичного разряда блока управлениясоединен с информационным входом счетчика, четвертый тактовый выход блокауправления соединен с тактовым входомвторого дешифратора, входы первойгруппы разрядов адреса которого соединены с выходом счетчика, а выход второго дешифратора соединен совходом блока памяти, первый выход третьего регистра является выходом знакапорядка преобразователя, третий тактовый выход блока управления соединенс тактовым входом счетчика, в неговключен четвертый регистр, вход которого соединен с выходом первого дешифратора, а выход - с входами второй группы разрядов адреса второгодешифратора, входы третьей группы разрядов адреса которого соединены совторым выходом третьего регистра, управляющий вход первого дешифраторасоединен с выходом опроса порядка блока управления. А также тем, что в преобразователе двоично-десятичной дроби в двоичную дробь блок управления содержит генератор импульсов, дешифратор, регистр, делитель частоты, формирователь импульсов, элемент памяти и элемент И, причем вход генератора импульсов является первым входом блока управления, первый вход элемента И является вторым входом блока управления, второй вход элемента И соединен с нулевым выходом элемента памяти, а выход элемента И соединен с разрешаю5 8263щим входом формирователя импульсов,первый и второй тактовые входы которого соединены с первым и вторым выходами генератора импульсов, являют-.ся первым и четвертым тактовыми выхо 5дами блока управления и соединеныс входом делителя частоты и первымвходом дешифратора соответственно,второй вход которого является информационным входом блока управления,третий вход соединен с единичным выходом элемента. памяти и является выходом номера десятичного разрядаблока управления, а выход дешифратора соединен со входом регистра, выход которого является выходом управления умножением блока управления,первый и второй выходы делителя частоты являются вторым и третьим тактовыми выходами блока управления, причем второй выход делителя частотысоединен со входом установки в нольэлемента памяти, вход установки единицы которого является третьим входомблока управления, выход формировате зля импульсов является выходом опросапорядка блока управления.Ка фиг. 1 приведена блок-схема ;преобразователя; на фиг. 2 - таблица хранимых в блоке памяти эквивалентов що десятичных чисел; на фиг. 3 - пример преобразования числа 0,99999910".Предлагаемый преобразователь содержит информационный вход 1, регистр 2, дешифратор 3, регистр 4,группы элементов И 5-7., накапливающий сумматор 8, выходы 9 мантиссы, вход 10 управляющего сигнала пуска,генератор 11 импульсов, формирователь12 импульсов, делитель 13 частоты, 40вход 14 знака порядка, регистр 15, выход 16 знака порядка преобразовате- ля, вход 17 признака мантиссы, элемент 18 памяти, счетчик 19, вход 20 спнхроимпульса, элемент И 21, блок 22 4 З памяти, регистр 23, выходы 24 порядка, вход 25 порядка, дешифратор 26, регистр 27, дешифратор 28, блок 29 управления. 50Информационнья вход 1 служит для подачи очередной тетрады преобразуемой двоично-десятичной дроби и соединен с информационным входом первого регистра 2, выход которого соединен с информационным входом первого де" шифратора 3. Выход первого дешифратора 3 соединен со вторым регистром 4, хранящим результат анализа пары раз 35 6рядов преобразуемой теграды, Выход второго регистра 4 соединен с информа" ционньп 4 и входами первой, второй и третьей групп элементов И 5-7 для передачи множимого прямым кодом, пря,мым кодом со сдвигом влево на один разряд, дополнительным кодом. Выходы первой, второй и третьей групп элементов И 5-7 соединены соответственно с первыми, вторыми и третьими вхо" дами накапливающего сумматора 8, выходы которого являются первыми выхода ми 9 преобразователя, служащими для выдачи двоичной мантиссы, Вход 1 О служит для передачи пуска и соединен с генератором 11 импульсов, вырабатывающим две тактирующие серии СОО и С 05, сдвинутые одна относительно другой на полтакта, Первый выход генератора 11 (серия СОО) соединен с управляющим входом первого дешифра-. тора 3, с первым управляющим входом формирователя 12, второй управляющий вход которого соединен со вторым выходом генератора 11, а также с управляющим входом первого регистра 2, управляющими входами первой, второй и третьей групп элементов И 5-7, и входом делителя 13 частоты на два. Вход 14 служит для подачи знака деся" тичного порядка и соединен с регистром 15, выход которого является вторым выходом 16 преобразователя. Вход 17 служит для подачи признака преобразования и соединен с первым входом элемента 18 памяти, второй вход кото-, рого соединен с выходом делителя 13,первым тактовым входом накапливающего сумматора 8 для сдвига его содержимого на две позиции в сторону младших разрядов и тактовым входам счетчика 19, второй вход которого соединен единичным выходом элемента 8 памяти и вторым входом дешифратора 3. Вход 20 служит для подачи синхроимпульса на элемент И 21, второй вход которого соединен с нулевым выходом элемента 18 памяти. Выход элемента И 21 соединен с разрешающим входом формирователя 12. Второй выход делителя 13 частоты соединен со вторым тактовым входом на-капливающего сумматора 8 для сдвига его содержимого на две позиции в сторону старших разрядов. Первые выходы блока 22 памяти соединены с информационными входами первой, второй и третьей групп элементов И 5-7. Вторые выходы блока 22 памяти соединены с информационными входами регистра 23,6335 10ичному эквиваленту, смещенному напозиций в сторону старших или младшихразрядов.На фиг. 2 представлены три массиваприведенных двоичных эквивалентов (повосемь в каждом массиве для р =+1; 0;-1). Колонки -4 указывают соответственно номер выбираемого массива, десятичный порядок, условное обозначение10 и значение приведенных двоичных эквивалентов соответственно. Следует отМетить, что каждый из приведенныхэквивалентов первого и третьего массивов получается из приведенных двоичныхэквивалентов второго массиваЭ Ц-) = Э у 2-43э( 1) э 2соответственно, необходимый двоичныйпорядок указывает колонка 5. При этомнеобходимый массив выбирается в соответствии с содержимым регистров 5и 27.На фиг. 3 представлен пример преобразования числа 0,9999991 О . Преобразование осуществляется за 6 циклов по шесть тактов каждый, где приняты следующие обозначения: Л 2,ПР 2 - сдвиг либо в сторону старших,либо в сторону младших разрядов содержимого сумматора 8, Г 2- частичные произведения от умножения соответствующего двоичного эквивалентана младшую и старшую пары разрядовпреобразуемой тетрады, См - операция55 суммирования,Процесс преобразования в известном преобразователе осуществляетсяв два этапа. Причем на первом этапепроизводится суммирование произведений преобразуемых тетрад на соответствующие им двоичные эквиваленты. Навтором этапе вычисленная сумма умножается на считываемый из блока памяти двоичный эквивалент, однозначноопределяемый по величине и знаку десятичного порядка. На этом этапе требуется умножение полноразрядных чисел.В предлагаемом устройстве умноженияполноразрядных чисел производитьмне нужно, так как блок 22 памяти хранит приведенные двоичные эквивалентывида О-Р 2Поэтому выигрыш в быстродействииравен времени, затрачиваемому на умножение двух.п разрядных чисел.формула изобретения 9 82 дением. При этом в зависимости от состояния регистра 4 одна иэ групп элементов И 5-7 передает, информацию либо прямым кодом, либо прямым кодом со 1"двигом на одну позицию в сторону старших рязрядов, либо дополнительным кодом. Одновременно производится сдвиг в сторону младших разрядов регистра 2 на две позиции, По второму импульсу (С 002) серии СОО дешифратор 3 производит анализ старшей пары разрядов регистра 2, При этом каждое состояние дешифратора 3 запоминает регистр 4 Одновременно производится сдвиг содержимого сумматора 8 на две позиции в сторону младших разрядов и чтение блока 22 памяти по тому же адресу. По третьему импульсу (С 053) серии С 05 накапливающий сумматор 8 производит суммирование первого и второго частичных произведений. Одновременно счетик 19 адреса изменяет свое состояние на единицу. При этом устанавливается адрес следующего двоичного эквивалента в массиве. На этом цикл преобразования одной тетрады заканчивается. Затем поступают последующие тетрады двоично-десятичного числа. При этом описанный процесс чтения соответствующего приведенного двоичного эквивалента из блока 22 памяти и умножения на тетраду ничем не отличается от описанного и повторяется еще (1-1) раз. Преобразованная мантисса снимается с выходом двоичного сумматора 8, а съем величины н знака двоичного порядка производится с третьего .и четвертого регистров 5 и 23. Описанное выше поясняет следующая микропрограмма.С 051:Рр 1: Т.С 001: Анализ РР 1, Чтение БП,См 8: = См 8 Л 24С 052: См 81: = См 80 + ГРр 1.РР 1 ПрС 002:См 82=См 81Анализ Рр, Чтение БП 22С 053:См 83:=См 82+ РРрРр 1 Пр 2+1 СЧА 19: = СгА 19+Следует отметить, что блок 22 памяти содержит 2 р+1 массив поприведенных двоичных эквивалентов в каж 5 дом массиве (на десятичный разряд по одному) . Причем каждый (+1)-й приведенный двоичный эквивалент р-го массива равен -му приведенному дво 1. Преобразователь двоично-десятичной дроби в двоичную дробь, содер82633 жап 1 ий первый, второй и третий регист 1 ры, накапливающий сумматор, первую, вторую и третью группу элементов И, блок памяти, блок управления, счетчик, первый и второй дешифраторы, причем5 информационный вход десятичного разряда преобразователя соединен с информационным входом первого регистра, выход которого соединен с информационным входом блока управления, пер ный, второй и третий тактовые выходы которого соецинены соответственно с тактовым вхоцом первого регистра, с первым и вторым тактовыми входами; накапливающего сумматора, выход уп 15 ранления умножением блока управлениями соединен с первыми входами элементов И первой, второй и третьей групп, нторые входы которых соединены с выходом мантиссы блока памяти, а ны ходы соединены соответственно с входами прямого кода, входами сдвинутого прямого кода и входами дополнительного кода накапливающего сумматора, выходы которого являются вы ходами мантиссы преобразователя, выход порядка блока памяти соединен с входом второго регистра выходы которсгс являются выходами порядка преобразователя, входы порядка и знака т".,орядка п.:сбразсвателя соединены с входами первого дешифратора и трет.ьегс регистра соответственно, входы упрвляющегс сигнала пуска преобра:.сцателя, вход синхроимпульса преобразователя и вход признака мантиссы преобразователе соединены состветстценно с первьпл, вторим и третьим входами блока управления, первый тактовый выход которого соединен с третьими 12 30 35 40 45 50 55 входами элементов И первой, второйи третьей групп, выход номера десятичного разряда блока управления соединен с ив 1:срмационньм входом счетчика,четвертый тактсньгЛ выход блс:;а управления соединен с тактоным входом второго дешифратсравходы первой группыразрядов адреса которого соединены с выходом счетчика, а выход второго дешифратора соединен сс входом блокапамяти, первый выход третьего регистра является выходом знака порядка преобразователя, третий тактовыйвыход блока управления соединен с тактовым входом счетчика, о т л и ч а ющ и Й с я ;ем, что, с целью повьппения 5быстродействия, в него включен четвертый регистр, вход которогс соединен с выходом первого дешифратора,а выход - с входами второй группыразрядов адреса, второго дешифратора,входы третьей группы разрядов адресакоторого соединены со вторым выходомтретьего регистра, управляющий вход первого дешифратора соединен с выходом опроса порядка блока управления. 2. Цреобразователь по п. 1, о тл и ч а ю щ и й с я тем, что, в нем блок управления содержит генератор импульсов, дешифратор, регистр, делитель частоты, Формирователь импульсов, элемент памяти и элемент И, причем вход генератора импульсов является первым входом блока управления, первый вход элемента И является вторым входом блока управления, второй вход элемента И соединен с нулевым выходом элемента памяти, а выход,1 элемента И соединен с разрешающим входом Формирователя импульсов, первый и второй тактовые входы которогосоединены с первым и вторым выходамигенератора импульсов, являются первым и четвертым тактовыми выходамиблока управления и соединены с входом делителя частоты и первым входомдешифратора соответственно, второйвход которого является информационным входом блока управления, третийвход соединен с единичным выходомэлемента памяти и является выходомномера десятичного разряда блока управления, а выход дешиФратора соединен со входом регистра. выход которого является выходом управления умножением блока управления, первый ивторой выходы делителя частоты являются вторым и третьим тактовыми выходами блока управления, причем второй выход делителя частоты соединенсо входом установки в ноль элемента памяти, вход установки единицы которого является третьим входом блокауправления, выход Формирователя импульсов является выходом опроса порядка блока управления.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 473179, кл.б 06 Г 5/02, 1970.2, Авторское свидетельство СССРпо заявке У 2649587/18-24кл. С Об Г 5/02, 1978,Лг Составитель М. Аршавский Редактор С. Шевченко ТехредА.Бабинец Корректор Г. Решетник Заказ 251 б 70 Тираж 745 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, ЖРаушская наб., д. 4/5Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 Лг+ЕйСмОр г,ЕбгСм г, ЕМ См 7 р 2 ГВг г+Е 47СмдаргЕ 42См лг О 7 См дарг Е 72 Ег 7 См Орг Егг См Лг Е 77 см Прг 72 См,РазряА/10, 7 2 5 4 5 6 7 В 9101112 7 д 74 1 б 1 б 17 ЮЮгдг 1 00 ООООООООООРОО д 0 О ПОПОЮ дО а ОООООООООООО Оа 00 010 0 00 О Опддоппдддопп П О б П 10 П Ооаппооддодопдодоо и о пп 1 додо ОРООООПППОООПОП 1 ОПП О О ООП ОПООПО П и П д дд Опдддп ОПОП 0100 10 Р 0 О а О ООООПППППдоаа 17 0100 О а 0 0 О ОООООООО 00001 01 1 000 ОО О О ООООООП 000000001011 0 00 оо Одоппоаооаппп 17 01 ооо 00 о о дд д даоддпод и 711 7 1.1 о ЮОООР д ддОо о О Оааоооодоо 7 Оо 00071 00 ООО О О ООООООО 01000 ддд 01 Од або О О Оапдддопод 10 ааоа о Р 1 ада Р Раааааода 1 дааад 1 к РРР пооао Оааадаоо 7 0100071 Оо 7 ООООООООООО 10 7 О 0017 оа 7 ОО 0000000000070100077 7 7 010 РОООО Одаоо 101 0 о О 1 10 7 1 7 1 о Одд д д д дд О 00 01 0 7 а а О 1 1 а 1 1 7 000000000010100017 7 1 01 Пд О Одоп 0000110 П 1 ОП 1 д 1 ООООООО 1700 7100101 О 1 7 да ОООООО 077 0017 00110 011 дд 000000170017001 01 11 7 Р Оа 00000000710011 дп 7011 11 о ОООООО 77 0011 ОР 1100 71 Оа О 000011111 1 7111 О д 000011 11 17 1117111 Р 1 1 Р РР аао 7 аоаа оаооодпдооа попо 00011110 доппддд 010 1 ( д Рд 0000011117117777 7 1 7 0 110 ОО 1 ОООПП ПП 0 ООРПОППОО ОПО 00100111 1111777 7171 0 110 0,10 Р 177 7 17 77711771 01 10 т=+Ф РЦ 2. Р

СмотретьЗаявка

2818807, 06.07.1979

ОМЕЛЬЧЕНКО ВИКТОР ИВАНОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичной, двоичную, дроби, дробь

Опубликовано: 30.04.1981

Код ссылки

<a href="https://patents.su/8-826335-preobrazovatel-dvoichno-desyatichnojj-drobi-v-dvoichnuyu-drob.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоично-десятичной дроби в двоичную дробь</a>

Предыдущий патент: Устройство для отображения информации на экране электронно лучевой трубки

Следующий патент: Однородная вычислительная среда

Случайный патент: Устройство для суммирования двухимпульсных последовательностей