Устройство для умножения последовательных п-разрядных двоичных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 769541

Авторы: Адамия, Асатиани, Кублашвили, Мирианашвили, Смородинова, Чачанидзе

Текст

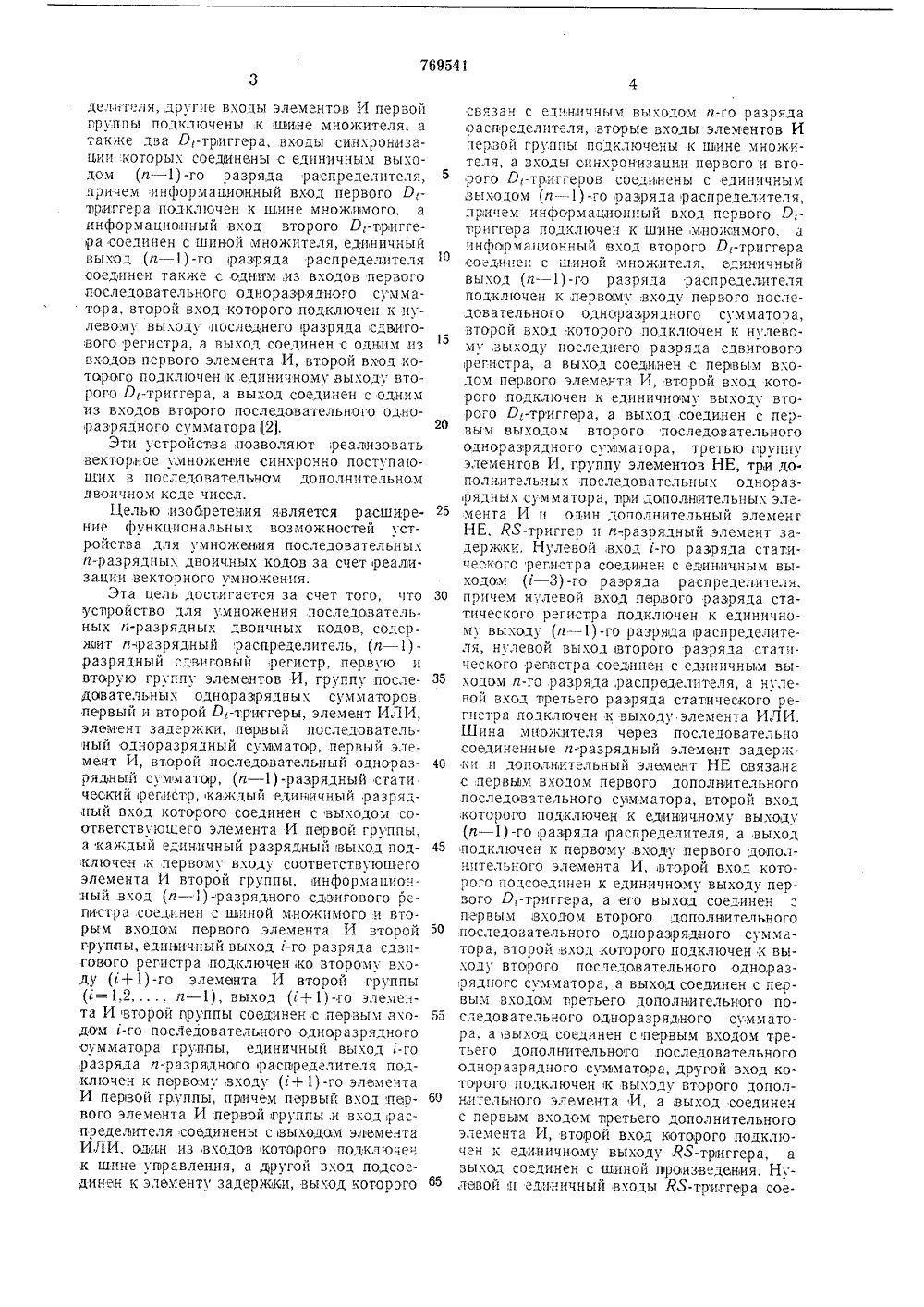

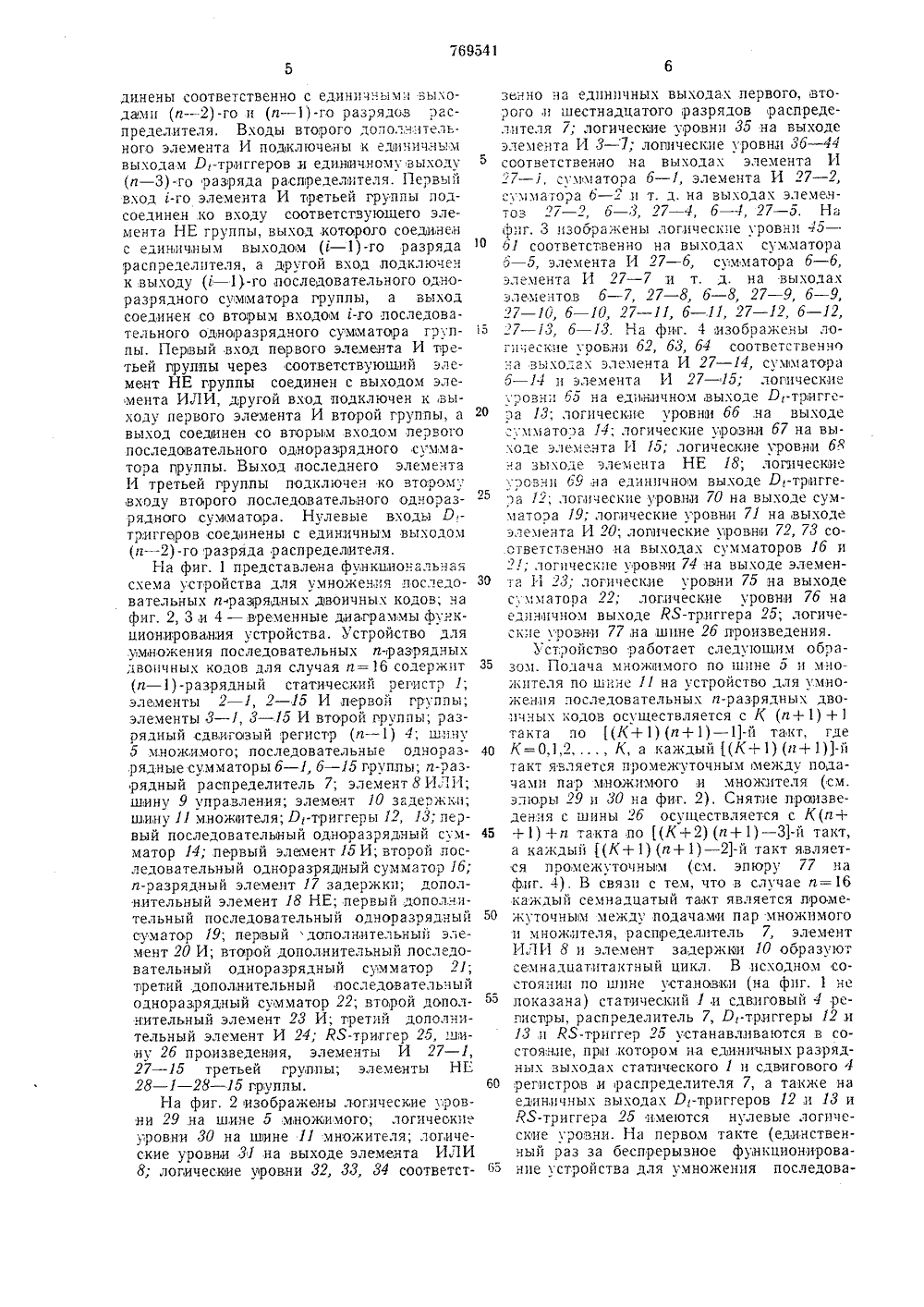

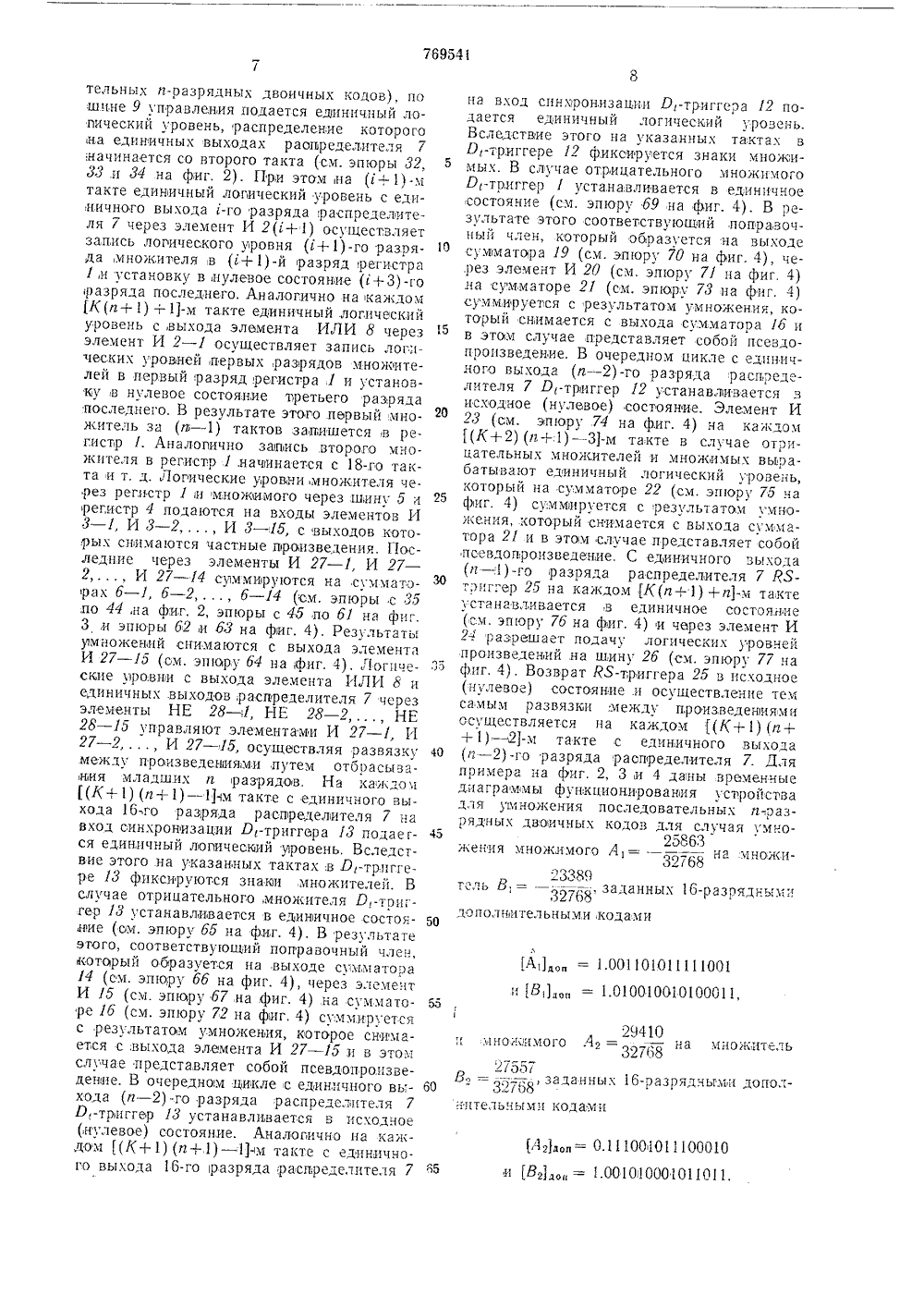

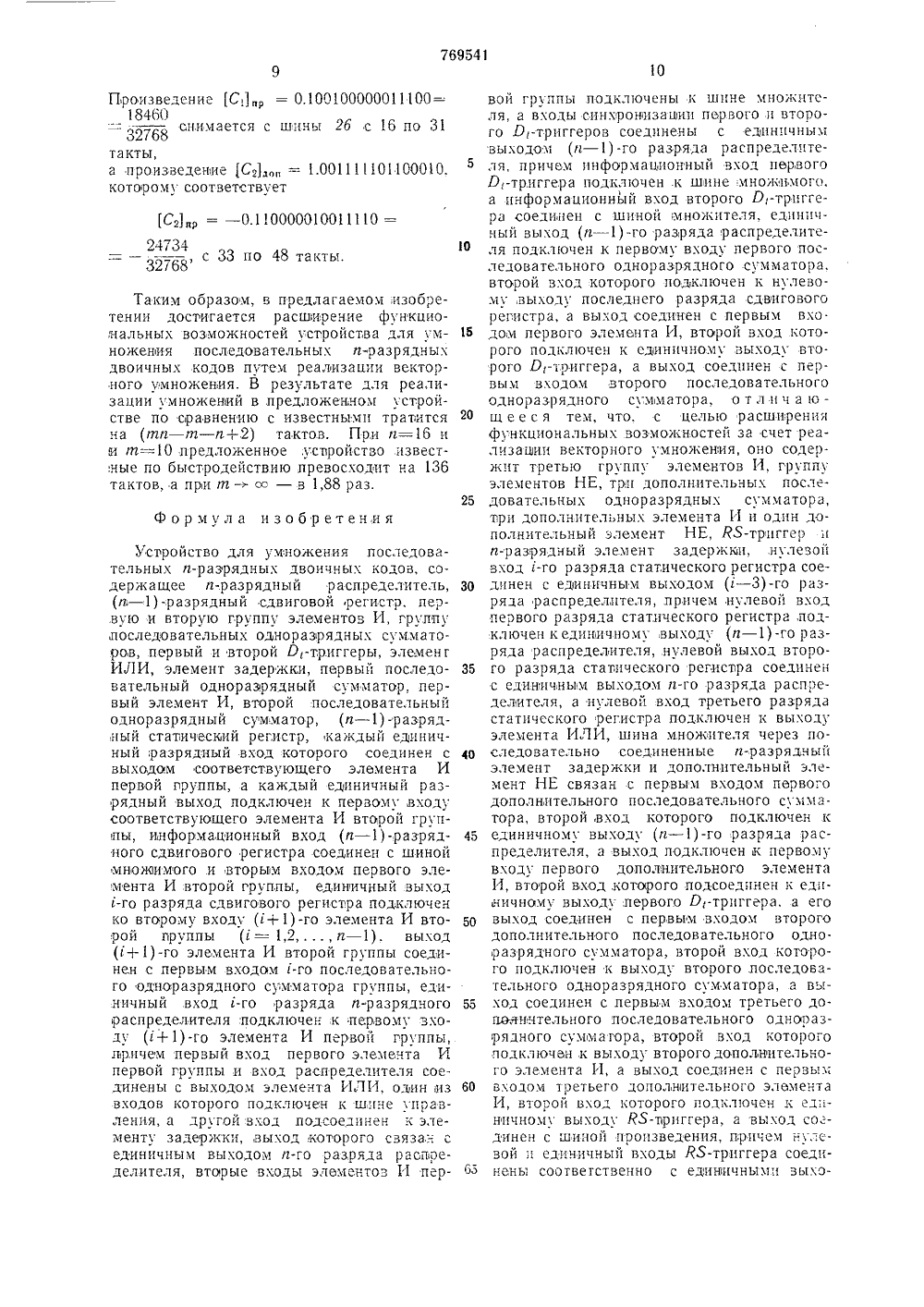

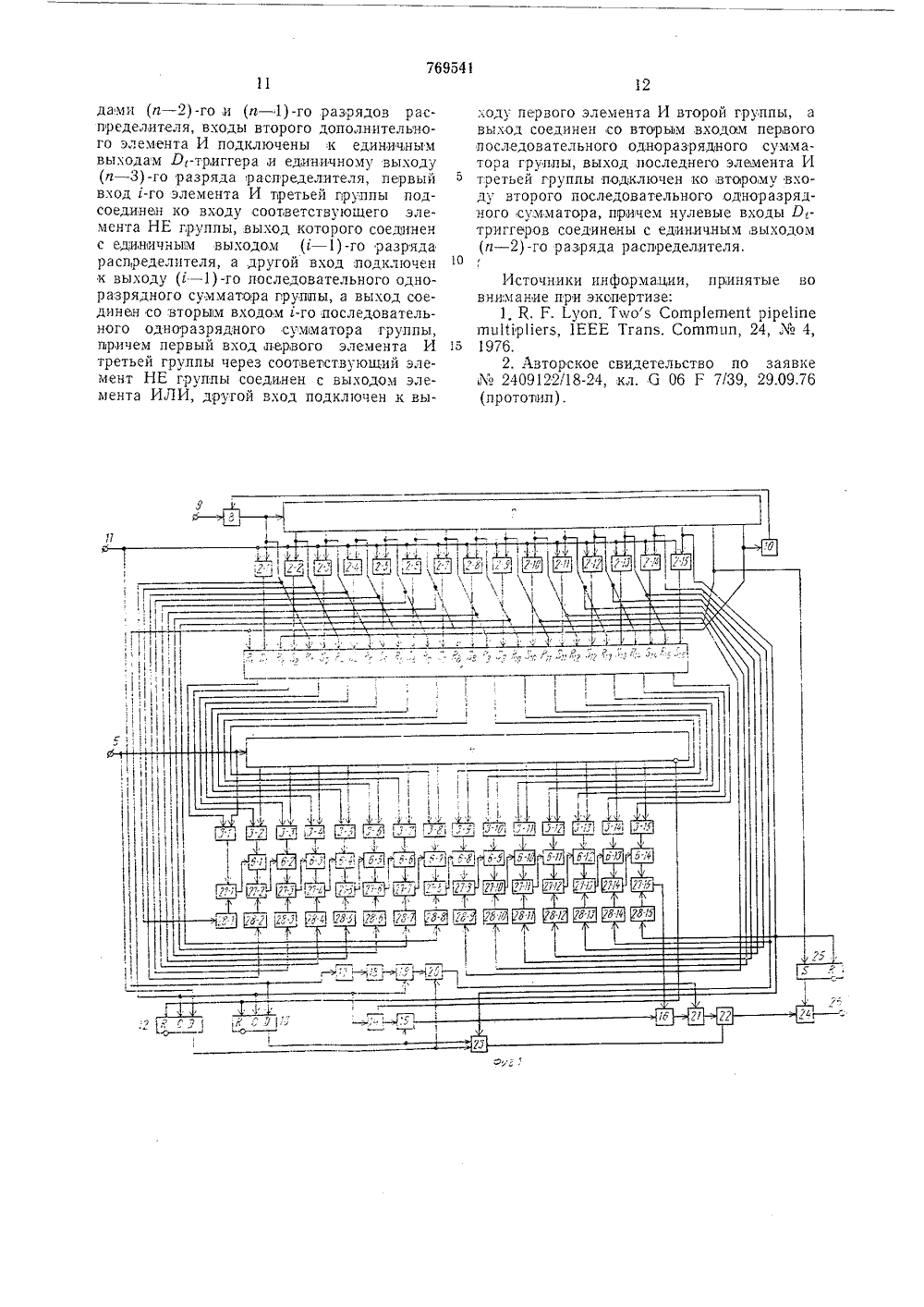

т 1", к.", м:,. 4) ие уП А о НИЕИЗСБР ЕТЕ Н И Я Союз Советских Социалистических Республик(б 1авт. свпд-в лнительн 22) Заявлено 23,0 622874/18-24 8 (2 1.Кл," 6 06 Г 7 я 2 присоединением заявк ударственный комнте(43) Опубликовано 07.10.80. Бюллетень е 3 (45) Дата опубликования описания 21.11.80 о делам изобретений н открытий72) Авторы изобретен В. Г. Чачанидзе, Г. Г. Асатиани, Т. О.Г. Смородинова, Р. 3. Мирианашвили: блашвили,Н. Д. Адами 71) Заяви Институт проблем управлени 54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯПОСЛЕДОВАТЕЛЬНЫХ и-РАЗРЯДНЫХДВОИЧНЫХ КОДОВ 2 Изоо слительн некторн пающих ном дво содержи ,пают мл ретение от ой техники ого умножи в последо ичном код тся в и-м р адшие разр носится к области вычии предназначено для теля синхронно ,постувательном дополнителье чисел, в которых знак азряде и сначала постуяды. Известно устроиство для умножения двух синхронно поступающих в последовательно дополнительном двоичном коде чисел, в которых знак, содержится в и-м разряде и сначала поступают младшие разряды. Устройство содержит сдвиговый регистр, распределитель, статический регистр, 15 а также элементы И,и последовательно одноразрядные сумматоры. При обработке больших массивов .данных производительность известного устройства для умножения последовательных и-разрядных кодов зна чительно уменьшается, так как оно реализует т умножений за 2 тп тактов, где и - разрядность последовательного двоичного кода, а предлагаемое устройство реализует т угмножений за (тп+т+и - 2) тактов, 2 где тп тактов приходятся собственно на мнохкение т пар множимого и множителя, т тактов - ,на развязку произведений, а п представляет собой время начальной реакции устройства 111.36 Наиболее близким техническим решением к изобретению является устройство для умножения последовательных и-разрядных двоичных кодов, содержащее (и - 1) -разрядный статический регистр, каждьш единичный разрядный вход которого соединен с выходом соответствующего элемента И первой группы, а каждый единичный разрядный выход подключен к одному из входов элемента И второй группы, а также (и - 1) -разрядный сдвпговый регистр, информ а ционны й вход которого соедив ен с шиной множимого и другим входом первого элемента И второй группы, единичный выход г-го разряда сдвигового регистра подключен к другому входу (г+1)-го элемента И второй труппы, выход каждого из которых, начиная со второго, соединен с однихг из входгов соответствующего последовательного одноразрядного сумматора группы, а также п-разрядный распределитель, единичный выход г-го,разряда, которого подключен и одному из входов (г+1)-го элемента И первой группы, причем олин из входов первого элемента И первой группы и вход распределителя соединены с выходом элемента ИЛИ, один,из входов которого подключен к шине управления, а другои вход соединен через элемент задержки с единичным выходом и-го разряда распределителядругие входы элементов И первой группы подключены к шине множителя, а также два Рг-тригге 11 а, Входы синхронизации которы.; соед 1 инвны с единичным выходом (и - 1) -го разряда распределителя, причем информационный вход первого Р,- триггера подключен к шине множдмого, а информационный вход второго Рг-триггера соединен с шиной множителя, единичный выход (и - 1) -го 1 разряда распределителя соединен также с одним,из входов первого последовательного одноразрядного сумматора, второй вход которого подключен к нулевому выходу последнего 1 разряда сдвитового регистра, а выход соединен с одним из входоз первого элемента И, второй вход которого подключен к единичному выходу второго Рг-триггвра, а выход соединен с одним из входов второго последовательного одноразрядного сумматора 21.Эти устройства позволяют реал 1 изовать векторное умножение синхрочно поступающих з последовательном дополнительном двоичном коде чисел.Целью, изобретения является расширение функциональных возможностей устройсгва для умножения последовательны.; и-разрядных двоичных кодов за счет реализации векторного умножения.Эта цель достигается за счет того, что успройство для умножения последовательных и-разрядных двоичных кодов, содерж 1 ит и,разрядный распределитель, (и - 1)- разрядный сдзиговый,регистр, первую и вторую группу элементов И, группу последовательных однораэрядных сумматоров, первый и второй Рг-триггеры, элемент ИЛИ, элемент задержки, первый последовательный одноразрядный сумматор, первый элемент И, второй последовательный одноразрядньш сумматор, (и 1)-разрядный стати ческий 1 регистр, каждый един 1 ичный разрядный вход которого соединен с выходом соответствующего элемента И первой группы, а каждый единичный разрядный выход подключен,к первому входу соответствующего элемента И второй группы, 1 информационный вход (и - 1)-разрядного сдзигового репистра соединен с ш 1 ной множимого и вторым входом первого элемента И второй группы, единичный выход 1-го разряда сдзигового регистра подключен ко второму входу (+1) -го элемента И второй группы (г=1,2, и - 1), выход (1+1)-го элемента И второй группы соединен с первым входом г-го последовательного одноразрядного сумматора группы, единичньш выход г-го ,разряда и-разрягдно 1 го 1 расвределителя подключен к первому входу (1+1)-го элвмента И пер 1 вой группы, причем первый вход пврвого элемента И первой группы,и вход распредел 1 ителя соединены с 1 выходам элемента ИЛИ, один из входов 1 которого подключен к шине управления, а другой вход подсоединвн к элементу задержки, выход которого 5 1 О 5 20 25 30 35 40 45 50 60 65 связан с единичным выходом и-го разряда оаспределителя, вторые входы элементов И первой группы подключены к шахине множителя, а входы синхронизации первого и второго Р 1-триггеров соединены с единичным выходом (и - 1) -го,разряда распределителя, п"ичем информационный вход первого Р- триггера подключен к шине множимого. а информационный вход второго Р 1-триггвра соединен с шиной множителя, единичный выход (и - 1)-го разряда распределителя подключен к первому;входу первого последозательното одноразрядного сумматора, второй вход которого подключен к нулевому,выходу последнего разряда сдвигового регистра, а выход соединен с перовым входом первого элемента И, второй вход которого подключен к единичному выходу второго Рг-триггвра, а выход, соединен с первым выходом второго последовательного одноразрядного сумматора, третью группу элементов И, руппу элементов НЕ, три до. полнительных последовательных одноразрядных сумматора, ври дополнительных элемента И и один дополнительный элемент НЕ, Я 5-триггер и и;разрядный элемент задержки, Нулевой,вход гхго разряда статического регистра соединен с ед 1 иничным выходом (1 - 3) -го разряда распределителя, причем нулевой вход первого разряда статического регистра подключен к единичному выходу (и - 1)-го разряда распределителя, нулевой выход 1 второго разряда статического регистра соединен с единичным выходом и-го разряда,распределителя, а нулевой вход третьего разряда статического регистра лодкл 1 очен к выход) элемента ИЛИ. Шина множителя через последовательно соединенные и-разрядный элемент задержки и дополнительный элвмент НЕ связана с первым входом первого дополнительного последовательного сумматора, второй вход которого подключен .к единичному выходу (и - 1) -го,разряда распределителя, а выход подключен к пврвому входу первого дополнительного элемвнта Ивторой вход которого подсоединен к единичному выходу первого Р 1-триггера, а вго выход соединен первым входом второго дополн 1 ительного последовательного однораз 1 рядного сумматора, второй вход которого подключен к выходу второго последовательного одноразрядного сумматора, а выход соединен с первым входогм третьего дополнительного последовательного одноразрядного сумматора, а 1 зыход соединен с первым входом третьего дополнтгтельното последовательного одноразрядчого сумматора, другой вход которого подключен к выходу второго дополнительного элемента И, а выход соединен с первым входом третьего дополнительного элемента И, втоуой вход которого подключен к единичному выходу Р 5-тр 1 иггера, а выход соединен с шиной произведения. Нулвзой,п единичный входы Я 5-триггвра сое 76954127 - 15 третьей группы; элементы НЕ28 - 1 - 28 - 15 группы.На фиг. 2 изображены логические уров 60 ни 29 на шине 5 множимого; логические уровни 30 на шине 11 множителя; логические уровнями 31 на выходе элемента ИЛИ 8; логические уровни 32, 33, 34 соответстдинены соответственно с единичнымн зы. одами (и - -2)-го и (л - 1)-го разрядов распределителя. Входы второго дополнительного элемента И подключены к единичнь 1 м выходам Р-триггеров и единоличному гвыходу (и - 3)-го разряда распределителя, Первый вход -го элемента И третьей группы подсоединен ко входу соответствующего элемента НЕ группы, выход которого соедииен с единичным выходом (1 - 1) -го разряда распределителя, а другой вход, подключен к выходу- 1)-го последовательного одноразрядного сумматора группы, а выход соединен со вторым входом 1-го последовательного одноразрядного сумматора груп пы. Первый вход первого элемента И третьей пруппы через соответствующий элемент НЕ группы соединен с выходом элемента ИЛИ, другой вход подключен к,выходу первого элемента И второй группы, а 20 выход соединен со вторым входом первого последовательного одноразрядного сумм а- тора пруппы. Выход последнего элемента И третьей группы подключен ко втором; ,входу второго последовательного однораз 25 рядного сумматора. Нулевые входы .О, - триггеров соединены с единичным выходом (л - 2) -го разряда распределителя.На фиг. 1 представлена фуниьиональная схема устройства для умножечия последа вательных и разрядных двоичных кодов; ча фиг. 2, З,и 4 - временные диаграммы функционирования устройства. Устройство для умножения последовательных и-разрядных двоичных кодов для случая и=16 содержит 35 (и - 1) -разрядный статический регистр 1; элементы 2 - 1, 2 - 15 И первой группы; элементы 3 - 1, 3 - 15 И второй группы; разрядный сдвигозый регистр (и - 1) 4; шину 5 множимого; последовательные однораз рядные сумматоры б - 1, б - 15 группы; л-разрядный распределитель 7; элемент 8 ИЛИ; шину 9 управления; элемент 10 задержки; шину 11 множителя; Р-триггеры 12, 13; первый последовательный одноразрядный сум матор 14; первый элемент 15 И; второй последовательный одноразрядный сумматор 16; л-разрядный элемент 17 задержки; дополнительный элемент 18 НЕ; первый дополнительный последовательный одчоразрядный 50 суматор 19; первый дополнительный элемент 20 И; второй дополнительный последовательный одноразрядный сумматор 21; третий дополнительный последовательный одноразрядный сумматор 22; второй дополчительный элемент 23 И; третий дополчительный элемент И 24; Я 5-триггер 25, шину 26 произведения, элементы И 27 - 1,зенно на единичных выходах первого, второго,и шестнадцатого, разрядов распределителя 7; логические уровни 35 на выходе элемента И 3 - 7; логические уровни 36 - 44 соответственно на выходах элемента И 27 - 1, сумматора 6 - 1, элемента И 27 - 2, сумматора б - 2 и т, д. на выходах элемеитов 27 - 2, б - 3, 27 - 4, 6 - 4, 27 - 5. На фиг. 3 изображены логические уровни 45 - 61 соответственно на выходах сумматора 6 - 5, элемента И 27 - б, сумматора 6 - 6, элемента И 27 - 7 и т. д. на выходах элементов б - 7, 27 - 8, б - 8, 27 - 9, б - 9, 27 - 10, б - 10, 27 - 11, б - 11, 27 - 12, б - 12, 7 - 13, б - 13. На фиг. 4 изображены логические розин 02, 63, 64 соответственно на зь;ходах элемента И 27 - 14, сумматора 6 - 14 и элемента И 27 - 15; логические уровни 65 на единичном, выходе Р-триггера 13; логические розии бб на выходе :умматора 14; логические у 1 розни 67 на выходе элемента И 15; логические уровни 68 на зыходе элемента НЕ 18; логические ровни 69 иа едгничном выходе Р,-тригге,а 12; логические уровни 70 на выходе сумматора 19; логические уровни 71 на,выходе элемента И 20; логические уровни 72, 73 соответственно на выходах сумматоров 16 и 21; логические уровни 74 на выходе элемента И 23; логические уровни 75,на выходе с, мматора 22; логические уровни 76 на единичном выходе Й 5-триггера 25; логические уровни 77,на шине 26 произведения.Устройсвзо работает следующим образом. Подача множимого по шине 5 и множителя по шине 11 на устройство для умножения последовательных и-разрядных двоичных кодов осуществляется с К (и+1)+1 такта по (К+1) (и+1) - 1-й такт, где К=0,1,2 К, а каждый (К+1) (и+1)-й такт является промежуточным между подачами пар множимого и множителя (см. эпюры 29 и 30 на фиг. 2). Снятие произведения с шины 26 осуществляется с К(п+ + 1) + л такта по (К+ 2) (и+ 1) - 3-й такт, а каждый (К+1) (и+1) - 2-й такт является промежуточным (ом. эпюру 77 на фиг. 4). В связи с тем, что в случае и=16 каждый семнадцатый такт является промежуточным между подачами пар множимого и множителя, распределитель 7, элемент ИЛИ 8 и элемент задержки 10 образуют семнадцатитактный цикл. В исходном состоянии по шине установки (на фиг. 1 не показана) статический 1 и сдвиговый 4 реписгры, распределитель7, Р-триггеры 12 и 13 и Л 5-триггер 25 устанавливаются в состояние, при котором на ед 1 иничных разрядных выходах статического 1 и сдвиговогорегистров и распределителя 7, а также на единичных выходах Р-триггеров 12 и 13 и Л 5-триггера 25 имеются нулевые логические урозни. На первом такте (единственный раз за беспрерывное функционирование устройства для умножения последовательных и-разрядных двоичных кодов), по шине 9 управления подается единичный лопический уровень, распределение которого на единичных выходах распределителя 7 .начинается со второго такта (см. эпюры 32, Л и 84 на фиг, 2). При этом на (г+1)-м такте единичный логический уровень с единичного выхода г-го разряда распределителя 7 через элемент И 2(г+1) осуществляет запись логического уровня (г+1) -го разряда множителя в (г+1)-й разряд регистра 1 ги установку в нулевое состояние (г+3)-го разряда последнего. Аналогично на каждом К(п+1) 1-1-м такте единичный логический уровень с,выхода элемента ИЛИ 8 через элемент И 2 - 1 осуществляет запись логических уровней первых,разрядов множителей в первый разряд регистра,1 и установку в нулевое состояние третьего разряда последнего. В результате этого первый множитель за (и - 1) тактов задишется в регистр 1. Аналопично запрись второго множителя в регистр 1,начинается с 18-го такта и т, д. Логические уровни множителя через регистр 1 и множимого через, шину 5 и регистр 4 подаются на входы элементов И 8 - 1, И 8 - 2 И 8 - 15, с выходов которых снимаются частные произведения. Последние через элементы И 27 - 1, И 27 - 2 И 27 - 14 суммируются на сумматорах б - 1, 6 - 2 6 - 14 (см. эпюры с 85 ло 44,на фиг. 2, эпюры с 45 по 61 на фиг.3 гн эпюры 62 и 68 на фиг. 4), Результаты умножений снимаются с выхода элемента И 27 - 15 (ом. эпюру 64 на фиг. 4). Логические уровни с выхода элемента ИЛИ 8 и единичных выходов, распределителя 7 через элементы НЕ 28 - ;1, НЕ 28 - 2 НЕ 28 - 15 управляют элементами И 27 - 1, И 27 - 2 И 27 - 15, осуществляя развязку между произведениями,путем отбрасьаания младших п фазрядов. На каждом (К+1) (и+1) - 1 м такте с единичного вы.хода 16.го разряда распределителя 7 на вход синхронизации Р-триггера 1 З подаегся единичный лопичесмий уровень, Вследствие этого на указанных тактах,в Р-триггере 13 фиксируются знаки множителей. В случае отрицательного, множителя Р-триггер 13 устанавливается в единоличное состояние (см, эпюру 65 на фиг. 4). В результате этого, соответствующий поправочный член, некоторый образуется на выходе сумматора 14 (см. эпюру бб на фиг. 4), через элемент И 15 (см. эпвру 67 на фиг. 4) на сумматоре 16 (см. эпюру 72 на фланг, 4) суммируется с результатом умножения, которое снимяется с,выхода злемента И 27 - 15 и в этом случае представляет собой псевдопроизведение. В очередногм цикле с едингичного вь.- хода (п - 2) -го разряда распределителя 7 Р,-триггер 13 устанавливается в исходное (,нулевое) состояние. Аналогично на каждом (К+1) (и+1) - 1 м такте с единичного выхода 16-го разряда распределителя 7 5 0 15 20 25 30 Э 40 45 50 55 50 55Я,- 1.001101011111001и 1 Ви, = 1.010010010100011,29410 32768 множитель и множгимого 27557В. = - ;,= заданных 16-разрядньгми допол впельными кодами А р= 0.111001011100010ги ВД , = 1.001010001011011. на вход синхронизации Рг-триггера 12 подается единичный логический уровень. Вследствие этого на указанных тактах в Рг-триггере 12 фиксируется знаки множимых. В случае отрицательного множимого Р-триггер 1 устанавливается в единичное состояние (см. эпюру 69 на фиг, 4). В результате этого соответствующий поправочный член, который образуется на выходе сумматснра 19 (см. эпюру 70 на фиг. 4), через элемент И 20 (см, эпюру 7 на фиг. 4) на сум,маторе 21 (см. эпюр,у 78 на фиг. 4) суммируется с результатом умножения, который снимается с выхода сумматора 16 и в этом случае представляет собой псевдо- произведение. В очередном цикле с единичного выхода (и - 2)-го разряда распределителя 7 Рг-триггер 12 устанавливается з исходное (нулевое) состояние. Элемент И 28 (см. эпюру 74 на фиг. 4) на каждом (К+2) (гг+1) - 3-м такте в случае отрицательных множителей и множимых вььрабатывают единичный логический уровень, который на сумматоре 22 (см. эпюру 75 на фиг. 4) суммируется с результатом умножения, который снимается с выхода сумматора 21 и в этосом случае представляет собой псевдопроизведение. С единичного выхода (гг - 1) -го разряда распределителя 7 Р 5- триггер 25 на каждом К(п+1)+п-м такте устанавливается в единичное состояние (см. эпюру 76 на фланг, 4) и через элемент И 24 разрешает подачу логических уровчей произведений на шину 26 (см. эпюру 77 на фиг, 4), Возврат Р 5-триггера 25 в исходное (нулевое) состояние и осуществление тем самым развязки между произведениями осуществляется на каждом (К+1) (и+ + 1) - 2-м такте с единичного выхода (и - 2)-го разряда распределителя 7. Лля примера на фиг, 2, 3 и 4 даны временные диаграфмы функционирования устройства для умногжения последовательных иразрядных двоичных кодов для случая лно 25863жения множнмого А, = --- на множи"976823389тель О, = вв , в заданных 6-разрядными15 20 25 Произведение СД, = 0,100100000011100=18460снимается с шины 2 б с 16 по 31такты,а произведение С 2)л, -- 1.00111101100010,которому соответствует С 21 пр = - 0.110000010011110 24734---- , с 33 по 48 такты. 32768 Таким образом, в предлагаемом,изобретении достигается расш 1 ирение функциональных возможностей устройства для умножения последовательных п-разрядных двоичных кодов путем реализации векторного умножения. В результате для реализации умножен 1 ий в предложенног устройстве по сравнению с известными тратится на (тп - т - и+2) тактов. При гг=16 и м т=10 предложенное,устройство цзвест;ные по быстродействию превосходит на 136 тактов, а при т с - в 1,88 раз. Формула изобретения Устройство для умножения последовательных п-разрядных двоичных кодов, содержащее п-.разрядный распределитель, (и - 1) -разрядный сдвиговой регистр, пер,вую и вторую группу элементов И, группу последовательных одноразрядных сумматоров, первый и второй Рг-триггеры, элеменг ИЛИ, элемент задержки, первый последовательный одноразрядный сумматоо, первый элемент И, второй последовательный одноразрядный сумматор, (и - 1) -разрядный статический регистр, каждый единичный;разрядный вход которого соединен с выходом соответствующего элемента И первой пруппы, а каждый единичный разрядный выход подключен к первому входу соответствующего элемента И второй группы, информационный вход (и - 1) -разрядного сдвигавого регистра соединен с шиной множимого и вторым входом первого элемента И второй группы, единичный выход г-го разряда сдвигового регистра подключен ко второму входу (г+1)-го элемента И второй группы (г = 1,2 и - 1). выход (1+1)-го элемента И второй группы соединен с первым входом г-го последовательного одноразрядного сумматора группы, единичный вход г-го разряда и-разрядчого распределителя подключен к первому входу (г+1)-го элемента И первой группы, причем первый вход первого элемента И первой группы и вход распределителя соединены с выходом элемента ИЛИ, один из входов которого подключен к шНне управления, а другой вход подсоединен к элементу задержки, выход которого связан с единичным выходом и-го разряда распределителя, вторые входы элементов И пер 30 35 40 45 50 55 60 65 ВОЙ группы подкл 10 чены к шине многкптсля, а входы синхронцзац 1 иц первого и второго Р 1-триггеров соединены с единичным выходом (и - 1) -го разряда распределителя, причем цнформацлонныЙ вход первого Р 1-триггера подключен,к шне:мноркБ 10 го, а информационный вход второго Р 1-триггера соединен с шиной множителя,ный выход (п - 1) -го разряда распределителя подключен к первому входу первого последовательного одноразрядного сумматора, второй вход которого подключен к нулевому,выходу последнего разряда сдвигового регистра, а выход соединен с первым вхо. дом первого элемента И, второй вход которого подключен и сдинцчному выходу второго Рг-триггера, а выход соединен с первым входом второго последовательного одноразрядного сумматора, о т л ц ч а ющ ее ся тем, что. с целью расширения функциональных возможностей за счет реализап 1 ии векторного умножения, оно содержит третью группу элементов И, группу элементов НЕ, трп дополнительных последовательных одноразрядных сумматора, три дополнительных элемента И и один дополнительный элемент НЕ, Я 5-триггер ц и-разрядный элемент задержки, нулевой вход г-го разряда статического регистра соединен с единичным выходом (г - 3)-го разряда распределителя, причем нулевой вход первого разряда статического регистра,подключен к единоличному,выходу (п - 1) -го разряда распределителя, нулевой выход второго разряда статического регистра соединен с един 1 ичным выходом гг-го разряда распределителя, а нулевой вход третьего разряда статического регистра подключен к выходу элемента ИЛИ, шина множителя через последовательно соединенные гг-разрядны элемент задержки и дополнительный элемент НЕ связан с первым входом первого дополнительного последовательного сумматора, второй, вход которого подключен к единичному выходу (и - 1)-го разряда распределителя, а выход подключен к первому входу первого дополнительного элемента И, второй вход которого подсоединен к единичному выходу первого Р-триггера, а его выход соединен с первым входом второго дополнительного последовательного одноразрядного сумматора, второй вход которого подключен к выходу второго последовательного одноразрядного сумматора, а выход соединен с первым входом третьего допэлн тельного последовательного одноразрядного суммагора, второй вход которого подключен к выходу второго дополнительного элемента И, а выход соединен с первым входом третьего дополн 1 ительного элемента И, второй вход которого подключен к единичному выходу Й 5-триггера, а выход соединен с шиной произведения, причем нулевой и едичичный входы Ю-триггера соединены соответственно с един 1 ичнымц зыходами (и - 2)-го,и (и - 1)-го разрядов распределителя, входы второго дополнительного элемента И подключены к единичным выходам .О,-триггера,и единичному выходу (п - 3) -го разряда распределителя, первый вход -го элемента И третьей группы подсоединен ко входу соответствующего элемента НЕ группы, выход которого соединен с единичньим выходом ( - 1)-го разряда распределителя, а другой вход, подключен к выходу ( - 1) -го последовательного одноразрядного сумматора группы, а выход соединен со вторым входом -го последовательного одноразрядного сумматора группы, причем первый вход первого элемента И третьей группы через соответствующий элемент НЕ группы соединен с выходом элемента ИЛИ, другой вход подключен к вы 12ходу первого элемента И второй группы, авыход соединен со вторььм входом перногопоследовательного одноразрядного сумматора группы, выход последнего элемента Итретьей группы подключен ко второму входу второго последовательного одноразрядного сумматора, причем нулевые входы Й,- триггеров соединены с единичным,выходом(л - 2)-го разряда распределителя.10Источники информации, принятые вовнимание при экопертизе:1, К, Г. 1.уоп, Твоз Согпр 1 ещеп 1 р 1 ре 11 пегпцШр 11 егз, 1 ЕЕЕ Тгапз. Согппшп, 24,4,15 1976,2. Авторское свидетельство по заявкеМ 2409122/18-24 кл. 6 06 Г 7/39, 29.09.76. 4 Тип. Харьк. фил. пред. Патент зказ 1289/1295ПО Поиск Изд. М 484 дарственного комитета СССР 113035, Москва, Ж, РауТира; по дела ская наб 772 изобретений одписное открытий

СмотретьЗаявка

2622874, 23.05.1978

ОРДЕНА ЛЕНИНА ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ АН СССР

ЧАЧАНИДЗЕ ВЛАДИМИР ГАВИЕВИЧ, АСАТИАНИ ГУРАМ ГЕОРГИЕВИЧ, КУБЛАШВИЛИ ТЕНГИЗ ОТАРОВИЧ, СМОРОДИНОВА ОЛЬГА ГРИГОРЬЕВНА, МИРИАНАШВИЛИ РОИН ЗУРАБОВИЧ, АДАМИЯ НОДАР ДАВИДОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: двоичных, кодов, п-разрядных, последовательных, умножения

Опубликовано: 07.10.1980

Код ссылки

<a href="https://patents.su/8-769541-ustrojjstvo-dlya-umnozheniya-posledovatelnykh-p-razryadnykh-dvoichnykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения последовательных п-разрядных двоичных кодов</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Многоканальное устройство для обслуживания запросов

Случайный патент: Устройство для регулирования межэлектродного зазора при электрохимической обработке