Микропроцессор для вводавывода данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 618733

Авторы: Бестань, Калмыков, Кириченко, Кривоносов, Сычев

Текст

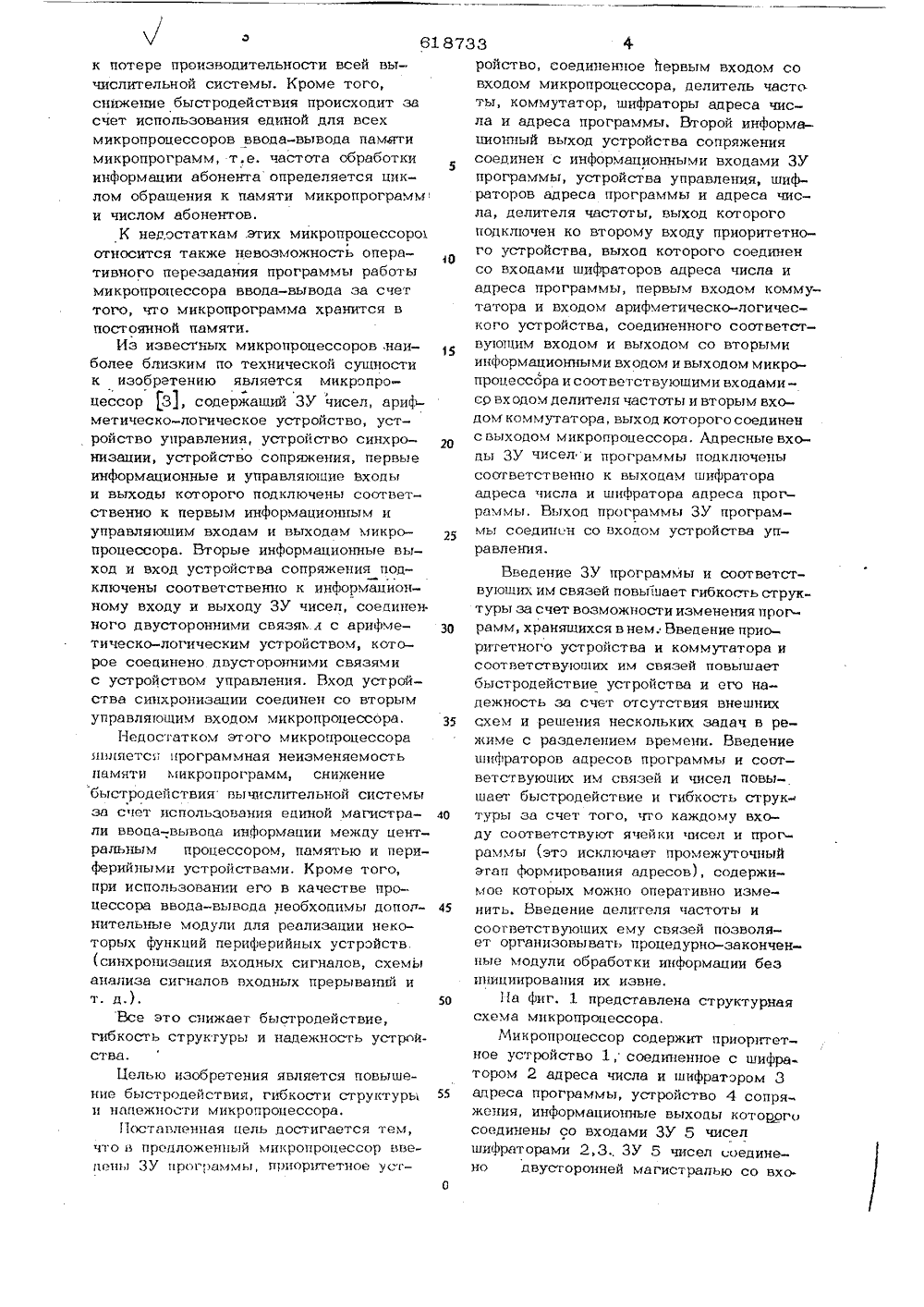

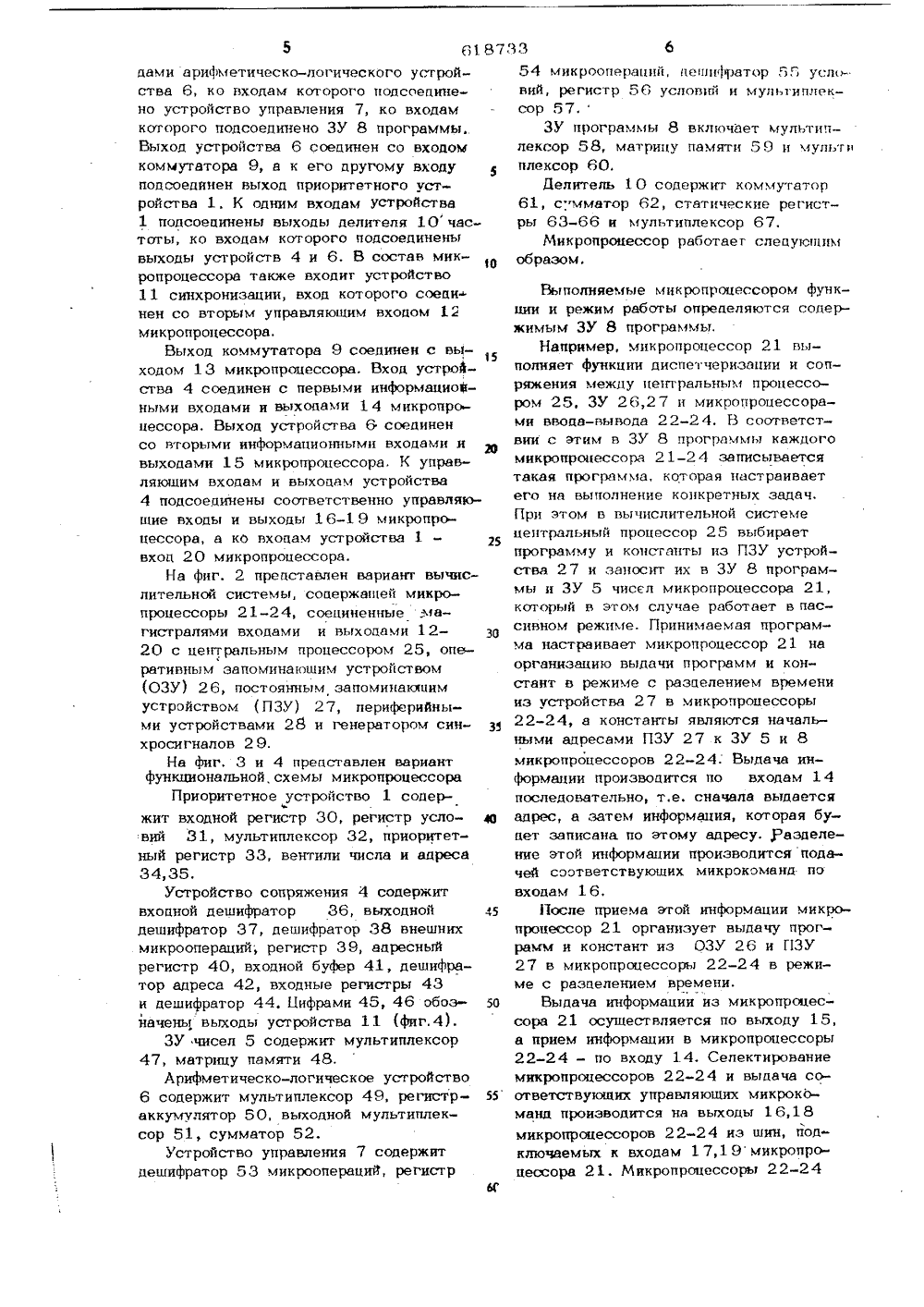

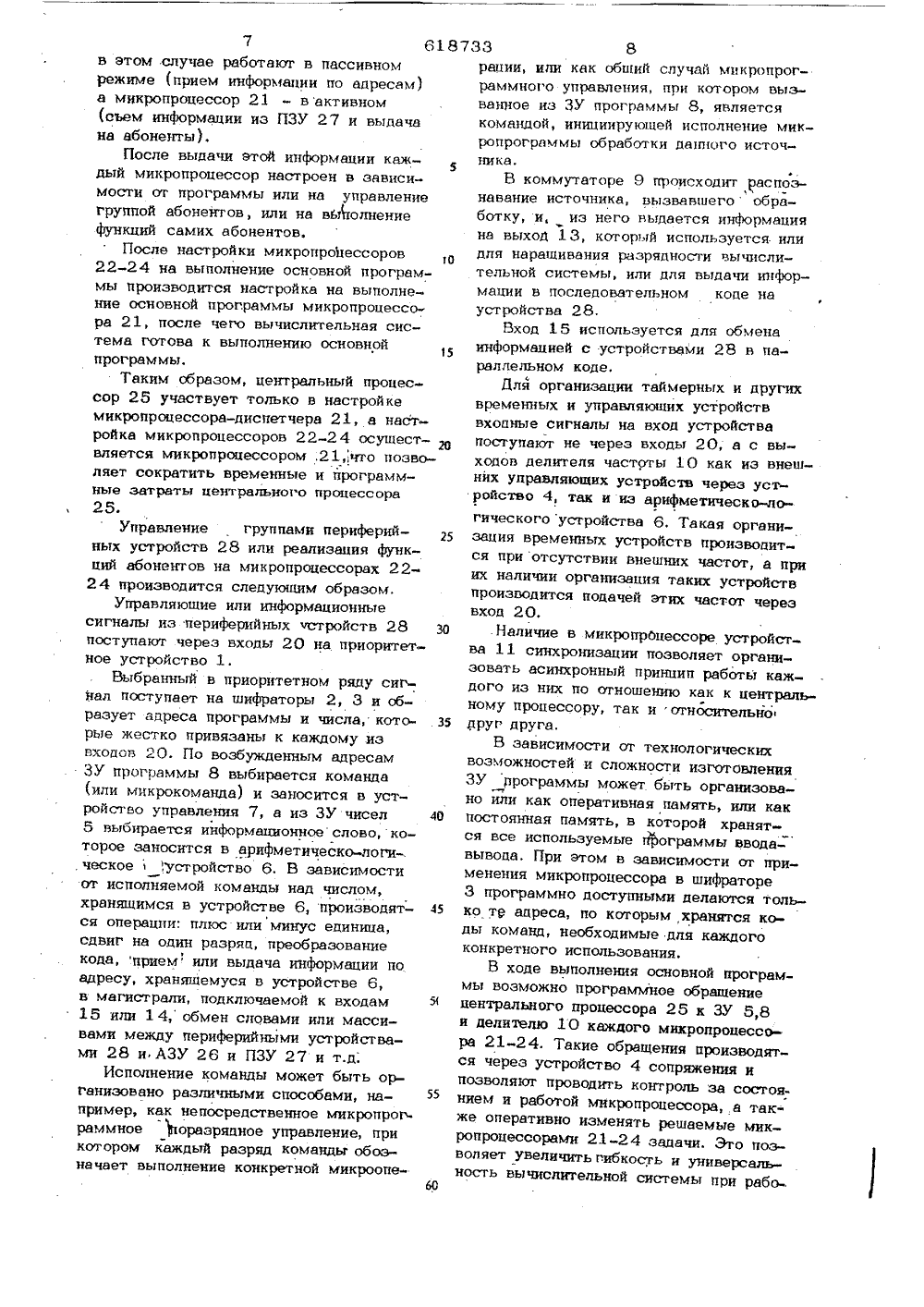

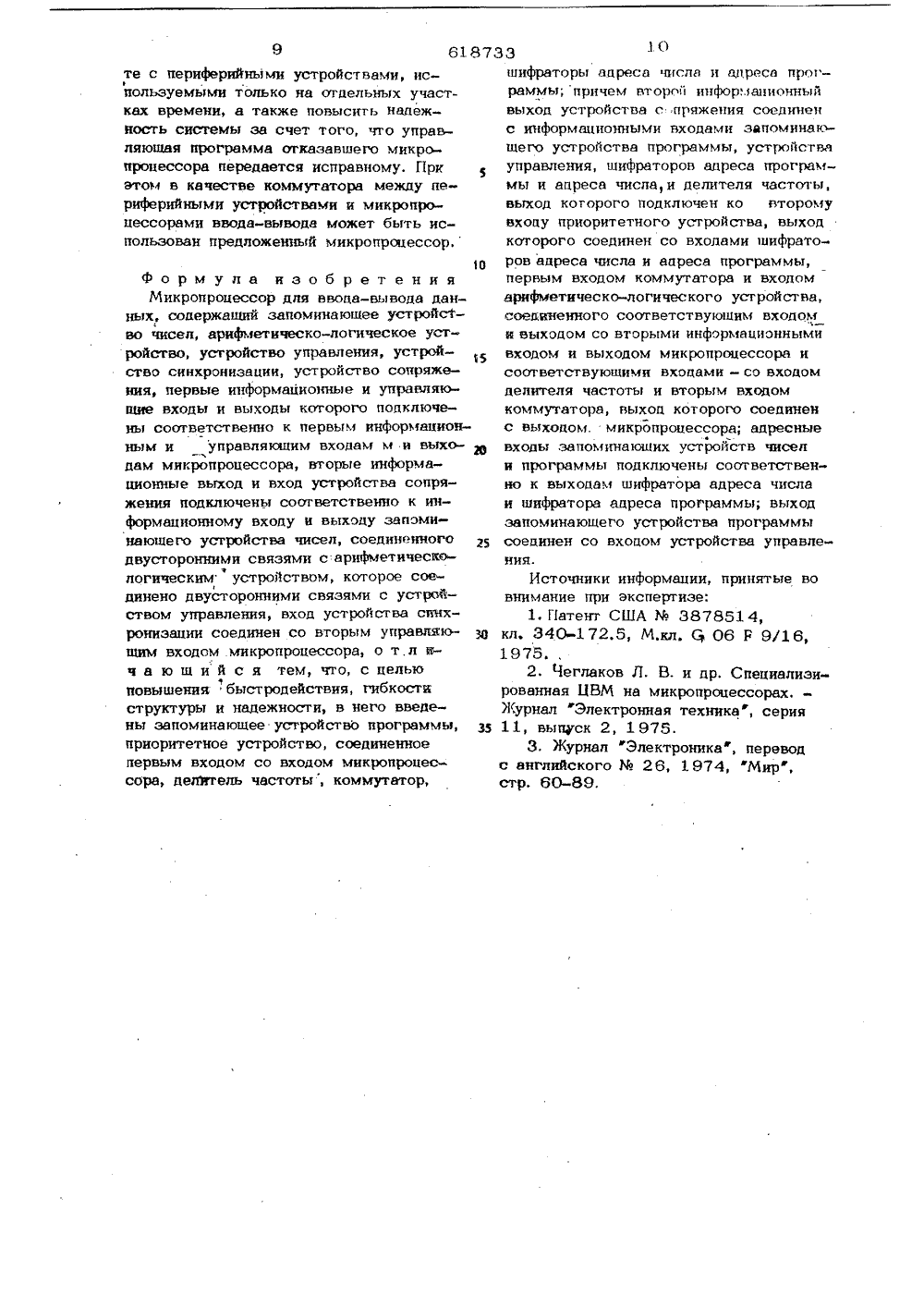

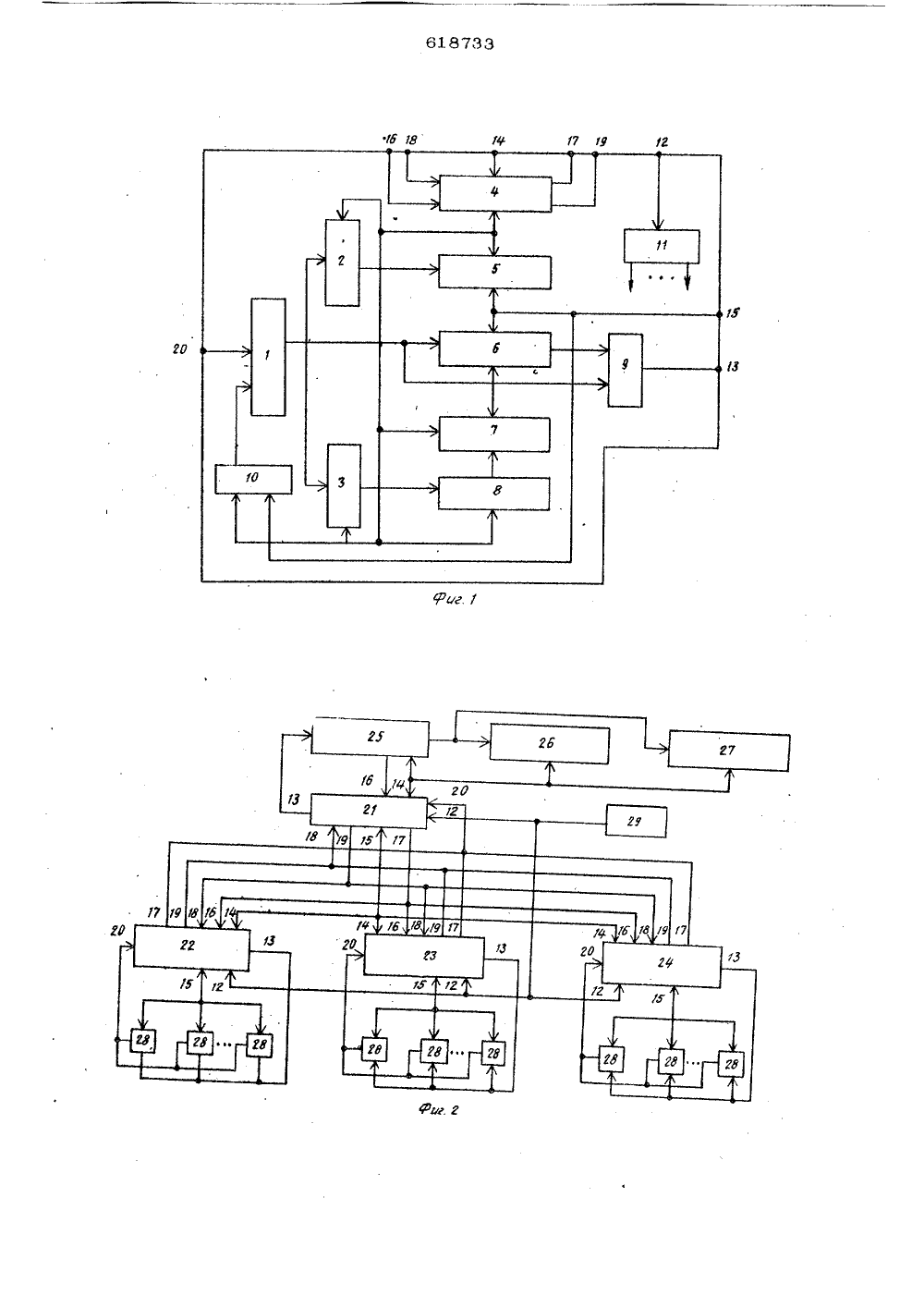

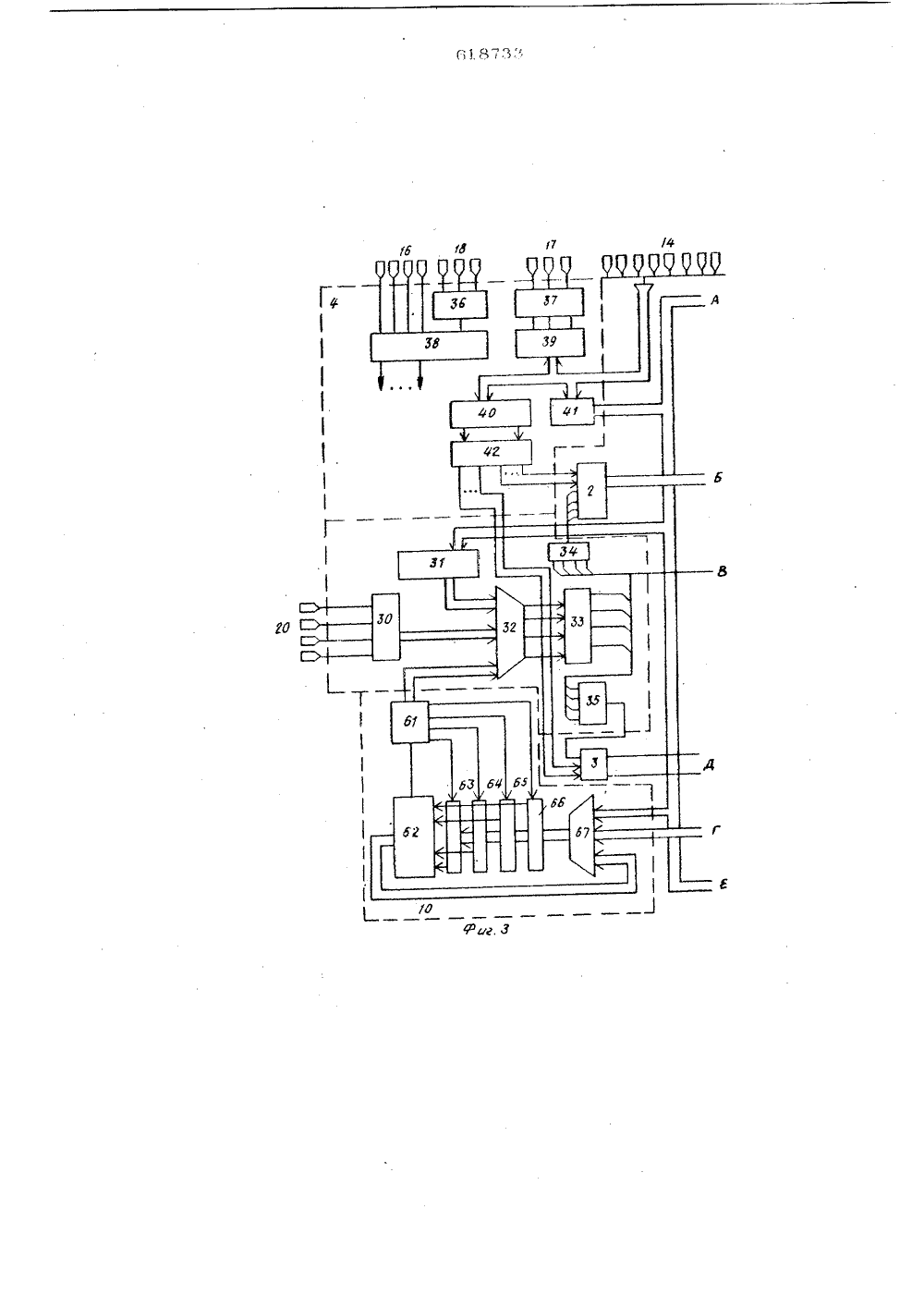

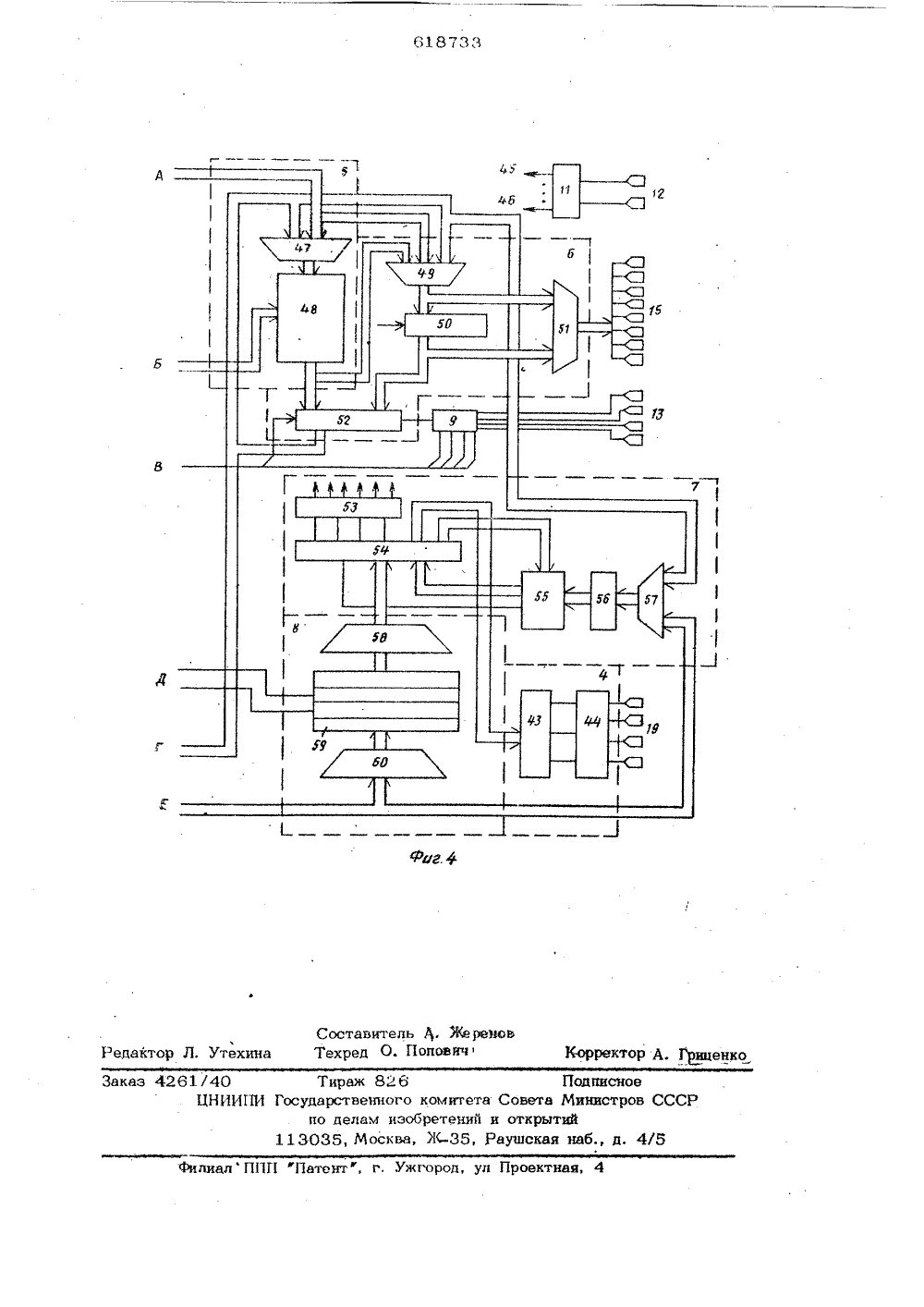

О П И.С-АК.И/Е И ЗОБРЕТЕ ЙЯЯ Союз СоветскикСоциалистимескикРеспублик(11) 6187.33 д.ву11470/18-24 6 РЗ/ рисоединением заявки Хасудерстеенный комитет Соает 1 а Министров СССР оо делам изобретений и открытий(53) УЙК 681,327 .2 (088.8) 5) Дата опуб вания описания 3 ычев, Р. 2) Авто изобр стань, и А. И 71) Заявите МИКРОПРОЦЕССОР ДЛЯ ВВОДА-ВЫВОДДАННЫХ Не го мик опроцессорйствия за агистралим процес между памятью центральнь ми вводаухъярусной времч выда ные устройст дв-вывода м ней занята ром н процессораПри этом в дв ной системе во пин в периферий процессоров вво обмена информвц вательно, работа числительчи информаиз микро тральслепо- пргцессов центрального води о 61) Дополнительное к22) Заявлено 00.01:76 Изобретение относится к области вычислительной техники и может быть использовано при построении многопрограм мных и мНогопроцессорных вычислительных систем, а также управляющих и вычислительных систем с разветвленной сетью абонентов.Известен микропроцессор, содержаший последовательный сумматор, входную и выходную последовательные. шины, буферные регистры, логический блок и блок управления с запоминающим устройством (ЗУ) микропрограмм 1. Обработка входной информации в нем производится в соответствии с микрооперацией, выбираемой из ЗУ, работой которого управляет логический блок, а ветвление и ход выполняемой программы определяются управляющими словами, поступающими нв вход логического блока.Недостатками этого микропроцессора является то, что при построении устройства вводв-вывода нв его основе требуется значительное число дополнительных внешних схем (устройство упА. Калмыков, Н. В. Кириченкривоносов равления, устройство прерывания н т.д,), а также отсутствие гибкости за счет того, что архитектура и соединения внешних схем определяют жесткую структуру такого устройства ввода-вывода.Известентакжемикропроцессорисполь) зуемый для организации системы ввода-вывода информации содержашей устройство управления, регистр микрокоманпы, соединенный с врифметико-логическим устройством, и оперативную память чисел, соединенную с устройством сопряжения (2. является снижение быстро счет использования единой с памятью невозможна,30 50 к потере производительности всей вычислительной системы. Кроме того,снижение быстродействия происхопит засчет использования единой для всехмикропроцессоров ввода-вывода памятимикропрограмм, т.е, частота обработкиинформации абонента определяется циклом обращения к памяти микропрограмми числом абонентов.К недостаткам .этих микропроцессороотносится также невозможность оперативного перезадания программы работымикропроцессора ввопа-вывода за счеттого, что микропрограмма хранится впостоянной памяти.Из известных микропроцессоров .наиболее близким по технической сущностик изобретению является микропроцессор 31, содержащий ЗУ чисел, арифметическо-логическое устройство, устройство управления, устройство синхронизации, устройство сопряжения, первыеинформационные и управляюпие входыи выходы которого подключены соответственно к первым информационным иуправляющим входам и выходам микропроцессора. Вторые информационные выход и вход устройства сопряжения подключены соответственно к информационному входу и выходу ЗУ чисел, соединенного двусторонними связяк л с арифметическо-логическим устройством, которое соединено двусторонними связямис устройством управления, Вход устройства синхронизации соединен со вторымуправляющим входом микропроцессора,Недостатком этого микропроцессораянляетсп программная неизменяемостьпамяти микропрограмм, снижениебыстродействия вычислительной системыза с ит использования единой магистрали ввода-вывода информации между центральным процессором, памятью и периферийными устройствами. Кроме того,при использовании его в качестве процессора ввода-вывода необходимы дополнительные модули для реализации некоторых функций периферийных устройств(синхронизация входных сигналов, схемыанализа сигналов входных прерываний ит. д.),Все это снижает быстродействие,гибкость структуры и надежность устройства.Целью изобретения является повышение быстродействия, гибкости структурыи напежности микропроцессора,Поставленная цель достигается тем,что в предложенный микропроцессор ввепены ЗУ программы, приоритетное устройство, соединенное йервым входом со входом микропроцессора, делитель часто ты, коммутатор, шифраторы адреса числа и адреса программы. Второй информационный выход устройства сопряжения соединен с информационными входами ЗУ программы, устройства управления, шифраторов адреса программы и адреса числа, делителя частоты, выход которого подключен ко второму входу приоритетного устройства, выход которого соединен со входами шифраторов адреса числа и адреса программы, первым входом коммутатора и входом арифметическо-логического устройства, соединенного соответствующим входом и выходом со вторыми информационными входом и выходом микропроцессора и соответствующими входамисо входом делителя частоты и вторым входом коммутатора, выход которого соединен с выходом микропроцессора. Адресные вхопы ЗУ чисели программы подключены соответственно к выхопам шифратора адреса числа и шифратора апреса программы, Выход программы ЗУ программы соединен со входом устройства управления.Введение ЗУ программы и соответствующих им связей повышает гибкость структуры за счет возможности изменения программ, хранящихся в нем, Введение приоритетного устройства и коммутатора и соответствующих им связей повышает быстродействие устройства и его надежность за счет отсутствия внешних схем и решения нескольких задач в режиме с разделением времени. Введение шифраторов адресов программы и соответствующих им связей и чисел повышает быстродействие и гибкость структуры за счет того, что каждому входу соответствуют ячейки чисел и программы (это исключает промежуточный эгап формирования адресов), содержимое которых можно оперативно изменить. Введение делителя частоты и соогветствуюгпих ему связей позволяет организовывать процедурно-законченные модули обработки информации без инициирования их извне.На фиг. 1 представлена структурнаясхема микропроцессора,Микропроцессор содержит приоритетное устройство 1, соединенное с шифра тором 2 адреса числа и шифратором 3 адреса программы, устройство 4 сопряжения, информационные выходы которого соединены со входами ЗУ 5 чисел шифраторами 2,3., ЗУ 5 чисел соединено двусторонней магистралью со вхо.5 6187 дами врифметическо-логического устройства 6, ко входам которого полсоепине но устройство управления 7, ко входам которого подсоелинено ЗУ 8 программы,. Выход усгройствв 6 соединен со входом коммутатора 9, а к его другому входу подсоединен выход приоритетного устройства 1. К одним входам устройства 1 подсоединены выходы делителя 10 частоты, ко входам которого подсоединены выходы устройств 4 и 6. В состав микропроцессора также входиг устройство 11 синхронизации, вход которого соеди нен со вторым управляющим входом 12 микропроцессора.Выход коммутатора 9 соединен с вы 15 ходом 13 микропроцессора. Вход устрояства 4 соединен с первыми информациоФ- ными входами и выходами 14 микропро цессора, Выход устройства 6 соединен со вторыми информационными входами и выходами 15 микропроцессора, К управляющим входам и выходам устройства 4 подсоединены соответственно управлщощие входы и выходы 16-19 микропроцессора, а ко входам устройства 1 вход 20 микропроцессора.На фиг. 2 представлен вариант вычислительной системы, содержащей микропроцессоры 21-24, соединенные магистралями входами и выходами 12- 3 я 20 с центральным процессором 25, оперативным запоминающим устройством (ОЗУ) 26, постоянным звпоминаклпим устройством ( ПЗУ) 27, периферийными устройствами 28 и генератором син- З 5 хросигналов 2 9.На фиг, 3 и 4 представлен вариант функциональной, схемы микропроцессораПриоритетное устройство 1 содержит входной регистр 30, регистр усло вий 31, мультиплексор 32, приоритетный регистр 33, вентили числа и адреса 34,35.Устройство сопряжения 4 содержит входной дешифратор 36, выходной 5 дешифратор 37, дешифратор 38 внешних микроопераций; регистр 39, адресный регистр 40, входной буфер 41, дешифратор адреса 42, входные регистры 43 и дешифратор 44. Бифрвми 45, 46 обоз начены выходы устройства 11 (фиг.4).ЗУ чисел 5 содержит мультиплексор 47, матрицу памяти 48.Арифметическо-логическое устройство 6 содержит мультиплексор 49, регистр аккумулятор 50, выходной мультиплексор 51, сумматор 52,Устройство управления 7 содержит дешифратор 53 микроопервций, регистр 3354 микрооперапий, дешифратор 5, уел-. вий, регистр 56 условий и мультиплексорр 57.ЗУ программы 8 включает мультип - лексор 58, матрицу памяти 59 и мульти плексор 60.Делигель 10 содержит коммутатор 61, с"мматор 62, статические регистры 63-66 и лтультиплексор 67.Микропроцессор работаег следующпл образом. Выполняемые микропроцессором функции и режим работы определяются содержимым ЗУ 8 программы,Например, микропроцессор 21 выполняет функции диспетчеризации и сопряжения между пеггральныл процессором 25, ЗУ 26,27 и микропроцессорами ввода - вывода 22-24. В соответствии с этим в ЗУ 8 программы каждогомикропроцессора 21-24 записываетсятакая программа, которая настраиваетего на выполнение конкретных задач,При этом в вычислительной системецентральный процессор 25 выбираетпрограмму и константы из ПЗУ устройства 27 и заносит их в ЗУ 8 программы и ЗУ 5 чисел микропроцессора 21,который в этом случае работает в пассивном режиме. Принимаемая программа настраивает микропроцессор 21 наорганизацию вылачи программ и констант в режиме с разделением временииз устройства 27 в микропроцессоры22-24, в константы являются начальными адресами ПЗУ 27 к ЗУ 5 и 8микропроцессоров 22-24; Вылача информации производится по вхолам 14последовательно, т,е, сначала выдаетсяадрес, а затем информация, которая будет записана по атому адресу.,Разделение этой информации производится подачей соответствующих микрокоманд повходам 16,После приема атой информации микропроцессор 21 организует выдачу программ и констант из ОЗУ 26 и Г 1 ЗУ27 в микропроцессоры 22-24 в режиме с разделением времени,Выдача информации из микропроцессора 21 осушествляегся по выходу 15,а прием информадии в микропроцессоры22-24 - по входу 14, Селектированиемикропроцессоров 22-24 и выдача соответствующих управляющих микрокоманд производится нв выходы 16,18микропроцессоров 22-24 из шин, подключаемых к входам 17,19 микропроцессора 21, Микропроцессоры 22-24733 8рации, или как общий случай микропрограммного управления, при котором вызванное из ЗУ программы 8, являетсякомандой, инициирующей исполнение микропрограммы обработки даптого источника,В коммутаторе 9 происходит распознавание источника, вызвавшегообработку, и, иэ него выдается информацияна выход 13, который используется илидля наращивания разрядности вычислительной системы, или для выдачи информации в последовательном коде наустройства 28.Вход 15 используется для обменаинформацией с устройствами 28 в параллельном коде,Для организации таймерных и другихвременных и управляющих устройстввходные сигналы на вход устройствапоступают не через входы 20, а с выходов делителя частоты 10 как иэ внешних управляющих устройств через устройство 4, так и из арифметическо-логическогоустройства 6, Такая организация временных устройств производится при отсутствии внешних частот, а приих наличии организация таких устройствпроизводится подачей этих частот черезвход 20.Наличие в микропроцессоре устройства 11 синхронизации позволяет организовать асинхронный принцип работы каждого из них по отношению как к центральному процессору, так и относительнодруг друга,В зависимости от технологическихвозможностей и сложности изготовленияЗУ программы может быть организовано йли как оперативная память, или какпостоянная память, в которой хранятся все используемые тфограммьт вводавывода. При атом в зависимости от применения микропроцессора в шифраторе3 программно доступными делаются только те адреса, по которым хранятся коды команд, необходимые для каждогоконкретного использования.В ходе выполнения основной программы возможно программное обращениецентрального процессора 25 к ЗУ 5,8и делителю 10 каждого микропроцессора 21-24, Такие обращения производятся через устройство 4 сопряжения ипозволяют проводить контроль за состоянием и работой микропроцессора, а также оперативно изменять решаемые микропроцессорами 21-24 задачи. Это позволяет увеличить гибкость и универсальность вычислительной системы при рабо-. 7 618в этом .случае работают в пассивномрежиме (прием информации по адресам)а микропроцессор 21 - вактивном1 съем информации из ПЗУ 27 и выдачана абоненты),После выдачи атой информации каждый микропроцессор настроен в зависимости от программы или на управлениегруппой абонентов, или на вьтттолнениефункций самих абонентов,После настройки микропроцессоров22-24 на выполнение основной программы производится настройка на выполнение основной программы микропроцессора 21, после чего вычислительная система готова к выполнению основнойпрограммы.Таким образом, центральный процессор 25 участвует только в настройкемикропроцессора-диспетчера 21, а настройка микропроцессоров 22-24 осущест цвляется микропроцессором,21что позволяет сократить временные и программныв затраты центрального процессора25.Управление группами периферийных устройств 28 или реализация функций абонентов на микропроцессорах 2224 производится следующим образом,Управляющие или информационныесигналы иэ периферийных ч:тройств 28 зОпоступают через входы 20 на приоритетное устройство 1,Выбранный в приоритетном ряду сигнал поступает на шифраторы 2, 3 и образует адреса программы и числа, кото- .35рые жестко привязаны к каждому извходов 20, По возбужденным адресамЗУ программы 8 выбирается команда(или микрокоманда) и заносится в устройство управления 7, а из ЗУ чисел 405 выбирается информационное слово, которое заносится в арифметическологи-.,ческое 1 ",устройство 6. В зависимостиот исполняемой команды над числом,хранящимся в устройстве 6, производятся операции: плюс или минус единица,сдвиг на один разряд, преобразованиекода, прием или выдача информации поадресу, хранящемуся в устройстве 6,в магистрали, подключаемой к входам 515 или 14, обмен словами или массивами между периферийными устройствами 28 и АЗУ 26 и ПЗУ 27 и т.д,Исполнение команды может быть организовано различными способами, например, как непосредственное микропрог.раммное )тораэрядное управление, прикотором каждый разряд команды обозначает выполнение конкретной микроопе6187 те с периферийными устройствами, используемыми только на отдельных участках времени, а также повысить надежность системы за счет того, что управляющая программа отказавшего микропроцессора передается исправному. Пркэтом в качестве коммутатора между цериферийными устройствами и микропроцессорами ввода-вывода может быть использован предложенный микропроцессор. формула изобретения Микропроцессор для ввода-вывода данных, содержащий запоминающее устройство чисел, арифметическо-логическое устройство, устройство управления, устройство синхронизации, устройство сонряжения, первые информационные и управляющие входы и выходы которого подключены соответственно к первым информационным и управляющим входам м и выхо-, дам микропроцессора, вторые информационные выход и вход устройства сопряжения подключены соответственно к информационному входу и выходу заломи нающего устройства чисел, соединенного двусторонними связями с арифметическотлогическим устройством, которое соединено двусторонними связями с устройством управления, вход устройства синхронизации соединен со вторым управляющим входом микропроцессора, о т л ич а ю ш и й с я тем, что, с целью1повышения быстродействия, гибкости структуры и надежности, в него введены запоминающее устройство программы, щ приоритетное устройство, соединенное первым входом со входом микропроцессора, деятель частоты , коммутатор,33.ошифраторы адреса числя и ддреса программы; причем второй инфор;мационныйвыход устройства с пряжения соединенс информационными входами запоминающего устройства программы, устройствауправления, шифраторов адреса программы и адреса числа,и делителя частотывыход которого подключен ко второмувходу приоритетного устройства, выходкоторого соединен со входами шифраторов адреса числа и адреса программы,первым входом коммутатора и входомарифметически-логического устройства,соединенного соответствующим входоми выходом со вторыми информационнымивходом и выходом микропроцессора исоответствующими вхоцами - со входомделителя частоты и вторым входомкоммутатора, выход которого соединенс выходом, микропроцессора; адресныеФвходы запоминающих устройств чисели программы подключены соответственно к выходам шифратора адреса числаи шифратора адреса программы; выходзапоминающего устройства программысоединен со входом устройства управления.Источники информации, принятые вовнимание при экспертизе:1. Патент США 14 3878514,кл, 340-172 5, М.кл. С 06 Р 9/16,1975.2, Чеглаков Л. В. и др. Специализированная ЦВМ на микропроцессорах,Журнал "Электронная техника, серия11, выгцгск 2, 1975.3. ЖурналЭлектроника, переводс английского И 26, 1974, "Мир,стр, 60-89.618733 Фиг. Тираж 826 Подписное Государственного комитета Совета Министров СССР по делам иэобретений и открытий 113035, Москва, Б 35, Раушская наб., д. 4/5

СмотретьЗаявка

2311470, 09.01.1976

ПРЕДПРИЯТИЕ ПЯ А-7160

СЫЧЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, БЕСТАНЬ ГЕННАДИЙ СЕРГЕЕВИЧ, КАЛМЫКОВ ВАЛЕНТИН АЛЕКСАНДРОВИЧ, КИРИЧЕНКО НИКОЛАЙ ВАСИЛЬЕВИЧ, КРИВОНОСОВ АНАТОЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 3/00

Метки: ввода—вывода, данных, микропроцессор

Опубликовано: 05.08.1978

Код ссылки

<a href="https://patents.su/8-618733-mikroprocessor-dlya-vvodavyvoda-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор для вводавывода данных</a>

Предыдущий патент: Пневматический счетчик импульсов

Следующий патент: Устройство для ввода информации

Случайный патент: 163238