Аналого-цифровой преобразователь биполярных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1018231

Авторы: Клочан, Лаврентьев

Текст

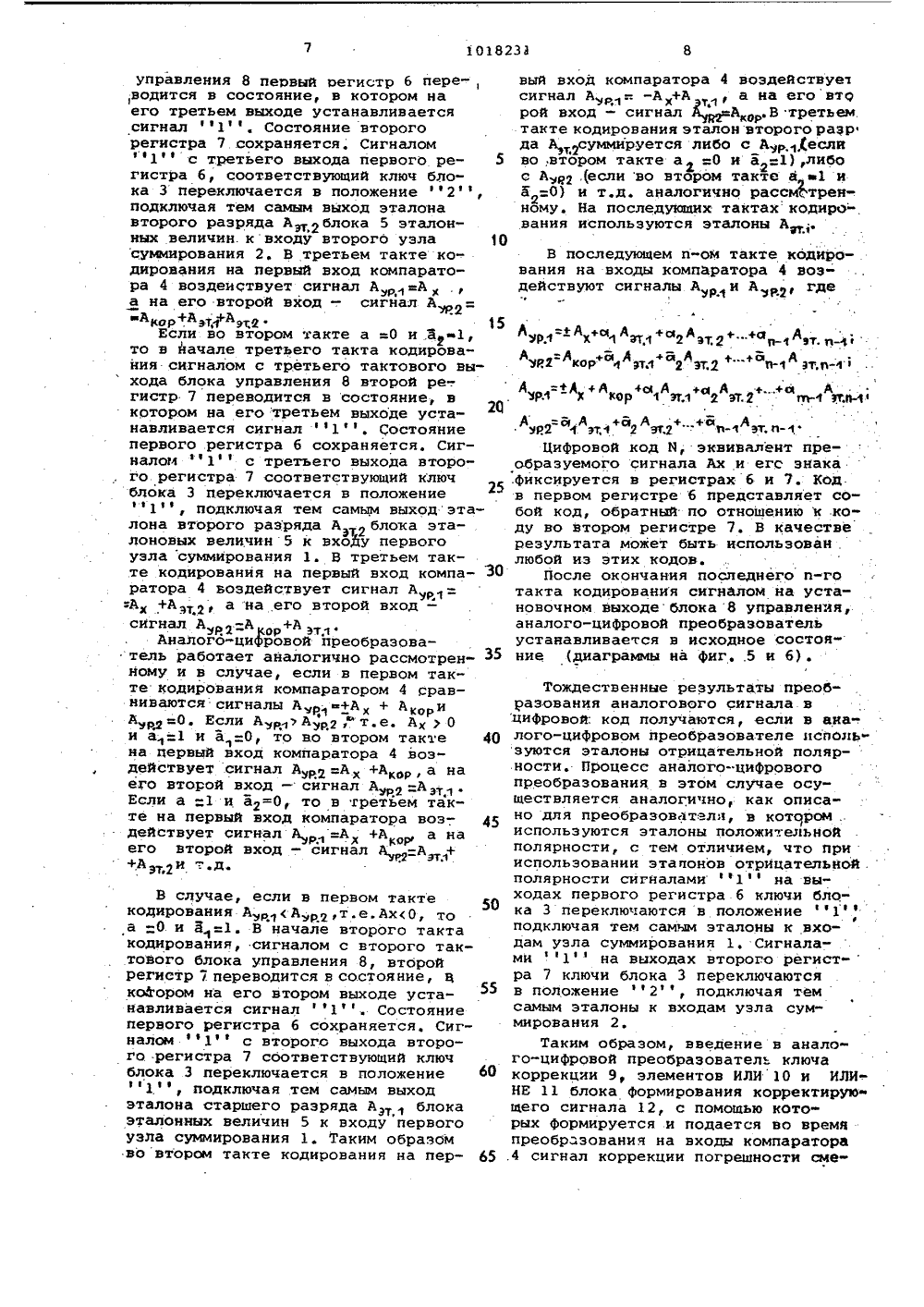

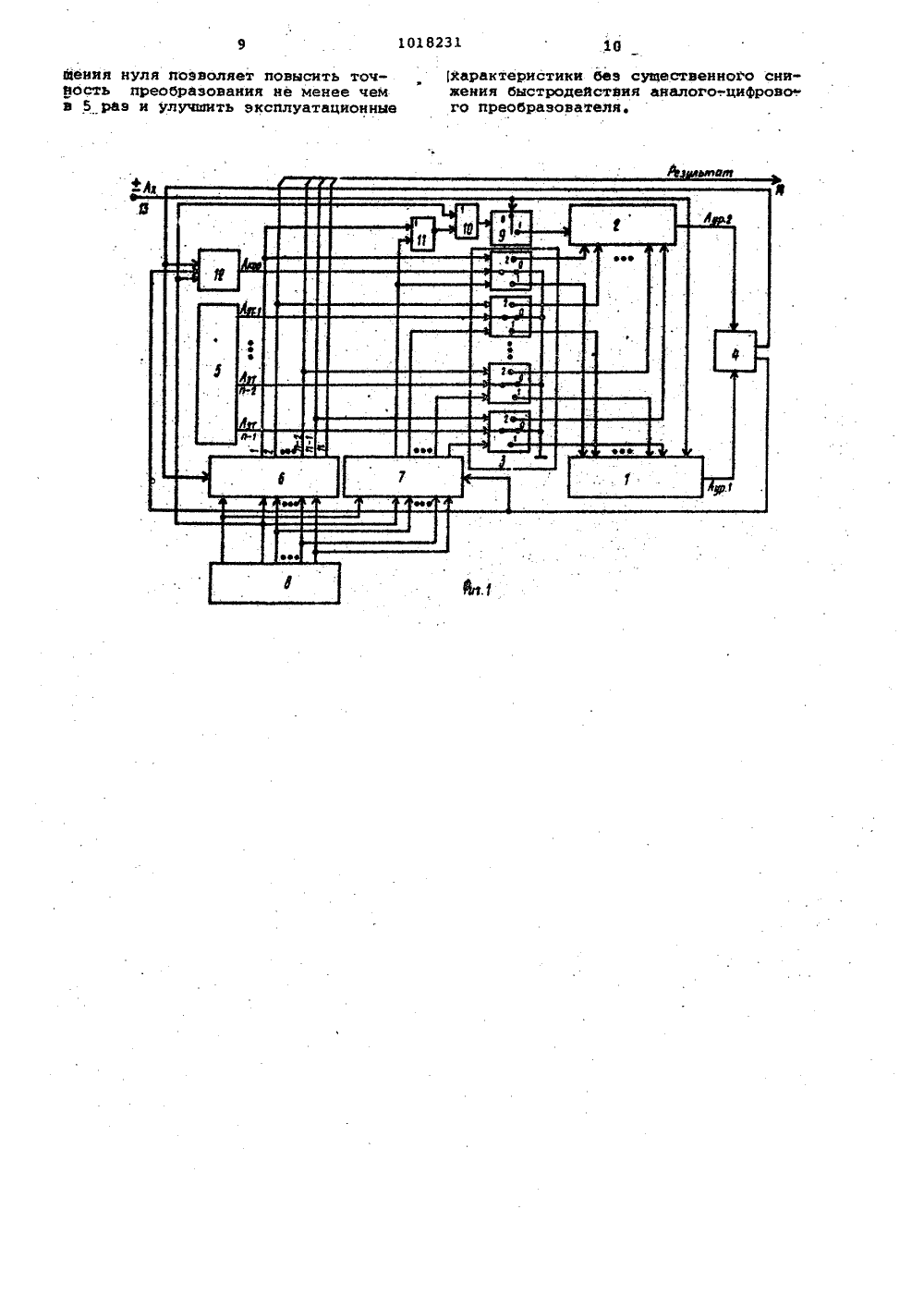

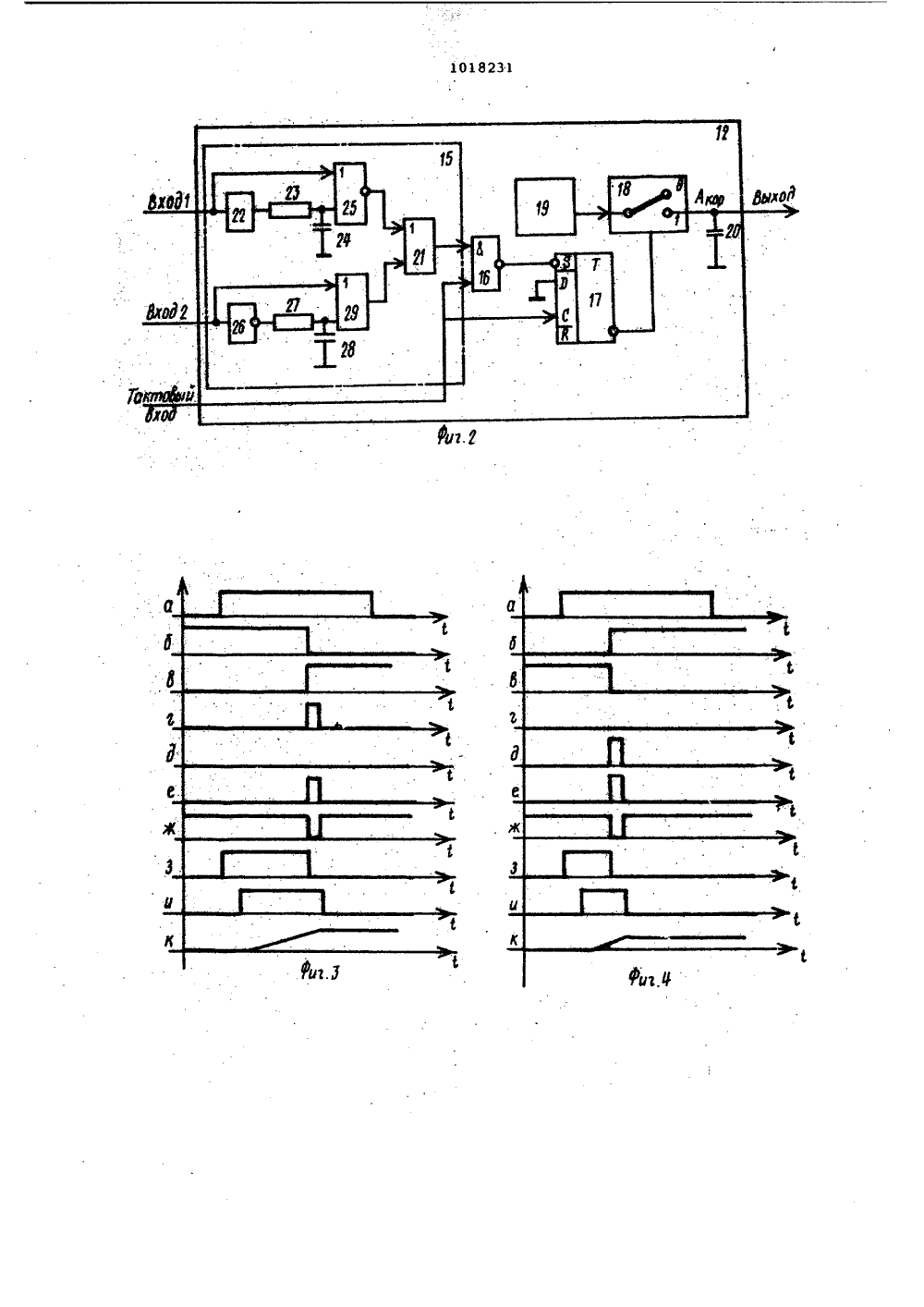

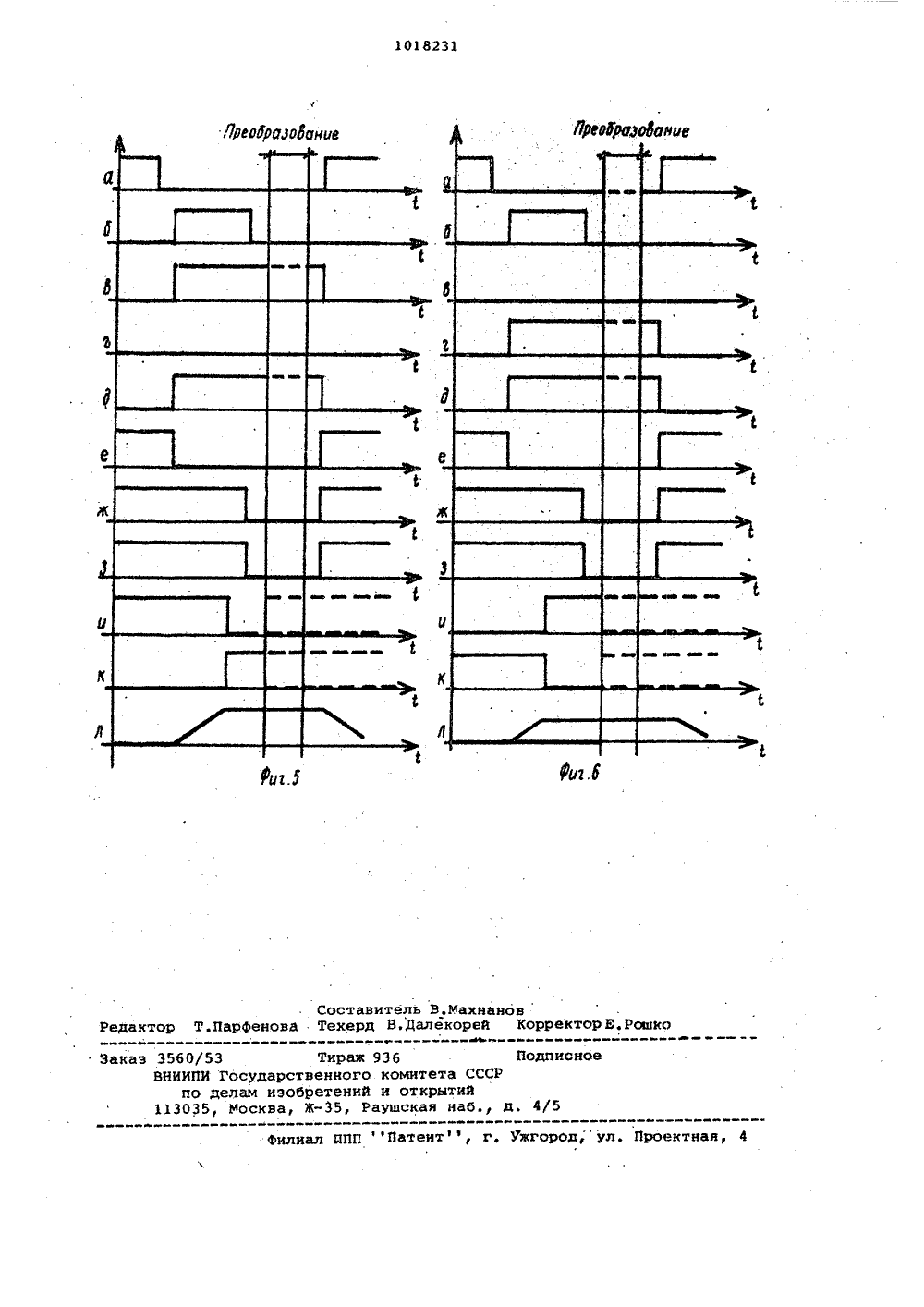

: ОЗ:ЯЮИРЮЕСВ РЕСПУБЛИК МСУДАРСТВЕННЫЙ КОМ паФПАЫИМНПВЮ ОПИСАНИЕ ИЗОБРЕТЕК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ИЯ(72) П.С.Клочан и В.Н.Лаврентьев (71) Ордена Ленина институт кибернетики АН Украинской ССР,2. Проблемы создания преобразователей формы информации. Тезисы докладов 1 У Всесоюзного симпозиума.1980, ч.2, с. 12-20, рис. 3 (прототип).(54)(57) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ БИПОЛЯРНЫХ СИГНАЛОВ, содержащий первый узел суммирования, первый вход которого подключен к шийе преоб разуемого сигнала, остальные входы соединены с первыми выходами ключей блока ключей, а выход соединен с пер вым входом компаратора, второй вход которого соединен с выходом второго узла суммирования, входы которого со единены с вторыми выходами ключей блока ключей, третьи выходы которых подключены к шине нулевого потенциала, а потенциальные входы .ключей,кро ме первого, поразрядно .подключены к выходам блока эталонных величин, пе вые и вторые управляющие входы ключе блока ключей пораэрядйо соединены с Об Ю Ф выходами соответственно первого и второго регистров, входы установки в фнульф и управляющие входы которых .подключены к соответствующим входам блока управления, а входы установки в фединицуе соединены соответственно с первым и вторым выходами компаратора, выходы первогоре-. гистра, кроме первого, подключены к шине вывода результатов преобразования, о т л и ч а ю щ и й с я тем, что, с цельюповышения точности преобразования,.в него введены ключ коррекции, элементы ИЛИ и ИЛИ-НЕ и блок формирования корректирующего сигнала, причем дополнительный вход второго узла суммирования подключен 3 к шине преобразуемого сигнала через ключ коррекции, управляющий вход которого соединен с выходом элемента аав ИЛИ, первый выход которого соединен . мее с выходом элемента ИЛИ-НЕ, входы ко торого подключены к первым выходам первого и второго регистров, первыеуправляющие входы которых соединены с вторым входом элемента ИЛИ и первым входом блока формирования корректирующего сигнала, второй и третий входУ которого подключены к выр- ходам компаратора, а выход - к пойтенциальному входу первого ключаблока ключей.подключены к выходам блока эталонных величин, первые и вторые входы управляющих ключей блока ключей поразрядно соединены с выходами соответственно первого и второго регистров, входы установки в О и управляющие входы .которых подключены к соответствующим выходам блока управления, а входы установки в единицу соединены соответственно с первым и вторым выходами компаратора, выходы первого регист.ра, кроме первого, подключены к шине вывода результатов преобразования, введены. ключ коррекции, элементы ИЛИ и ИЛИ-НЕ и блок Формирования корректирующего сигнала причем дополнительный вход второго узла сум- мирования подключен к шине преобразуемого сигнала через ключ коррекции, управляющий вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом элемеита ИЛИ-НЕ, входы которого 1 подключены к первым выходам первогои второго регистров, первые управляющие входы которых соединены со вторым входом элемента ИЛИ и первым вхо; дом блока формирования корректирующего сигнала, второй и третий входы которого подключены к выходам компаратора, а выход - к потенциальному входу первого ключа блока ключей,На Фиг, 1 изображена Функциональная схема аналого-цифрового преобразователя биполярных сигналов; на фиг.2- блой Формирования корректирующего сигнала; на Фиг. 3 и 4 - временные диаграммы работы блока Формирования,корректирующего сигнала; на фиг. 5 - временные диаграммы работы аналого-цифрового преобразователя для случая ЯзрЪАзрщ, , на фиг,б - то же,для случая Аур А рПреобразователь содержит первый 1 и второй 2 узлы суммирования, блок ключей 3, компаратор 4, блок 5 эталонных величин, первый б и второй 7 регистры, блок 8 управления, ключ 9 коррекции, элемент 10 ИЛИ, элемент 11 ИЛИ-НЕ и блок 12 Формирования корректирующего сигнала. К клемме источника 13 преобразуемого сигнала подключен первый вход первого узла суммирования 1 р остальные его входы соединены с первыми выходами ключей блока 3, а выход соединен с первым входом компаратора 4, второй вход которого .соединен с выходом второго узла 2 суммирования, входы которого соединены с вторыми вйходамй ключей блока З,дополнительный вход второго узла 2 суммирования подключен через ключ 9 коррекция к шине преобразуемого сигнала 13,а третьи выходы ключей блока 3 подключены к шине нулевого потенциала. Потенциальные входы ключей блока 3, ,кроме первого ключа, поразрядно подИзобретение относится к вычислительной и электроизмернтельнойтехнике и может быть использовано вкачестве самостоятельного блока икак составная часть различных устройств, в которых осуществляется 5преобразование аналоговых сигналов в цифровые коды,Известны аналого-цифровые преобразователи биполярных сигналов,которых с целью сокращения вреени преобразования, уравновешивающий сигнал Формируется из разнополярных дискретных эталонов 11 3.Известен аиалого-цифровой преобразователь биполярных сигналов,содержащий первый узел суммирования, первый вход которого подключен к шине преобразуемого сигнала, остальные входы соединены спервыми выходами ключей блока ключей, а выход соединен с первымвходом компаратора., второй вьиодкоторого соединен с выходом второго узла суммирования, входы которого соединены с вторыми выходамиключей блока ключей, третьи выходы которых подключены к шиненулевого потенциала, а потенциапьные входы ключей поразрядно подключены к выходам блока эталонных величин, первые и вторые управляющие З 0входы ключей блока ключей поразрядно соединены с выходами соответ.ственно первого и второго регистров, входы установки в "нуль" иуправляющие входы которых подключены 35к соответствующим выходам блока управления, а входы установки в единицуф соединены соответственно с пер-,вым и вторым выходами компаратора,выходы первого регистратора подключены к шине вывода результатов преобразования 2 1,Погрешность, вызванная неидентичностью параметров входов компаратоР 3параметров узлов суммирования 45и ключей блока ключей, проявляетсякак смещение нуля аналого-цифровогопреобразователя.Цель изобретения - повышение точ -ности преобразования,, Цель достигается тем, что в аналогово-цифровой преобразс атель биполярных сигналов, содержащий пер. -вый узел суюирования, первый входкоторого подключен к шине преобразуемого сигнала, остальные входы со 55единены с первыми выходами ключейблока ключей, а выход соединен с пер.вым входом компаратора, второй входкоторого соединен с выходом второго узла суммирования, входы которого соединены с вторыми выходамиключей блока ключей, третьи выходыкоторых подключены к шине нулевого.величин, первые ивторые управляю-щие входы ключей блока 3 поразряд но соединены с выходами, соответственно, первого 6 и второго 7 регистров, входы установки в фО"5и управляющие входн которых подключены к соответствующим выходам блока 8 управления, а входы установкив фединицуф первого 6 и второго 7 .регистров соединены, соответственно., Щс первым и вторым выходамй компара: -тора 4. К щине вывода результатовпреобразования 14. подключены все,кроме. первого, выходы первого регистра б. Управляющий вход ключа коррекции. 9 соединен с выходом элемента10 КПИ, первый вход которого соеди. нен с выходом элемента 11 ИЛИ-НЕ,входы которого подключены к первымвыходай первого б и второго 7 ре.гистров, первые управляющие входыкоторых соединеныс вторым входомэлемента 10 ИЛИ и первым входом блока 12 формировайия корректирующегосигкала, два других входа которогоподключены к выходам компаратора 4,а выход блока 12 формирования,корректирующего .сигнала 12 соединенс потенциальным входом первого ключа блока 3,Блок 12 формирования корректирующего сигнала вводятся в аналогоцифровой преобразователь биполярныхсигналов для Формирования .корректирующего воздействия смещения нуля иможет быть реализован различным об-, З 5разом. Одна из возможных реализаций .показана на фиг 2, Он:содержит блок .15. Формирования короткихимпульсов,элемент И-НЕ 16, триггер 17, аналоговый ключ 18 У ис очник 19 эталонной .величины и. запоминающий конденсатор 20. Выход .блока 15 Формированйя коротких импульеов соединен спервым. входом элемента И-НЕ 1 б,второй вход которого является тактовым входом блока 12 Формирования кор.ректирующего сигнала и соединен ссинхронизационным входом триггера17, а выход элемента 16 И-НЕ соеди-.нен с входом.установки в 0. триггера 17, выход которогосоединен с 50управляющим входом аналогового ключа 18. Потенциальный вход аналогового ключа 18 подключея к источиику19 эталонной. велйчиаы, а выход аналогового ключа 18. соедийен с .запоминакарпа конденсатором 20.-и является выходом блока 12 Формирования корректирующего сигнала.Блок 15 Формирования коротких импульсов содержит элемент ИЛИ 21.и два 60идентичных формирователя, первый Формирователь содержит элемент НЕ 22,резистор 23, конденсатор. 24 и эле-мент ИЛИ-НЕ 25. Вход элемента НЕ 22является первым входом 24 и элемент ИЛЙ-НЕ 25 Вход элемента НЕ 22 является первым входом блока 12 Формирования корректирующего сигнала исоединен с первым входом элементаИЛИ-НЕ 25, а выход элемента НЕ 22соединен через резистор 23 с конденсатором 24 и вторым входом элемента ИЛИ-НЕ 25, выход которого соединен с первым входом элемента ИЛИ21, выход которого является выходом блока 15 Формирования короткихимпульсов.Второй формирователь содержитэлемент НЕ 26, резистор 27, конденсатор 28 и элемент ИЛИ-ЙЕ 29. Входэлемента НЕ 26 является вторымвходом блока 12 формирования корректирующего сигнала и соединен спервым входом элемента ИЛИ-НЕ 29,а выход элемента НЕ 26 соединенчерез резистор 27: с конденсатором 28и вторым входом элемента ИЛИ .21.В исходном, состоянии на тактовом входе блока 12 (фиг 3.) установлен сигнал.ффОф (диаграмма а),.на его первом входе сигнал ф 1 ф(диаграмма б), на его втором входесигнал фОе (диаграмма в), на выходах элементов ИЛИ-НЕ 25, ИЛИ-НЕ29 и ИЛИ 21 установлены сигналы .фОф(соответственно, диаграммы гд и е),на выходе элемента И-НЕ 16 установлен сигнал е 1 ф.ф (диаграюва ж), навыходе триггера 17 установлен сигналф 10 ф (диаграмма з), аналоговый ключ18 установлен в положение ф.01 ф .(диаграмма и) й запоминающий .конденсатор20 разряжен (диаграмма к) . На выходе блока 12 отсутствует сигнал коррекции,Прн появлении сигнала 1 ф 1 ф на .так"товом входе блока 12 (диаграмма а):на выходе триггера 17 (диаграмма,з)воздействует сигнал ф 1 фф, по которо"му аналоговый ключ 18 устанавливает"ся в положение ф 11 (диаграмма и)и подключает источник 18. эталоннойвеличины к запоминающему конденсатору20. Запоминающий конденсатор 20 заряжается (диаграмма к) и на выходеблока 1 У появляется .сигнал коррекции А , величина которого возрас.-.тает до тех пор,пока на первом входе блока 12 воздействует сигналф 1При изменении на первом входе блока 12 сигнала 11 ффна сигйал110 ф 1 (диаграмма б), элементом ИЛИ- .НЕ 25 Формируется короткий импульс1 ф г, который через элемент ИЛИНЕ 21 поступает на вход элемеятаИ-НЕ 16. Элементом И-НЕ 16 Формируется короткий импульс 0 ф ж, покоторому триггер 17 изменяет своесостояние" (диаграмма з),на его выходЮустанавливается сигнал 1 фО, покоторому аналоговый ключ 18 устанавливается в положение фОфф (диаграмма и) и отключает источник эталонЬ.ной величины 19 от запоминающегоконденсатора 20. На выходе блока 12воздействует корректирующий сигнал Аустановленной величины (диаграмма к)с запоминающего конденсатора 20.Если в исходном состоянии на первомвходе блока 12 установлен сигнал "О"(диаграмма б , фиг. 4), а:на еговтором входе сигнал 1 (диаграмма в, фиг, 4;, то блок формирования корректирующего сигнала 12 ра Оботает (Фиг. 4), как и в предыдущемслучае (фиг, 4) с тем лишь отличием,что при изменении сигнала 11 насигнал. 0 на втором входе блока12 (диаграмма в), Формирование корот кого импульса ф 1 д осуществляется во втором формирователе коротких импульсов элементом ИЛИ-НЕ 29.В аналого-цифровом преобразователе, для уравновешивания биполярного преобразуемого сигнала +Ах , используются эталонные величины одного знака, причем могут быть использованы как . эталоны положительной полярности, так и эталоны отрицательной полярности. .Рассмотрим работу аналого-цифрового преобразователя при использовании положительных эталонных величин А и Аэт 1 фВ исходном состоянии на установочном выходе блока управления 8 воз О действует сигнал ф-ф 1 ф, на выходах регистров б и 7 воздействуют сигналы О", ключи блока установлены в положение О, Выходы всех разрядных эталонов блока эталонных величин 5 и 35 . вЫход блока 12 формирования корректирующего сигнала отключены от узлов суммирования 1 и 2, Ключ коррекции 9 установлен в положение 11, преобразуемый сигнал йАх через первый 40 узел суммирования 1 подключен к пер.,вому входу компаратора 4,а через аналоговый ключ 9 и второй узел суммирования 2 подключен к второму входу компаратора 4, Если сигнал Ар 1 45 на первом входе компаратора 4 посвоей величине больше сигнала А 2 наего втором входе, т,е, АрАр 2, то на выходах компаратора 4 в исходном . состоянии установлены сигналы а:1и ВжО.Если же Аур 1 с А р 2, то В исходном.состОянии аО, а а 1. После окончания действйя сигнала ф 1 и установки сигнала 0 на установочномвыходе блока управления 8 (диаграмма а), .на его первом тактовом выходеустанавливается сигнал ф 1 (диаграмма б), по которому первый регистр6 переводится в состояние, в котором на его первом выходе. устанавливается 60сигнал 1 (диаграмма в), Состояние Втррого регистра 7 сохраняется (диаграмма г).Сигналом фф 1 с первого выхода регистра б соответствующий ключблока 3 переключается в положение ф 2(диаграмма д), подключая тем самымвыходблока формирования корректирующего сигнала 12 к входу второго узласуммирования 2. На выходе элементаИЛИ-НЕ 11 устанавливается сигнал 0(диаграмма е), однако на выходе элемента ИЛИ 10 сохраняется сигнал .1(диаграмма ж), и ключ коррекции 9остается в положении ф 1 (диаграмма з) до окончания такта коррекции..На второй вход компаратора 4 воздействует сигнал А -А +Ао , величинакоторого возрастает вследствие нарастания А (диаграмма л) до тер пор пока на вйходе компаратора 4 не установится сигнал фО.ф (диаграмма и), покоторому прекращается нарастание сигнала А на выходе блока 12 формирования корректирующего сигнала (диаг. -рамма л). После окончания такта коррекции, на выходе элемента ИЛИ 10устанавливается сигнал О (диаграмма ж), по которому аналоговый ключ9 устанавливается в положение 0(диаграмма з) и отключает сигнал +Ахот узла суммирования 2,Коррекция погрешности смещения нуляв этом случае осуществляется аналогично рассмотренному, с тем лишь отличием, что по сигналам а-О и а:1 навыходах компаратора 4 (диаграммы и,к), в 1 ф 1 переводится второй регистр 7 (диаграмма г), а соответствующий ключ блока 3 переключается в положение.ф 1 (диаграмма д), подключаятем самым выход блока формирования корректирующего сигнала 12 к входу первого узла суммирования 1.После окончания такта коррекции начинается цикл преобразования биполярного сигнала +Ах, состоящий из и тактов кодирования ( где и - количестворазрядов выходного кода И), В первомтакте кодирования сигналы Ар 1 +Аи Ау 2 дАорсравниваются компаратором4, Если А ъА 2., т,е. А)0, то аа 1,ааО.Ъ начале второго такта кодированиясигналом с второго тактового выходаблока 8 управления первый регистр бпереводится .в состояние, в которомна его втором выходе устанавливаетсясигнал 1 ф. Состояние второго регистра 7 сохраняется. Сигналом ф 11 1с второго выхода первого регистра бсоответствующий ключ блока 3 переключается в положение ф 2, подключая тем самым выход эталона старшего разряда А блока эталонныхвеличин 5 к входу второго узла суммирования 2. Таким образом, во втором такте кодирования на первыйвход компаратора 4 воздействует сигнал А,р,-А х а на его второй вход -сигнал А д-А +А . Если во второмтакте а -1 и а :О, то в началетретьего такта кодирования сигналом сс третьего тактового выхода блока,водится в состояние, в котором наего третьем выходе устанавливаетсясигнал фф 11. Состояние второгорегистра 7 .сохраняется. Сигналом" 1 ф с третьего выхода первого регистра б, соответствующий ключ блока 3 переключается в положение 121,подключая тем самым выход эталонавторого разряда А т 2 блока 5 эталонных величин.к входу второго узласуычирования 2. В третьем такте кодирования на первый вход ксмпаратора 4 воздеиСтвует сигнал АрАа на его второй вход - сигнал ААкор+Аэт 1+АэтйЕсли во втором такте а :О и .321,то в начале третьего такта кодирования сигналом с третьего тактового выхода блока управления 8 второй ре-.гистр 7 переводится в состояние, вкотором на его третьем выходе устанавливается сигнал 1 ф, Состояниепервого регистра б сохраняется, Сигналом 1 ф 1 с третьего выхода второго регистра 7 соответствующий ключблока 3 переключается в положениефф 1 ф, подключая тем самым выход эталона второго разряда А блока эталоновых величин 5 к входу первогоузла суммирования 1. В третьем такте кодирования на первый вход компаратора 4 воздействует сигнал Ар 1-"А +А 2, а на его второй вход -Аурт А +А этур. 2- КорАналого-цифровой йреобразователь работает аналогично рассмотрен- З 5ному и в случае, если в первом такте кодирования компаратором 4 сравниваются сигналы А р +А + А иЧР 1 Х КоРАр 2-О. Если А,р.,э АУр 2, т.е. АхОи а:1 и а:О, то во втором такте 40на первый вход компаратора 4 воздействУет сигнал Ар 2:А +А р,а наеГо втоРой вхоД - сйгнал А 2 -Аэт.Если а -1 и а 2=0, то в третьем такте на первый вход компаратора воздействует сигнал А :А +А а наего второй вход - сигнал А, :А ++А 2 и т.д,10В последующем и-ом такте кМйро- .вания на входы компаратора 4 воздействуют сигналы А 1 и АР 2, где 15УР.1 - х 1 эт,1 2 зт.2+"+яэт.п А:М +а А +а А а Аур 2=Акор 1 эт,1 2 эт,2- п 1 эт,п 1) 50 55 60 65 В случае, если в первом такте кодирования Ар 1 Ар 2,т.е.АхО, то а -О.и а:1. В начале второго такта кодирования, сигналом с второго тактового блока управления 8, второй регистр 7 переводится в состояние, д койором на его втором выходе устанавливается сигнал ф 1 ф. Состояние первого регистра б сохраняется, Сигналом 1 ф 1 фф с второго выхода второго. регистра 7 соответствующий ключ блока 3 переключается в положение 1 фф, подключая тем самым выход эталона старшего разряда Аэблока эталонных величин 5 к входу первого узла суммирования 1. Таким образом во втором такте кодирования на первый вход компаратора 4 воздействуе 1 сигнал А,рэ - -А+А а на его вто рой вход - сигналъА .В третьем такте кодирования эталон второго раЗр да А 2 суммируется либо с АУР,внесли во,втором такте а 2 -О и а:1),либо с А,ц 2 .(если во втором такте а е 1 и а :0) и т.д. аналогично рассмотренному. На последующих тактах кодиро- вания используются эталоны А ур 1 " х хор 1 эт.1 2 эт 2 нм эт.иур 2 1 эт,1 2 эт.2иэт, дЦифровой .код И, эквивалент преобразуемого сигнала Ах и егс знака фиксируется в регистрах б и 7. Код в первом регистре б представляет собой код, обратный по отношению к коду во втором регистре 7. В качестве результата может быть использован . любой из этих кодов.После окончания последнего и-го такта кодирования сигналом йа установочном выходеблока 8 управления, аналого-цифровой преобразователь устанавливается в исходное состояние (диаграммы на фиг.5 и б) . Тождественные реэультаты преобразования аналогового сигнала в цифровой: код получаются, если в аналого-циФровом преобразователе используются эталоны отрицательной полярности. Процесс аналого-цифрового преобразования в этом случае осуществляется аналогично, как описано для преобразователя, в которомиспользуются эталоны положительной полярности, с тем отличием, что при использовании эталонов отрйцательной . полярности сигналами ф 1 на выходах первого регистра б ключи блока 3 переключаются в положение ф 1 подключая тем самым эталоны к входам узла суммирования 1, Сигналами 1 на выходах второго регист-ра 7 ключи блока 3 переключаются в положение 2 ф, подключая тем самым эталоны к входам узла суммирования 2.Таким образом, введение в аналого-цифровой преобразователь ключа коррекции 9, элементов ИЛИ 10 и ИЛИ-. НЕ 11 блока формирования корректирую щего сигнала 12, с помощью которых формируется и подается во время преобр-зования на входы компаратора .4 сигнал коррекции погрешности сме 1 О 182 З 1щения нуля позволяет повысить точность преобразования не менее чем в 5 раз и улучшить эксплуатационные 1 Марактеристики без существенного снижения быстродействия аналого-.цифрово;.го преобразователяСоставактор Т.Парфенова Техерд тель Э.махнанов В,Далекорей Ко ктор Е. Рошк н 5 Заказ 3560/53 ВНИКНИ Госуд по делам И 3035, МоскТиРаж 936 Птвенного комитета СССРбретений и открытий Ж, Раушская наб. д. иал ИПП Патент, г. Ужгород,ул. Проектная, 4

СмотретьЗаявка

3359578, 30.11.1981

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УССР

КЛОЧАН ПЕТР СТЕПАНОВИЧ, ЛАВРЕНТЬЕВ ВАСИЛИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 13/17

Метки: аналого-цифровой, биполярных, сигналов

Опубликовано: 15.05.1983

Код ссылки

<a href="https://patents.su/8-1018231-analogo-cifrovojj-preobrazovatel-bipolyarnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой преобразователь биполярных сигналов</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Устройство для преобразования напряжения в код

Случайный патент: Приспособление для лужения выводов радиоэлементов в упаковке