Преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

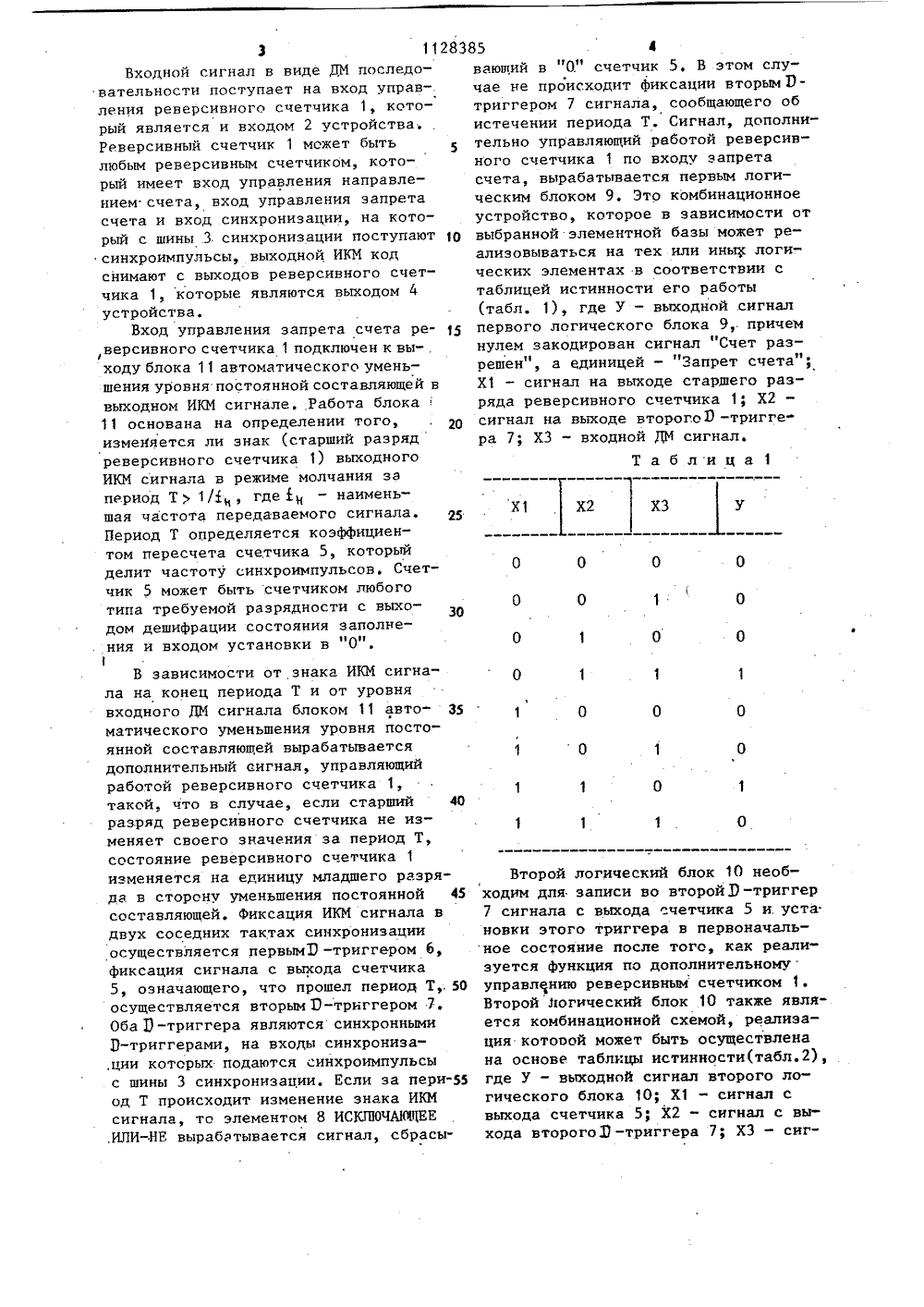

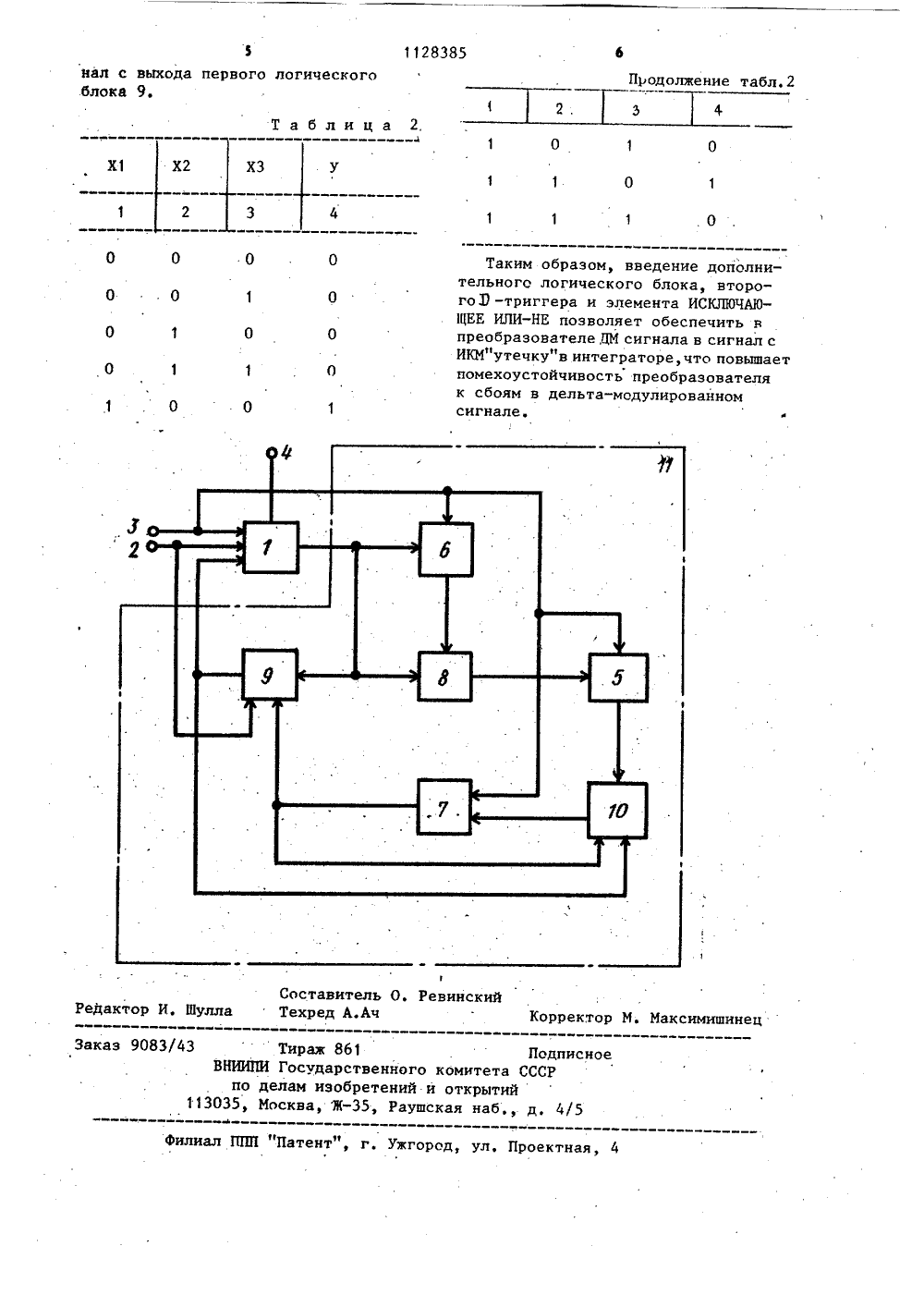

/СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУ БЛИН 0% (11) ЕЛЬ ДЕ ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЦТИЙ ОПИСАНИЕ ИЗОБРЕ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Ленинградский электротехнический институт связиим. проф. М.А. Бонч-Бруевича (53) 621.376,5(088,8)(56) 1, ТЕЕЕ. Тгапвасг 1 опз оп Зо 1 ЫБеаге Сгсц 3.г.з, 1981, ч. 2. В 4, р, 31.2. Авторское свидетельство СССР 9 930664, кл, Н 03 К 13/22,24,0980 (прототип).(54)(57) ПРЕОБРАЗОВАТ ЛЬТАМОДУЛИРОВАННОГО СИГНАЛА В СИГНАЛ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ, содержащий реверсивный счетчик, первый З-триггер, 3 -вход которого соединен с выходом старшего разряда реверсив-. ного счетчика, а вход синхронизации - с шиной синхронизации, счетчик и первый логический блок, о т л и ч а - ю щ и й с я тем, что, с целью повы- . шения помехоустойчивости, в него введены второй логический блок, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и второй Э-триггер, вход синхронизации которого соединен с шиной синхронизации входом синхронизации реверсивного счетчика и входом счетчика, выход кбторого соединен с первым входом второго логического блока, а вход уста" нонки в "0" счетчика - с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый вход которого соединен с выходом первогоП-триггера, а второй .вход подключен кВ -входу первого Р-триггера и первому входу первого логического блока, второй вход которого сое-динен с вторым входом второго логического блока и выходом второго Р-триггера, третий вход первого ло- Сев гнческого блока соединен с входом устройства и входом управления ревер- а сивного счетчика, а выход - с входом запрета счета реверсивного счетчика и третьим входом второго ло.гического блока, выход которого соединен сЗ -входом второгоЭ -триггера;Изобретение относится к импульсной технике и может быть использовано в системах обработки и передачи цифровых сигналов, в которых применяется дельта-модуляция (З) и 5 импульсно-кодовая модуляция (ИКМ).Известно устройство для преобразования ДМ сигналов в ИКМ, содержащее сумматоры, резисторы, умножители и постоянные запоминающие устройства 11 10Недостатком этого устройства является невысокая помехоустойчивость,Наиболее близким к изобретению техническим решением является устройство для преобразования дельта модулированных сигналов в сигнал с ИКМ, содержащее реверсивный счетчик, 1)-триггер, 3 -вход которого соединен с выходом старшего разряда реверсивного счетчика, а вход синхронизации - 20 с шиной синхронизации, управляемый делитель частоты, например, счетчик и первый логический блок, а также высокочастотный дельта-модулятор, прямой и инверсный выходы которого 25 через элементы И подключены к входу управления реверсивного счетчика, и генераторы тактовых импульсов 2 .Недостатком известного устройства является низкая помехоустойчивость, что вызывает изменение уровня постоянной составляющей в выходном ИКМ сигнале при возникновении сбоев в ДМ сигнале и приводит к искажению передаваемых сигналов. Это обусловлено тем, что рверсивные счетчики являют. ся идеальными интеграторами, вследствие чего они накапливают ошибки. Цель изобретения - повышение помехоустойчивости.Цель достигается тем, что в преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией, содержащий реверсивный счетчик, первыйЗ-триггер, Р - вход которого соединен с,выходом старшего разряда реверсивного счетчика, а вход синхронизации - с шиной синхронизации, счетчик и первый логический блок, введены второй логи .ческий блок, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и второй 2 -триггер, вход синхронизации которого соединен с шиной синхронизации, входом синхронизации реверсивного счетчика и входом счет чика, выход которого соединен с первым входом второго логического блока, ,а вход установки в "0" счетчика - с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ,первый вход которого соединен с выходом первого Э -триггера, а второй входподключен к Э -входу первого О -триггера и первому входу первого логического блока, второй вход которогосоединен с вторым входом второго логического блока и выходом второго3-триггера, третий вход первого блокасоединен с входом устройства и входомуправления реверсивного счетчика, авыход - с входом запрета счета реверсивного счетчика и третьим входомвторого логического блока, выход которого соединен сР -входом второгод-триггера,На чертеже представлена функциональная схема устройства.Устройство содержит реверсивный счетчик 1, вход управления которого соединен с входом 2 устройства, вход синхронизации соединен с шиной 3 синхронизации, выходы реверсивного счетчика 1 являются выходом 4 устрой ства, счетчик 5, первый и второй Р- триггеры 6 и 7, элемент 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый и второй логические блоки 9 и 10, причем шина 3 синхронизации соединена с входом счетчика 5 и входами синхронизации первого и второго 2 -триггеров 6 и 7, авыход старшего разряда реверсивногосчетчика 1 подключен к первому входупервого логического блока 9, к первому входу элемента 8 ИСКЛЮЧАЮЩЕЕИЛИ-НЕ и к входу первогоЮ -триггера6, выход которого соединен с вторымвходом элемента 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ,выход которого подключен к входуустановки в "0" счетчика 5, а выходсчетчика 5 - к первому входу второгологического блока 10, выход которого соединен с 3 -входом второго 1)триггера 7, выход которого подключенк вторым входам первого и второгологических блоков 9 и 10, третийвход первого логического блока 9подключен к входу 2 устройства, авыход - к входу запрета счета реверсивного счетчика 1 и третьему входувторого логического блока 10.Счетчик 5, 2 -триггеры 6 и .7, элемент 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, блоки 9и 10 образуют блок 11 автоматического уменьшения уровня постоянной составляющей в выходном ИКМ сигнале,Устройство работает следующим образом,85 4вающий в "О." счетчик 5, В этом случае не происходит фиксации вторым 0 триггером 7 сигнала, сообщающего обистечении периода Т. Сигнал, дополнительно управляющий работой реверсивного счетчика 1 по входу запретасчета, вырабатывается первым логическим блоком 9. Это комбинационноеустройство, которое в зависимости отвыбранной элементной базы может реализовываться на тех или иных логических элементах в соответствии стаблицей истинности его работы(табл. 1), где У - выходной сигналпервого логического блока 9,. причемнулем закодирован сигнал "Счет разрешен", а единицей - "Запрет счета";Х 1 - сигнал на выходе старшего разряда реверсивного счетчика 1; Х 2 -сигнал на выходе второго 2 -триггера 7; ХЗ - входной ДМ сигнал. Т а б л и ц а 1 ХЗ у 0 О 0 1 0 0 0 О 0 0 0 0 0 Второй логический блок 10 необходим для записи во второй 3 -триггер 7 сигнала с выхода четчика 5 и. уста новки этого триггера в первоначальное состояние после того, как реализуется функция по дополнительному. управлению реверсивным счетчиком Второй логический блок 10 также является комбинационной схемой, реализация котовой может быть осуществлена на основе таблицы истинности(табл.2), где У - выходной сигнал второго логического блока 10; Х 1 - сигнал с выхода счетчика 5; Х 2 - сигнал с выхода второго,0 -триггера 7; ХЗ - сиг 3 11283Входной сигнал в виде ДМ последовательности поступает на вход управ-, ления реверсивного счетчика 1, который является и входом 2 устройства. Реверсивный счетчик 1 может быть любым реверсивным счетчиком, который имеет вход управления направлением счета, вход управления запрета счета и вход синхронизации, на который с шины 3. синхронизации поступают 1 О синхроимпульсы, выходной ИКМ код снимают с выходов реверсивного счетчика 1, которые являются выходом ч устройства,ход управления запрета счета ре ,версивного счетчика 1 подключен к выходу блока 11 автоматического уменьшения уровня постоянной составляющей в выходном ИКМ сигнале, Работа блока 11 основана на определении того, измеияется ли знак (старший разряд реверсивного счетчика 1) выходного ИКМ сигнала в режиме молчания за период Т1/1, где 1 - наименьшая частота передаваемого сигнала. 25. Период Т определяется коэффициентом пересчета счетчика 5, который делит частоту синхроимпульсов. Счетчик 5 может быть счетчиком любого типа требуемой разрядности с выхо 30 дом дешифрации состояния заполнения и входом установки в "О". 0 1В зависимости от знака ИКМ сигна 1 ла на конец периода Т и от уровня входного ДМ сигнала блоком 11 авто 1 О матического уменьшения уровня постоянной составляющей вырабатывается дополнительный сигнал, управляющий работой реверсивного счетчика 1,1 такой, 4 то в случае, если старший40 разряд реверсивного счетчика не из меняет своего значения за период Т, состояние реверсивного счетчика 1 изменяется на единицу младшего разряда в сторону уменьшения постоянной 45 составляюшей, фиксация ИКМ сигнала в двух соседних тактах синхронизации осуществляется первыми -триггером 6, фиксация сигнала с выхода счетчика 5, означающего, что прошел период Т 50 осуществляется вторым 2-триггером 7. Оба Д -триггера являются синхронными Э-триггерами, на входы синхрониза,ции которых подаются синхроимпульсы с шины 3 синхронизации. Если за период Т происходит изменение знака ИКМсигнала, тс элементом 8 ИСКЛЮЧАНФЕЕ1128385 Продолжение табл,2 Э 4 Таблица 2,0 Х 1 Х 2 ХЗ у 0 0 0 0 0 0 О 0 0 0 0 0 0 0 0 Составитель Техред А.Ач дактор И. Шулла аксимишинец Заказ 9083/ Тираж 861 Государственноелам изобретениосква, Ж, Ра ПодписССР ВНИИПИ по 113035, о комитета и открыти шская наб,"Патент" лиал нал с выхода первого логическогоблока 9. Таким образом, введение дополнительного логического блока, второ- гоЗ -триггера и элемента ИСКЛЮЧй 0- ЩЕЕ ИЛИ-НЕ позволяет обеспечить в преобразователе ДМ сигнала в сигнал с ИКМ"утечку"в интеграторе,что повышает помехоустойчивость преобразователя к сбоям в дельта-модулированном сигнале.М евинскийКорректо Ужгород, ул. Проектная,

СмотретьЗаявка

3589898, 06.05.1983

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

БРУНЧЕНКО АЛЕКСАНДР ВАЛЕНТИНОВИЧ, ВЛАСЮК ЮРИЙ СТЕПАНОВИЧ, ОХИНЧЕНКО ЕЛЕНА ПАВЛОВНА

МПК / Метки

МПК: H03K 13/24

Метки: дельта-модулированного, импульсно-кодовой, модуляцией, сигнал, сигнала

Опубликовано: 07.12.1984

Код ссылки

<a href="https://patents.su/4-1128385-preobrazovatel-delta-modulirovannogo-signala-v-signal-s-impulsno-kodovojj-modulyaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией</a>

Предыдущий патент: Преобразователь напряжения в код

Следующий патент: Коммутатор с переменой знака выходного напряжения

Случайный патент: М сине-зеленой водоросли anabaena var1abilisк-1