Управляющая вычислительная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

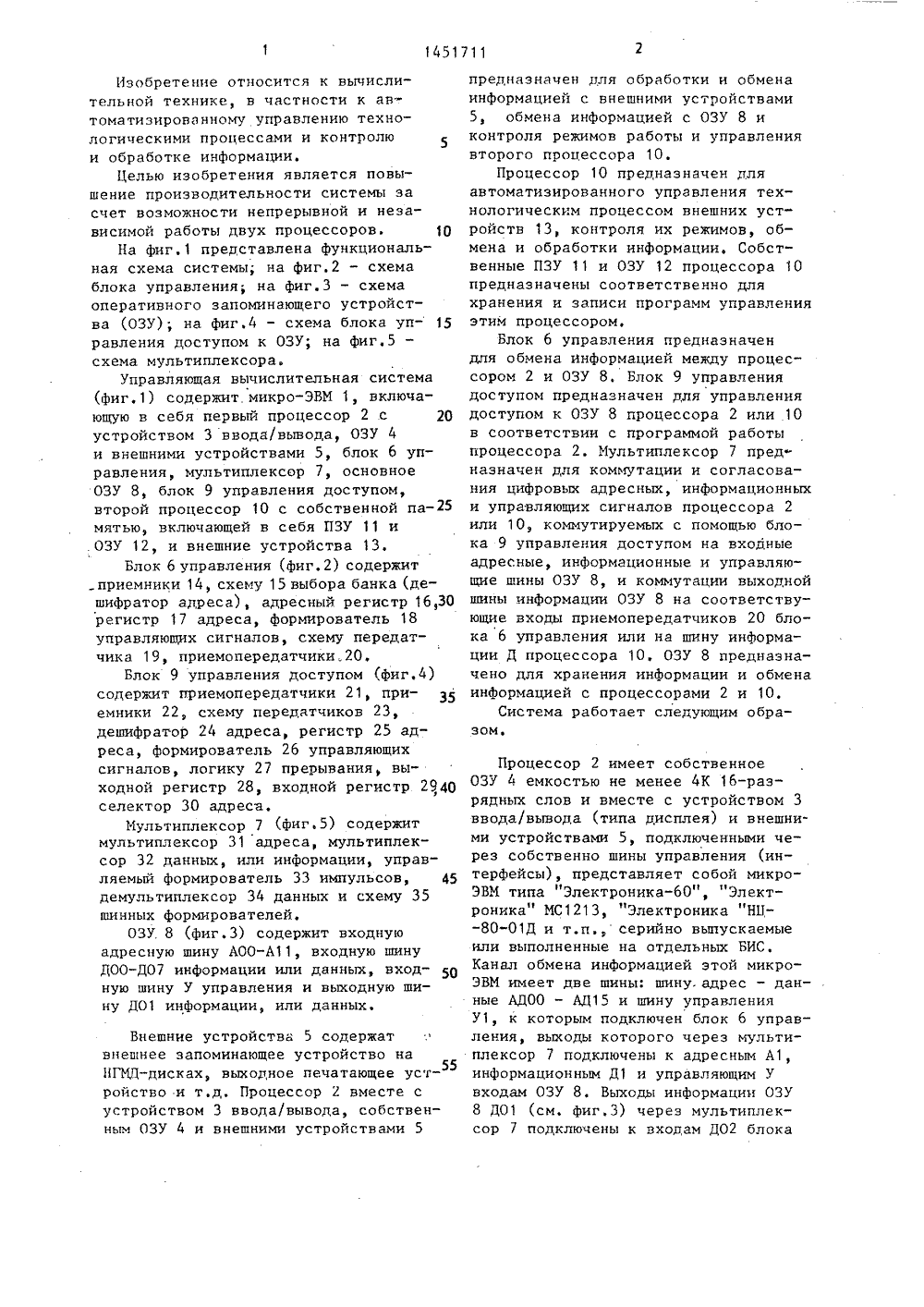

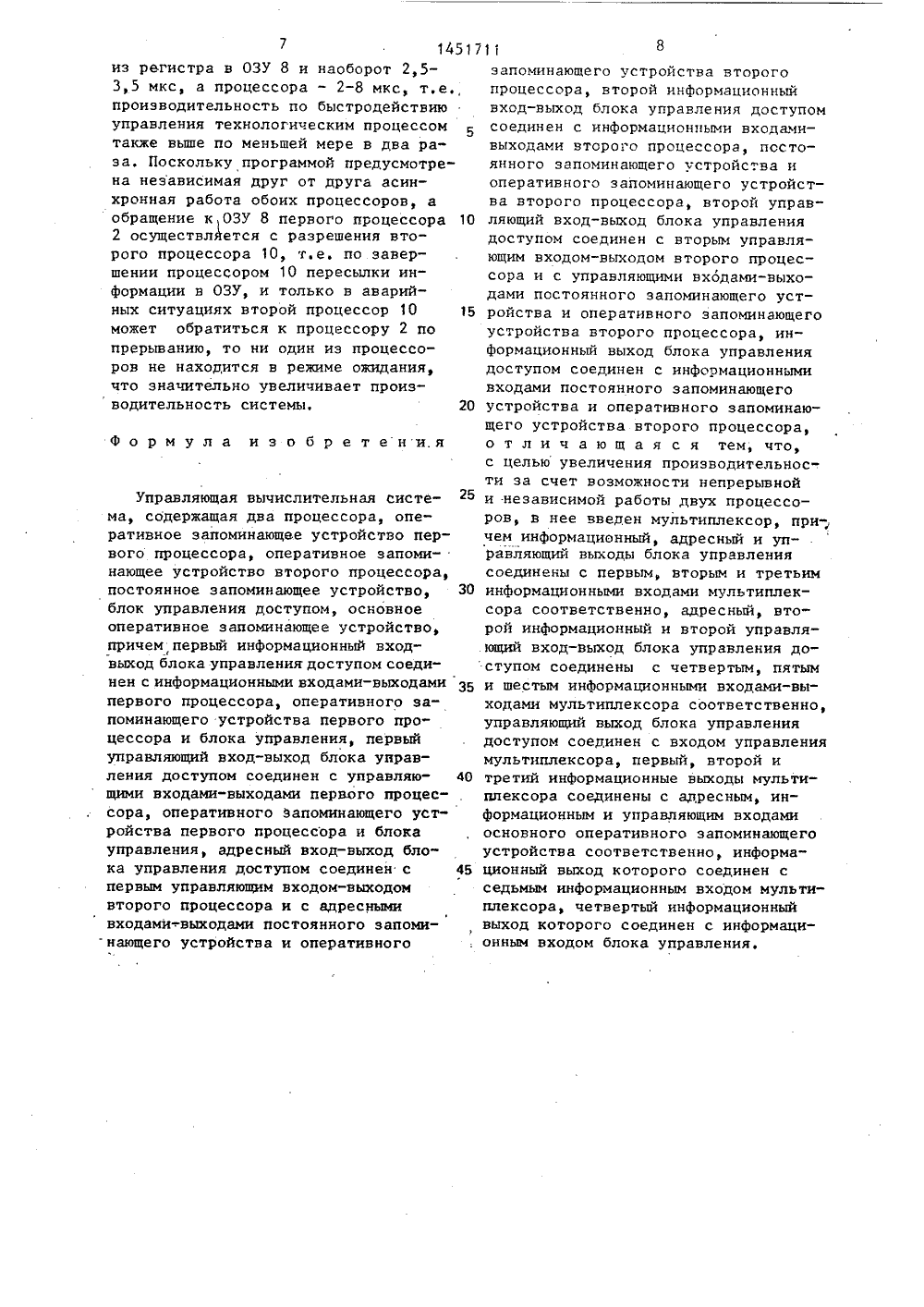

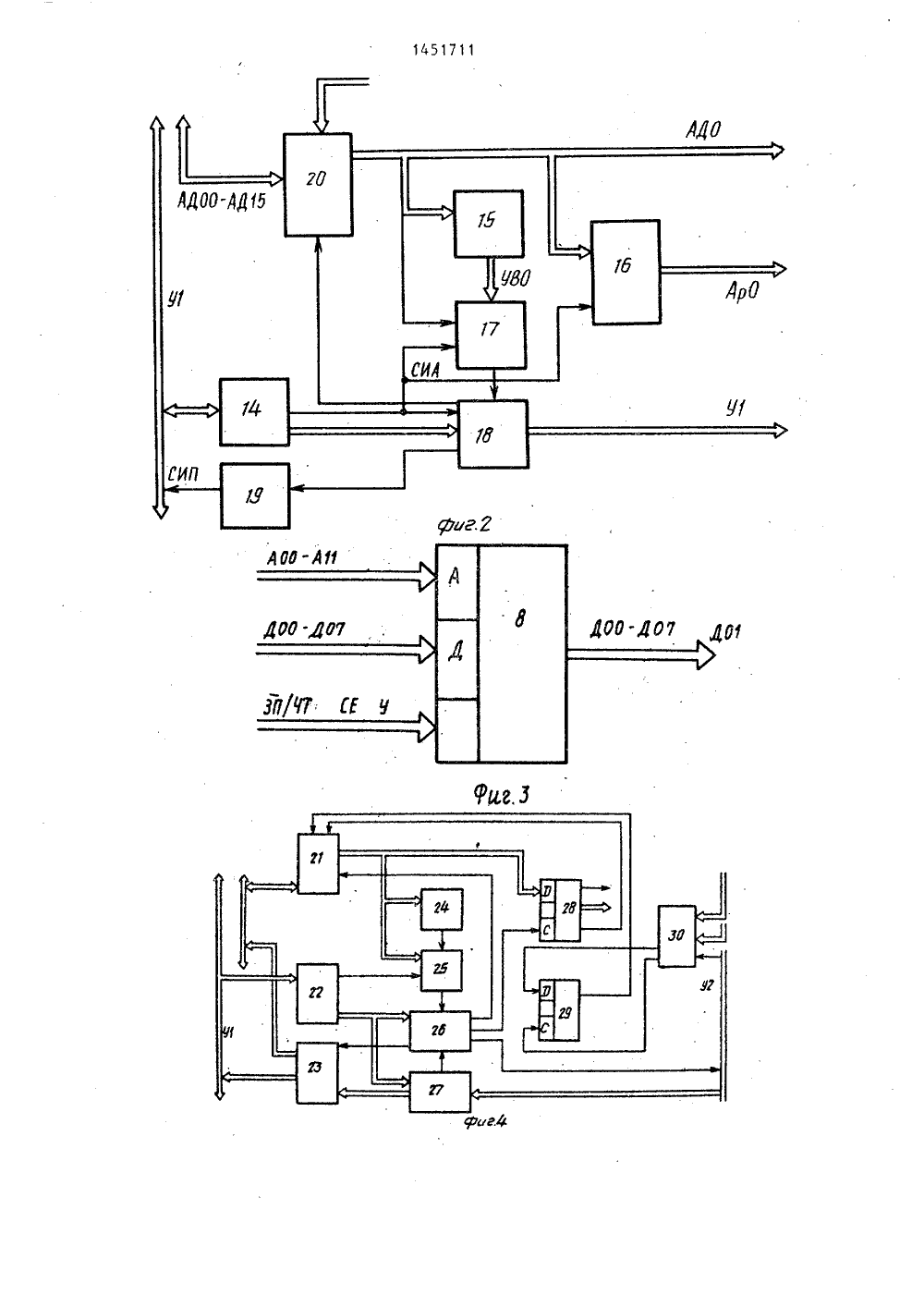

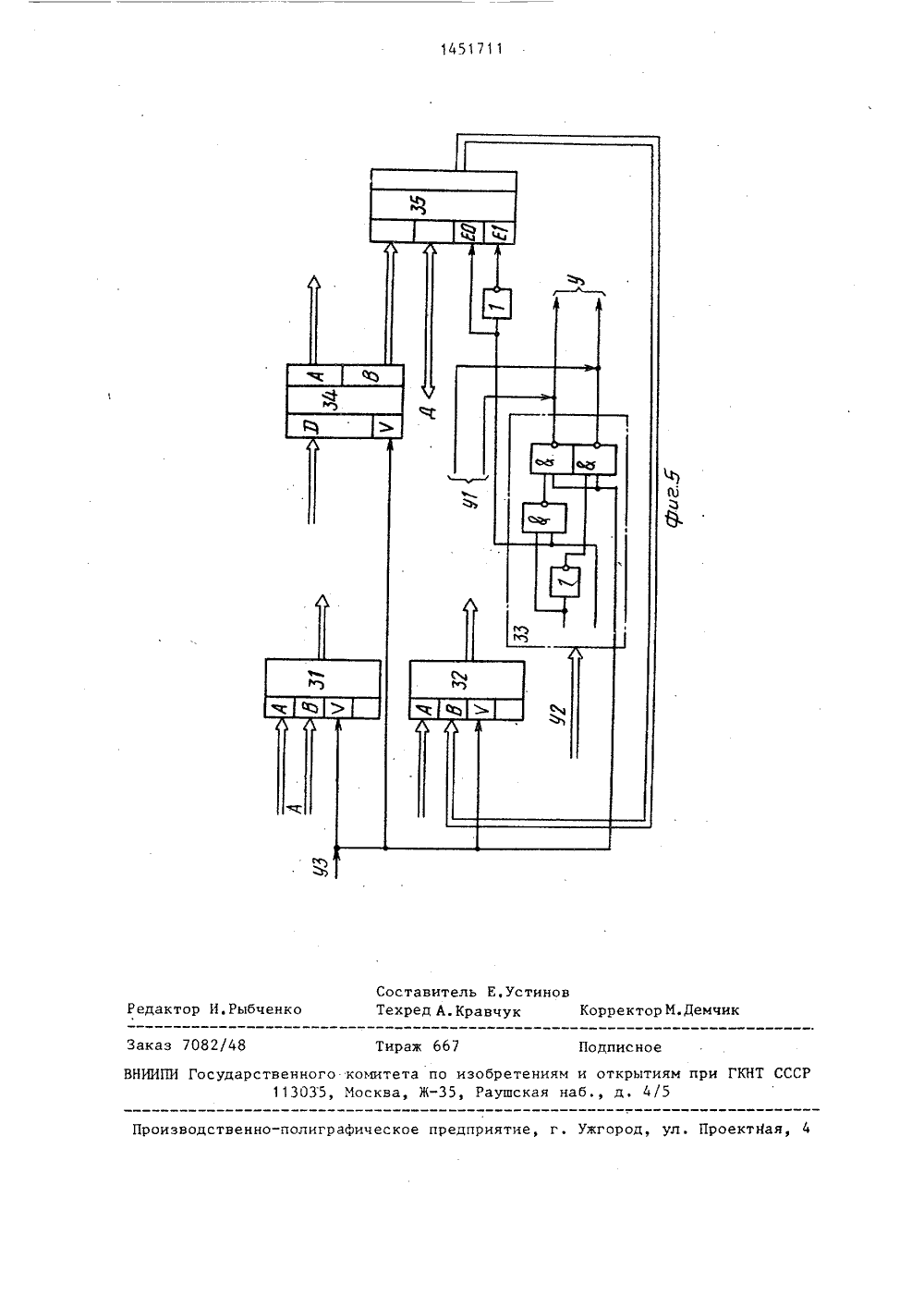

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХ СПУБЛИ и 4 С 06 Р 15/1 ОПИСАНИЕ ИЗОБРЕТЕНИ осится к вычисчастности кконтролю, упраформации. Цель Аддо-д ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(57) Изобретение отнлительной технике, вавтоматизированномулению и обработке ин изобретения является увеличениепроизводительности системы за счетвозможности непрерывной и независимой работы двух процессоров. Управляющая вычислительная система содержитмикро-ЭВМ 1, содержащую процессор 2с устройством 3 ввода/вывода, оперативным запоминающим устройством 4 ивнешними устройствами 5, блок 6 управления, мультиплексор 7, основноеоперативное запоминающее устройство8, блок 9 управления доступом, второйпроцессор 10, постоянное запоминающее устройство 11, оперативное эапоминающее устройство 12 второго процессора, 5 ил.1451711предназначен для обработки и обмена информацией с внешними устройствами 5, обмена информацией с ОЗУ 8 и контроля режимов работы и управления второго процессора 10.Процессор 10 предназначен дляавтоматизированного управления технологическим процессом внешних устройств 13, контроля их режимов, обмена и обработки информации. Собственные ПЗУ 11 и ОЗУ 12 процессора 10 предназначены соответственно для хранения и записи программ управления этим процессором,Блок 6 управления предназначендля обмена информацией между процессором 2 и ОЗУ 8. Блок 9 управления доступом предназначен для управления доступом к ОЗУ 8 процессора 2 или 10 в соответствии с программой работы процессора 2. Мультиплексор 7 предназначен для коммутации и согласования цифровых адресных, информационных и управляющих сигналов процессора 2 или 10, коммутируемых с помощью блока 9 управления доступом на входные адресные, информационные и управляющие шины ОЗУ 8, и коммутации выходной шины информации ОЗУ 8 на соответствующие входы приемопередатчиков 20 блока 6 управления или на шину информации Д процессора 10. ОЗУ 8 предназначено для хранения информации и обмена информацией с процессорами 2 и 10.Система работает следующим образом.Внешние устройства 5 содержат внешнее запоминающее устройство на НГМД-дисках, выходное печатающее уст 55 ройство и т,д. Процессор 2 вместе с устройством 3 ввода/вывода, собственным ОЗУ 4 и внешними устройствами 5 Процессор 2 имеет собственное ОЗУ 4 емкостью не менее 4 К 16-разрядных слов и вместе с устройством 3 ввода/вывода (типа дисплея) и внешними устройствами 5, подключенными через собственно шины управления (интерфейсы), представляет собой микро- ЭВМ типа "Электроника", "Электроника" МС 1213, "Электроника "НД- -80-01 Д и т.п серийно выпускаемые или выполненные на отдельных БИС.Канал обмена информацией этой микро- ЭВМ имеет две шины: шину, адрес - данные АДОО - АД 15 и шину управления У 1, к которым подключен блок 6 управления, выходы которого через мультиплексор 7 подключены к адресным А 1, информационным Д 1 и управляющим У входам ОЗУ 8, Выходы информации ОЗУ 8 Д 01 (см, фиг,3) через мультиплексор 7 подключены к входам Д 02 блока40 314517 6 управления. При включении питания системы процессоры 2 и 1 О вырабатывают на шинах управления У 1 и У 2 сигналы "Сброс 1" и "Сброс 2", которые ус-танавливают триггеры всех устройств, подключенных к шинам У 1 и У 2, в нулевое состояние, Эта обеспечивает подключение сигналов АрО, АДО и У 1 блока управления 6 (см, фиг,2) с помощью 10 мультиплексора 7 на входные адресные А 1, информационные Д 1 и управляющие У шины ОЗУ 8, ОЗУ 8 является энергонезависимым (т.е. не теряющим инфор-. мации при исчезновении питания), об ладает емкостью по меньшей мере 4 К байтов, Мультиплексор 7 коммутирует выходы информационной шины Д 01 ОЗУ 8 на входы Д 02 блока 6 управления, при этом на входе управления коммутацией 20 УЗ мультиплексора 7 (см, фиг,5) имеется сигнал низкого уровня. Если сигнал на входе УЗ высокого уровня(2, 4 В), схема коммутации коммутирует сигналы шин А, Д и У 2 второго про цессора 10 соответственно на входные адресную А 1, информационную Д 1 и управляющую У шины ОЗУ 8 при записи в него информации. При считывании инФормации выходная шина Д 01 РЗУ 8 под- З 0 ключается к шине Д второго процессора 1,0. Процессоры 2 и 10 сами по себе программно и аппаратно между собой не совместимы. Однако введение мультиплексора 7 между блоком 6 управле- ЗБ ния и ОЗУ 8 обеспечивает их аппаратное совмещение и позволяет управлять процессором 10 с помощью программы управления процессора 2. Управление выбором коммутации мультиплексора 7 осуществляется с помощью блока 9 управления доступом, в выходной регистр которого процессор 2 записывает высокий или низкий логический уровень. Если записан низ. кий уровень, ОЗУ 8 подключается мультиплексором 7 через блок 6 управления к шинам АДОО-АД 15 и У 1 процессора 2, который производит запись или считывание информации ОЗУ 8. Если с помощью устройства 3 ввода/вывода или программно записан в регистр блока 9 управления доступом высокий уровень, то ОЗУ 8 подключается мультиплексором 7 к шинам А, Д и У 2 процессора 10, который производит запись или считывание информации (или программы) ОЗУ 8. Таким образом, с помощью устройства 3 11ввода/вывода процессора 2 можно вводить программу управления вторым процессором 10, котарьп может перенести эту программу в собственно ОЗУ 12, производить автоматизированное управление внешними устройствами 13 и контролировать состояние этих внешних устройств. Кроме тагс, процессор 10 может производить обмен информацией внешних устройств 13 и ОЗУ 8. По окончании записи информации процессором 10 в ОЗУ 8 ан записывает в один из разрядов регистра блока 9 управления доступом высокий уровень. Этот разряд регистра по программе или с помощью устройства 3 ввода/вывода считывается процессором 2, и, если необходимо, процессор 2 с помощью блока 9 управления доступом переключает ОЗУ 8 к своей магистрали АДОО-АЦ 15 для ввода новой программы или данных, Блок 9 управления доступом производит отключение одного или нескольких ПЗУ 11 или ОЗУ 12 и под.ключает арно из этих ОЗУ или ПЗУ, а также запускает программу управления процессорам 10 или изменяет ее. Блок 6 управления управляет записью или счить;ванием информации с ОЗУ 8, т.к. процессор 2 работает по асинхронному принципу и не имеет отдельной шины адреса, а эта шина адреса совмещена с его магистралью данных. После включения питания мультиплексор 7 (как изложено вьппе) коммутирует выходные сигналы АрО, ДО, У 1 блока управления 6 к входным шинам А 1 адреса, Д 1 информации и У управления ОЗУ 8 и коммутирует выхорную шину Д 01 ОЗУ 8 на входы ДО 2 блока 6 управления. При обращении процессора 2 к ОЗУ 8 для записи информации вначале на шине АДООАД 15 генерируется параллельный двоичный 16-разрядный цифровой код адресаячейки ОЗУ 8. Этот код сопровождается по магистрали У 1 сигналом синхронизации СИА и поступает на входы приемопередатчиков блока 6 управления (смфиг.2), а сигнал СИА - на вход приемников 14. С выхода приемопередатчиков 20 код адреса поступает навход схемы 15 выбора банка, и на адресный регистр 16, Если три разрядакода адреса АЦ 13-АД 15, подаваемыена схему 15 выбора банка, совпадают сустановленным кодом в этой схеме, наее выходе появляется сигнал УВО10 15 20 25 ЗО 35 40 45 Блок 9 управления доступом аналогичен блоку 6 управления с той лишь разницей, что он имеет логику прерывания, позволяющую процессору 10(устройство выбрано), который поступает на вход регистра 17 адреса. С помощью сигнала СИА, поступающего на вход регистра 17 адреса, сигнал УВО записывается в регистр 17 адреса, а в адресный регистр 16 записывается адрес ячейки памяти ОЗУ 8.Во второй части цикла обращения процессора 2 к ОЗУ процессор 2 на шине АДОО-АД 15 вырабатывает параллельный двоичный 16-разрядный цифровой код данных, который сопровождается по магистрали упра.вления У 1 сигналом Вывод", Этот код информации с помощью приемопередатчиков 20 через мультиплексор 7 поступает на входную шину Д 1 информации ОЗУ 8, На адресную шину А 1 ОЗУ 8 подаются ана" логично сигналы АрО с выхода адресного регистра 16 через мультиплексор 7. На входы У управления ОЗУ 8 с выхода формирователя 18 управляющих сигналов блока 6 управления поступает сигнал ЗП/ЧТ и сигнал СЕ. Сигнал ЗП/ЧТ является инвертированным сигналом "Вывод", а сигналы СЕ являются сигналом УВ, который управляет входом выбора кристалла ОЗУ 8, Одновременно сигнал "Вывод" поступает на вход передатчика 19 для передачи сигнала синхронизации СИП в процессор 2 для регистрации того, что ответила схема управления ОЗУ 8. Длительность цикла записи или чтения ОЗУ 8 с помощью процессора 2 равна 2,5 мкс. Считывание информации с.ОЗУ 8 происходит аналогично, при этом приемо" передатчики 20 коммутируют входы ДО 1 на магистраль АДОО-АД 15 процессора 2, р на его шине У 1 генерируются сигнал СИА для записи адреса ячейки в адресный регистр 16, сигнал "Ввод" для коммутации приемопередатчиков 20 и сигнал СИП, сигнализирующий об окончании операции ввода. Если процессор 2 генерирует код адреса, который не совпадает с установленным на схеме выбора банка кодом, на ее выходе сигнал УВ = О, в результате на выходе формирователя 18 управляющихсигналов все сигналы управления отсутствуют, Схема выбора банка является дешифратором адреса. обращаться к процессору 2, требуя прерывания последнего в аварийной ситуации. Кроме того, вместо адресного регистра блок 9 управления доступом имеет два выходных регистра, по 1-4 разряда каждый. В один из этих регистров записываются данные от процессора 2 для переключения мультиплексора 7 и для сброса процессора.10. Во второй регистр процессор 10 записывает данные, сигнализируя о том, что запись данных в ОЗУ 8 закончена и процессор 2 может к нему обращаться. Селектор 30 адреса содержитдешифратор адреса и регистр адреса,полностью аналогичные устройствам24 и 25. Через схему селектора поступает сигнал ЗП от процессора 10.Эти сигналы поступают на входы регистра 29 блока 9 управления доступом при условии, что процессор 10 выработал адрес 1 ОООН(букваН означает, что адрес задан в шестнадцатиричной системе, а индекс 8 -в восьмеричной).Регистр 29 доступен для процессора 10 только для записи, а для процессора 2 - для считывания, Принципобмена информацией процессора 10 синхронный. Процессор 10 может иметь8-разрядную шину данных ДОО-Д 07 или16-разрядную (более совершенный вариант с более высокой производительнос"тью). При этом ОЗУ 8 можно выполнитьна 4 К 16-разрядных слоев, т.е, полностью совмещенным с процессором 2.Так как процессор 10 имеет отдельныешины адреса А и данных Д, то для егообращения к ОЗУ 8 сложной схемы управления не требуется. Приемопередатчики 20 блока 6 управления аналогичны шинным формирователям мультиплексора 7 с той лишь разницей, чтоприемопередатчики выполнены с двумясостояниями, а шинные формирователи -с тремя состояниями,Введение цифровой схемы коммутацин для управления ОЗУ 8 позволяет"применять в предлагаемой системе двапроцессора с различными системами команд, причем общее количество командсистемы 81+78 = 159. Это увеличивает производительность системы в два раза по сравнению с прототипом, где применены два процессора с одинаковой системой команд. При этом быстродей" ствие команды пересылки процессора 107 1451/ иэ регистра в ОЗУ 8 и наоборот 2,5- 3,5 мкс, а процессора - 2-8 мкс, т.е., производительность по быстродействию управления технологическим процессом также выше по меньшей мере в два раза. Поскольку программой предусмотрена независимая друг от друга асинхронная работа обоих процессоров, а обращение к ОЗУ 8 первого процессора 10 2 осуществл"ется с разрешения второго процессора 10, т.е. по.завершении процессором 10 пересылки информации в ОЗУ, и только в аварийных ситуациях второй процессор 10 15 может обратиться к процессору 2 по прерыванию, то ни один из процессоров не находится в режиме ожидания, что значительно увеличивает производительность системы, 20Формула изобретенияУправляющая вычислительная система, содержащая два процессора, оперативное запоминающее устройство первого процессора, оперативное запоминающее устройство второго процессора, постоянное запоминающее устройство, 30 блок управления доступом, основное оперативное запоминающее устройство, причем первый информационный вход- выход блока управления доступом соединен с информационными входами-выходами первого процессора, оперативного за" поминающего устройства первого процессора и блока управления, первый управляющий вход-выход блока управления доступом соединен с управляю щими входами-выходами первого процессора, оперативного запоминающего устройства первого процессора и блока управления, адресный вход-выход блока управления доступом соединен с 45 первым управляющим входом-выходом второго процессора и с адресными входами-выходами постоянного запоминающего устройства и оперативного эапоминающего устройства второгопроцессора, второй информационныйвход-выход блока управления доступомсоединен с информационными входамивыходами второго процессора, постоянного запоминающего устройства иоперативного запоминающего устройства второго процессора, второй управляющий вход-выход блока управлениядоступом соединен с вторым управляющим входом-выходом второго процессора и с управляющими входами-выходами постоянного запоминающего устройства и оперативного запоминающегоустройства второго процессора, информационный выход блока управлениядоступом соединен с информационнымивходами постоянного запоминающегоустройства и оперативного запоминающего устройства второго процессора,отличающаяся тем, что,с целью увеличения производительности за счет возможности непрерывнойи независимой работы двух процессоров, в нее введен мультиплексор, при",чем информационный, адресный и управляющий выходы блока управлениясоединены с первым, вторым и третьиминформационными входами мультиплексора соответственно, адресный, второй информационный и второй управляющий вход-выход блока управления доступом соединены с четвертым, пятыми шестым информационными входами-выходами мультиплексора соответственно,управляющий выход блока управлениядоступом соединен с входом управлениямультиплексора, первый, второй итретий информационные выходы мультиплексора соединены с адресным, информационным и управляющим входамиосновного оперативного запоминающегоустройства соответственно, информационный выход которого соединен сседьмым информационным входом мультиплексора, четвертый информационныйвыход которого соединен с информационным входом блока управления.тета по и ва, Ж,бретенням аушская н открытиям при ГКНТ ССС д, 4/5

СмотретьЗаявка

4117588, 10.09.1986

ПРЕДПРИЯТИЕ ПЯ А-1298

МЕДВЕДЕВ ВИКТОР ПАВЛОВИЧ, ВЕБЕР СЕРГЕЙ ВАЛЕНТИНОВИЧ, АРТЕМЬЕВ ВАЛЕРИЙ ВАСИЛЬЕВИЧ, ВОЛКОВА АЛЕВТИНА АЛЕКСАНДРОВНА

МПК / Метки

МПК: G06F 15/16

Метки: вычислительная, управляющая

Опубликовано: 15.01.1989

Код ссылки

<a href="https://patents.su/7-1451711-upravlyayushhaya-vychislitelnaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Управляющая вычислительная система</a>

Предыдущий патент: Устройство обработки информации

Следующий патент: Адаптивная система обработки данных

Случайный патент: Устройство для ограждения движителя подводного аппарата