Многотактное микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

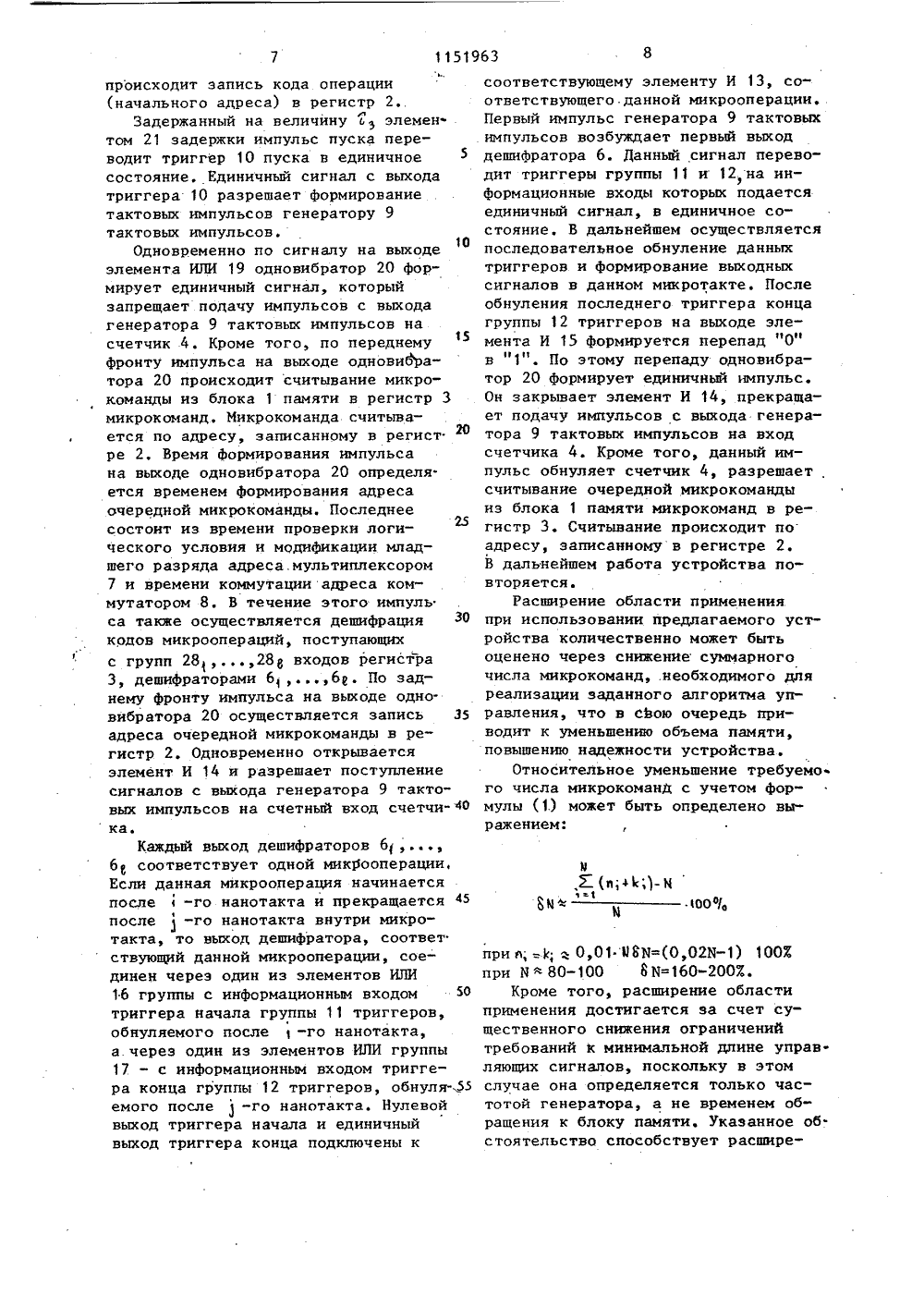

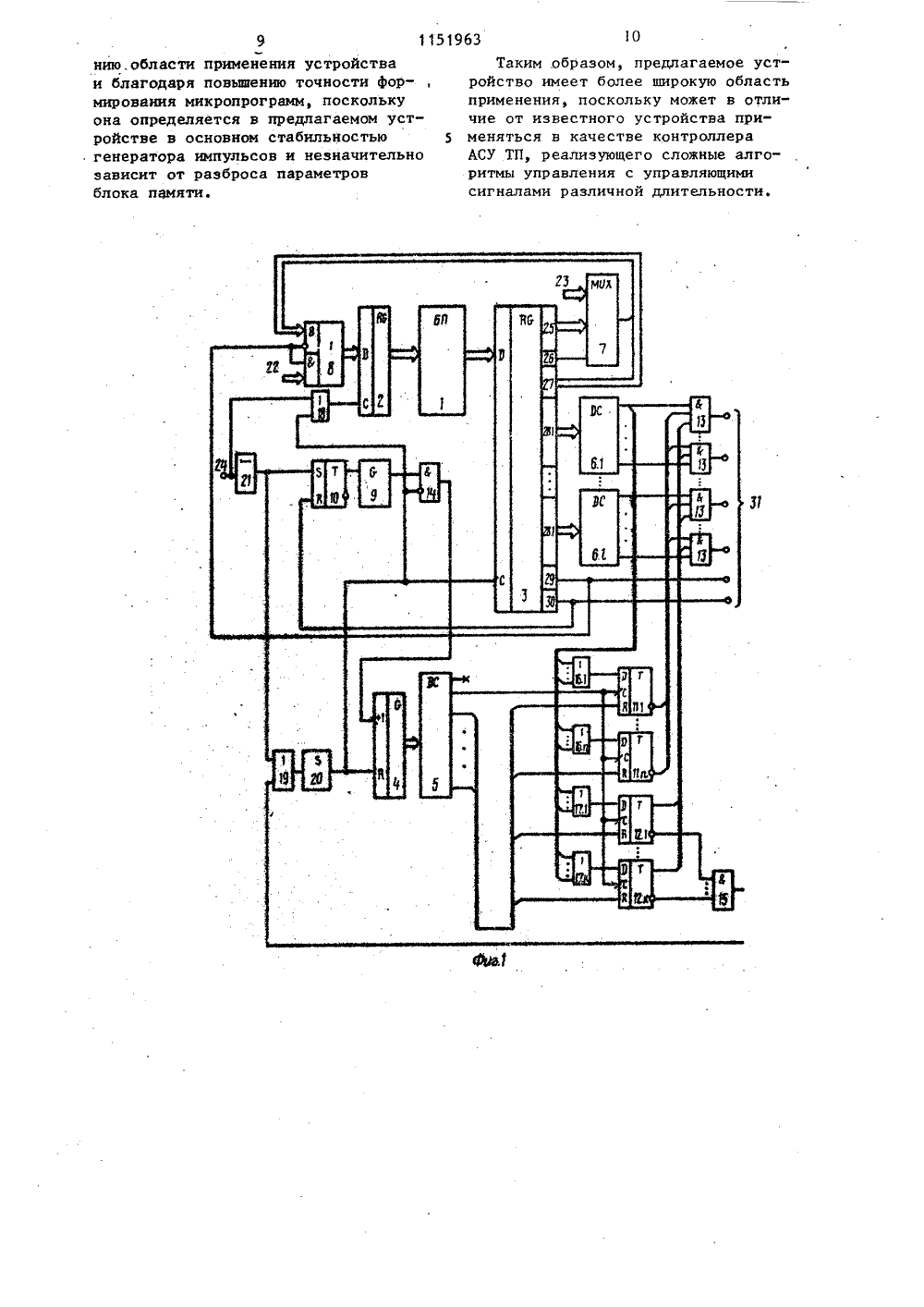

) С 06 Г 9/ К Харченко,ькин,тьев ельство СССР2, 1978.ьство СССР2, 1981.ьство СССР2, 1982 ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ САНИЕ ИЗОБРЕ РСИОМУ СВИДЕТЕЛЬСТВУ(54) (57) МНОГОТАКТНОЕ МИКРОПРОГРИФМНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд,счетчик, генератор тактовых импульсов, первую группу триггеров, группу дешифраторов, первую группу элементов ИЛИ, дешифратор, первыйэлемент И и элемент задержки, причем выход регистра адреса соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, группы выходовкодов микроопераций которого соединены с соответствующими группамивходов дешифраторов группы, выходыкоторых соединены с соответствующими входами п 1 элементов ИЛИ первойгруппы, выходы которых соединеныс информационными входами триггеровпервой группы, нулевые выходы которых соединены с входами первогоэлемента И, выход счетчика соединенс входом дешифратора, Ф выходов которого (п 1 =1,2 где п " количество многотактных микроопераций)соединены с входами установки в"0" соответствующих в триггеровпервой группы, о т л и ч а ю щ е -е с я тем, что, с целью расширенияобласти применения за счет реализации алгоритмов с произвольнымиточками начала и конца микроопераций, оно дополнительно содержитвторую группу триггеров, группу элементов И, вторую группу элементовИЛИ, коммутатор, мультиплексор,триггер пуска, второй элемент И,первый и второй элементы ИЛИ и одновибратор, причем вход пуска устройства соединен с первым входомпервого элемента ИЛИ и с входом элемента задержки, выход которого соединен с первым входом второго элементаИЛИ и с входом установки в "1" триггера пуска, выход которого соединенс входом запуска генератора тактовыхимпульсов, выход которого соединенс прямым входом второго элемента И,инверсный вход которого соединен свыходом одновибратора, с входом установки в "0" счетчика, с входомсинхронизации регистра микрокоманди с вторым входом первого элементаИЛИ, выход которого соединен с входом синхронизации регистра адреса,информационный вход которого соединен с выходом коммутатора, перваягруппа информационных входов которого является группой входов кодакоманды устройства, (л) информационных входов второй группы коммутатора (П=1,2 где 11 - разрядностьадреса блока памяти микрокоманд) соединены с (й) выходами немодифи 115 цируемых разрядов адреса регистра микрокоманд, выход модифицируемого разряда адреса которого соединен с первым информационньж входом группы мультиплексора, остальные информационные входы группы которого являются входами логических. условий группы устройства, выход кода анализируемых логических условий регистра микрокоманд соединен с управляющим входом мультиплексора, выход которого соединен с я -и информационным входом второй группы коммутатора, управляющий вход которого соединен с выходом признака конца команды регистра микрокоманд и является выходом индикации конца команды устройства, выход признака конца работы регистра микрокоманд соединен с входом установки в "О" триггера пуска и является выходом индикации конца работы устройства, в выходов де 1963шифратора соединены с входами уста новки в "О" соответствующих щ триггеров второй группы, нулевые выходыгкоторых соединены с первыми входами соответствующих щ элементов И группы, вторые входы которых соединены с единичными выходами соответствую.щих Ф триггеров первой группы, входы синхронизации которых соединеныс входами синхронизации щ триггероввторой группы и с (щ+1)-м выходомдешифратора, выход первого элементаИ.соединен с вторым входом второгоэлемента ИЛИ, выход которого соединен с входом одновибратора, выход второго элемента И соединен со счет.ным входом счетчика, выходы группыдешифраторов соединены с третьими входами соответствующих элементов И группы, выходы которых являютсяуправляющими выходами группы устройства.1 О 20 с нулевым входом счетчика, выход ре. гистра адреса соединен с входом бло. Изобретение относится к вычисли-тельной технике и ыожег быть использовано при построенни микропрограммируемьи контроллеров для АСУтехнологическими процессами.Известны миоготактиые микропрограммные устройства управления, содержащие блок памяти, регистр адреса, регистр микрокоманд, дешифраторы, логические элементы И, И 3%11 иЯ.В этих устройствах реализуетсяпринцип нанопрограммнрования, представляющего собой уровень микропрограммного управления, допускающий задание временной последовательности управляющих сигналов наноопераций).Недостатками укаэанных устройствявляются низкая экономичность, обус"ловленная раэнотипнцм форматом однотактных м многотактных микрокоманд,и узкая область применения, вызванная ограниченной номенклатурой процедур нанопрограммирования,Наиболее близким к предлагаемому 2является многотактное микропрограммное устройство управления, содержа.щее блок памяти, регистры адресаи мнкрокоманд, счетчик, генератор импульсов, группу триггеров, группу дешифраторов, дешифратор, групну элементов ИЛИ, элемент И, злемент задержки, причем выход генератора импульсов является тактовым вьг ходом устройства и соединен со счетным входом счетчика, выходы которогосоединены с входами дешифратора,выходы которого соединены с нулевымн входами группы триггеров, выходыгруппы дешифраторов являются информационными выходами устройства и соединены с соответствующими входами группы элементов ИЛИ, выходы которых соединены с единичньпчи входами группы триггеров, выходы которых соединены с входами элемента И, выход которого соединен с входом регистраадреса, а через элемент задержки -ка памяти, выход которого соединенс входом регистра микрокоманд, выходы которого соединены с входамигруппы дешифраторов Г 37,Недостатком известного устройстваявляется узкая область применения,обусловленная тем, что в указанномустройстве невозможно в пределах од,ай (2) 45св И ного микротакта реализовать набормикро (нано) операций, имеющих различные моменты начала и конца Формирования управляющих сигналов. Вданном устройстве микротакт, а соответственно и микрокоманда, заканчиваются одновременно с окончанием самойдлинной микрооперации, Это обстоятельство существенно сужает областьприменения устройства в качествеконтроллера АСУТП, в которых требует.ся реализовать сложные многотактныеалгоритмы управления, что обусловлено следующими причинами: при реализации алгоритмов, содержащих управляющие сигналы различной длительносЖ,длина микротакта должна выбиратьсяисходя из длительности самого короткого сигнала, действующего в его пределах. Это приводит к значительному 20увеличению числа микрокоманд, хранимых в блоке памяти, а в конечном итоге - к снижению надежности устройства, Количественное увеличение числамикрокоманд оценивается выражением 25 где и; и ; - число разлйчных начал З 0и концов управляющихсигналов в микрокоманде М;,11 - число микрокоманд.Снижение надежности устройствапроисходит в этом случае также ивследствие увеличения вероятностисбоя в связи с ростом частоты обращения к блоку памяти,онУвеличение интенсивности сбоев Зь 40пропорционально росту числа микрокоманд ( а следовательно, и обраще-"ний к блоку памяти): При выполнении алгоритмов, содержащих управляющие сигналы, длительность которых приближается к времени считывания информации из блока памя ти, использование известного устройства становится невозможным в силу реальных технических ограничений по быстродействию.Таким образом, вследствие рас смотренных причин известное устройство имеет ограниченную область при" менения в АСУТП, в которых реализуются алгоритмы управления рассмотренного класса.Цель изобретения - расширение области применения за счет реализации алгоритмов с произвольными точками начала и конца микроопераций.Поставленная цель достигается тем, что в многотактное микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд,счетчик, генератор тактовых импульсов, первую группу триггеров, группу дешифраторов, первую группу элементов ИЛИ, дешифратор, первый элемент И и элемент задержки, причемвыход регистра. адреса соединен садресным входом блока памяти микрокоманд, выход которого соединен синформационньм входом регистра микрокоманд, группы выходов кодов микроопераций которого соединены ссоответствующими группами входов дешифраторов группы, выходы которыхсоединены с соответствующими входамив элементов ИЛИ первой группы, выхолы которых соединены с информационными входами триггеров первойгруппы, нулевые выходы которых соединены с входами первого элемента И,выход счетчика соединен с входомдешифратора, в выходов которогоОч=1,2 где е - количество многотактных микроопераций) соединеныс входами установки в "О" соответствующих щ триггеров первой группывведены вторая группа триггеров,группа элементов И, вторая группаэлементов ИЛИ, коммутатор, мультиплексор, триггер пуска, второй элемент И, первый и второй элементыИЛИ и одновибратор, причем вход пуска устройства соединен с первымвходом первого элемента ИПИ и с входом элемента задержки, выход которого соединен с первьм входом второго элемента ИПИ и с входом установки в "1" триггера пуска, выход которого соединен с входом запуска генератора тактовых импульсов, выход которого соединен с прямым входом второго элемента И, инверсный вход которого соединен с выходом одновибратора, с входом установки в "О" счетчика, с входом синхронизации регистра микрокоманд и с вторым входом первого элемента ИЛИ, выход которого соединен с входом синхрони1151963 новибратора и обусловленных ими свя. зей позволяет управлять записью информации в регистры адреса и микро- команд и счетчиком.Введение триггера пуска и новых связей элемента задержки дает возмощность управлять пуском генератора импульсов и формировать сигнал первоначального занесения информации в регистры адреса и микрокоманд,На фиг,1 приведена функциональная схема предлагаемого устройства; на фиг,2 - временные диаграммы работы устройства.Функциональная схема многотактного микропрограммного устройства управления фиг.1) содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микрокоманд, счетчик 4, дешифратор 5, группу дешифраторов ббе, мультиплексор 7, коммутатор 8, генератор 9 тактовых импульсов, триггер 10 пуска, вторую группу триггеров 1111 (начала микроопераций), первую группу триггеров 12 112 конца микроопераций), группу 13 элементов И, второй элемент И 14, первый элемент И 15,"вторую 1616 в и первую 17 17 группы элементов ИЛИ, первый элемент ИЛИ 18, второй элемент ИЛИ 19, одновибратор 20, эле. мент 21 задержки, группу 22 входов кода команды, группу 23 входов логических условий, вход 24 пуска, группу 25 кода анализируемых логическихусловий регистра микрокоманд, выход 26 моднфицируемого разряда адреса регистра микрокомаид, группу 27 выходов иемодифицируемых .разрядов адреса регистра микрокоманд, группы 28 1- 28 р выходов кодов микроопераций регистра микрокоманд, выход 29 признака конца команды регистра микрокоманд, вьиод 30 признака конца работы регистра микрокоманд и группу 31 управляющих выходов.Предлагаемое устройство работает следующим образом.1 да"Пуск" на вход 24, которая представляет собой единичный импульс.По заднему Фронту этого импульса зации регистра адреса, информационный вход которого соединен с вьиодом коммутатора, первая группа информационных входов которого является группой входов кода команды уст.ройства, М 1) информационных входоввторой группы коммутатора ( П =1,2,где и - разрядность адреса блокапамяти микрокоманд) соединены с(и) вьиодамн немодифицируемых раз"рядов адреса регистра ьыкрокоманд,выход модифицируемого разряда адреса которого соединен с первым информапионньм входом группы мультинлексора, остальные информационные входыгруппы которого являются входамилогических условий группы устройства,выход кода анализируемых логическихусловий регистра микрокоманд соединен с управляющим входом мультиплек.сора, выход которого соединен с О -минформационным входом второй группыкоммутатора, управляющий вход кото"рого соединен с вьиодом признакаконца команды регистра микрокоманди является выходом индикации концакоманды устройства, выход признакаконца работы регистра микрокомандс входом установки в "0" триггерапуска и является выходом индикации 30конца работы устройства, я 1 выходовдешифратора соединены с входами установки в "0" соответствующих ш триггеров второй группы, нулевые выходыкоторых соединены с первыми входами З 5соответствующих, е элементов И группы, вторые входы которых соединены сединичными выходами соответствующихЮ триггеров первой группы, входысинхронизации которых соедннены с 40входами синхронизации у триггероввторой группы и с (в+1)-м выходомдешифратора, вьиод первого элементаИ соединен с вторым входом второгоэлемента ИЛИ, выход которого соединен 45с входом одновибратора, выход второго элемента И соединен со счетновходом счетчика, выходы группы дешифраторов соединены с третьими входаиисоответствующих элементов И группы, ьовьиоды котврьи являются управляю- В исходном состоянии элементыщими вьиодами группы устройства, памяти находятся в "0", на выходеВведение коммутатора и мульти регистра 3 имеет место логичесплексора и обусловленных ими связей кая "1". После прихода кода адресапозволяет управлять передачейи мо- у на группу 22 входов подается командификацией адреса,Введение первого и второго элементов ИЛИ, второго элемента И и од 4происходит запись кода операции (начального адреса) в регистр 2Задержанный на величину ь элементом 21 задержки импульс пуска переводит триггер 10 пуска в единичное состояние, Единичный сигнал с выхода триггера 10 разрешает формирование тактовых импульсов генератору 9 тактовых импульсов.Одновременно по сигналу на выходе10 элемента ИЛИ 19 одновибратор 20 Формирует единичный сигнал, который запрещает подачу импульсов с выхода генератора 9 тактовых импульсов на счетчик 4. Кроме того, по переднему Фронту импульса на выходе однови(Ьатора 20 происходит считывание микро- команды из блока 1 памяти в регистр 3 микрокоманд., Иикрокоманда считывается по адресу, записанному в регист. ре 2, Время Формирования импульса на выходе одновибратора 20 определяется временем Формирования адреса очередной микрокоманды. Последнее состоит из времени проверки логического условия и модификации младшего разряда адреса. мультиплексором 7 и времени коммутации адреса коммутатором 8В течение этого импуль. са также осуществляется дешифрация ЗО кодов микроопераций, поступающих с групп 281288 входов регистра 3, дешифраторами 616 р. По заднему фронту импульса на выходе одновибратора 20 осуществляется запись 35 адреса очередной микрокоманды в регистр 2. Одновременно открывается элемент И 14 и разрешает поступление сигналов с выхода генератора 9 тактовых импульсов на счетный вход счетчика.Каждый выход дешифраторов 61 6 соответствует одной мик 11 ооперации, Если данная микрооперация начинается после-го нанотакта и прекращается после-го нанотакта внутри микро- такта, то выход дешифратора, соответ. ствующий данной микрооперации, соединен через один из элементов ИЛИ 16 группы с информационным входом 50 триггера начала группы 11 триггеров, обнуляемого после 1 -го нанотаКта, а.через один из элементов ИЛИ группы 17 - с информационным входом триггера конца группы 12 триггеров, обнуля емого после-го нанотакта. Нулевой выход триггера начала и единичный выход триггера конца подключены ксоответствующему элементу И 13, соответствующего. данной микрооперации. Первый импульс генератора 9 тактовых импульсов возбуждает первый выход дешифратора 6. Данный сигнал переводит триггеры группы 11 и 12 на информационные входы которых подается единичный сигнал, в единичное состояние. В дальнейшем осуществляется последовательное обнуление данных триггеров и формирование выходных сигналов в данном мнкротакте. После обнуления последнего триггера конца группы 12 триггеров на выходе элемента И 15 формируется перепад "0" в "1". По этому перепаду одновибратор 20 формирует единичный импульс. Он закрывает элемент И 14, прекращает подачу импульсов с выхода генератора 9 тактовых импульсов на вход счетчика 4. Кроме того, данный импульс обнуляет счетчик 4, разрешает, считывание очередной микрокоманды из блока 1 памяти микрокоманд в регистр 3. Считывание происходит по адресу, записанному в регистре 2. В дальнейшем работа устройства повторяется.Расширение области применения при использовании предлагаемого устройства количественно может быть оценено через снижение суммарного числа микрокоманд, необходимого для реализации заданного алгоритма управления, что в свою очередь приводит к уменьшению объема памяти, повышению надежности устройства.Относительное уменьшение требуемо го числа микрокоманд с учетом формулы (1) может быть определено выражением: Н,Е(е;1;)-К1=3М 1 ОО% при в;:1 с;0,01 ИЗБ=(0,02 И) 100 Ж при И "- 80-100 О И=160-2007.Кроме того, расширение области применения достигается за счет существенного снижения ограничений требований к минимальной длине управляющих сигналов, поскольку в этом случае она определяется только частотой генератора, а не временем обращения к блоку памяти. Указанное об. стоятельство способствует расшире1151963 о 9нию.области применения устройства и благодаря повышению точности формирования микропрограмм, поскольку она определяется в предлагаемом устройстве в основном стабильностью генератора импульсов и незначительно зависит от разброса параметров блока памяти. Таким .образом, предлагаемое устройство имеет более широкую область применения, поскольку может в отличие от известного устройства при меняться в качестве контроллераАСУ ТП, реализующего сложные алгоритмы управления с управляющими сигналами различной длительности,

СмотретьЗаявка

3686070, 28.12.1983

ПРЕДПРИЯТИЕ ПЯ М-5156

СИДОРЕНКО НИКОЛАЙ ФЕДОРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ОСТРОУМОВ БОРИС ВЛАДИМИРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, КИРСАНОВ СТАНИСЛАВ ПЕТРОВИЧ, ШЕРЕМЕТЬЕВ СЕРГЕЙ АЛЕКСАНДРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное, многотактное

Опубликовано: 23.04.1985

Код ссылки

<a href="https://patents.su/7-1151963-mnogotaktnoe-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Многотактное микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство переменного приоритета

Случайный патент: Цифровой функциональный преобразователь