Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

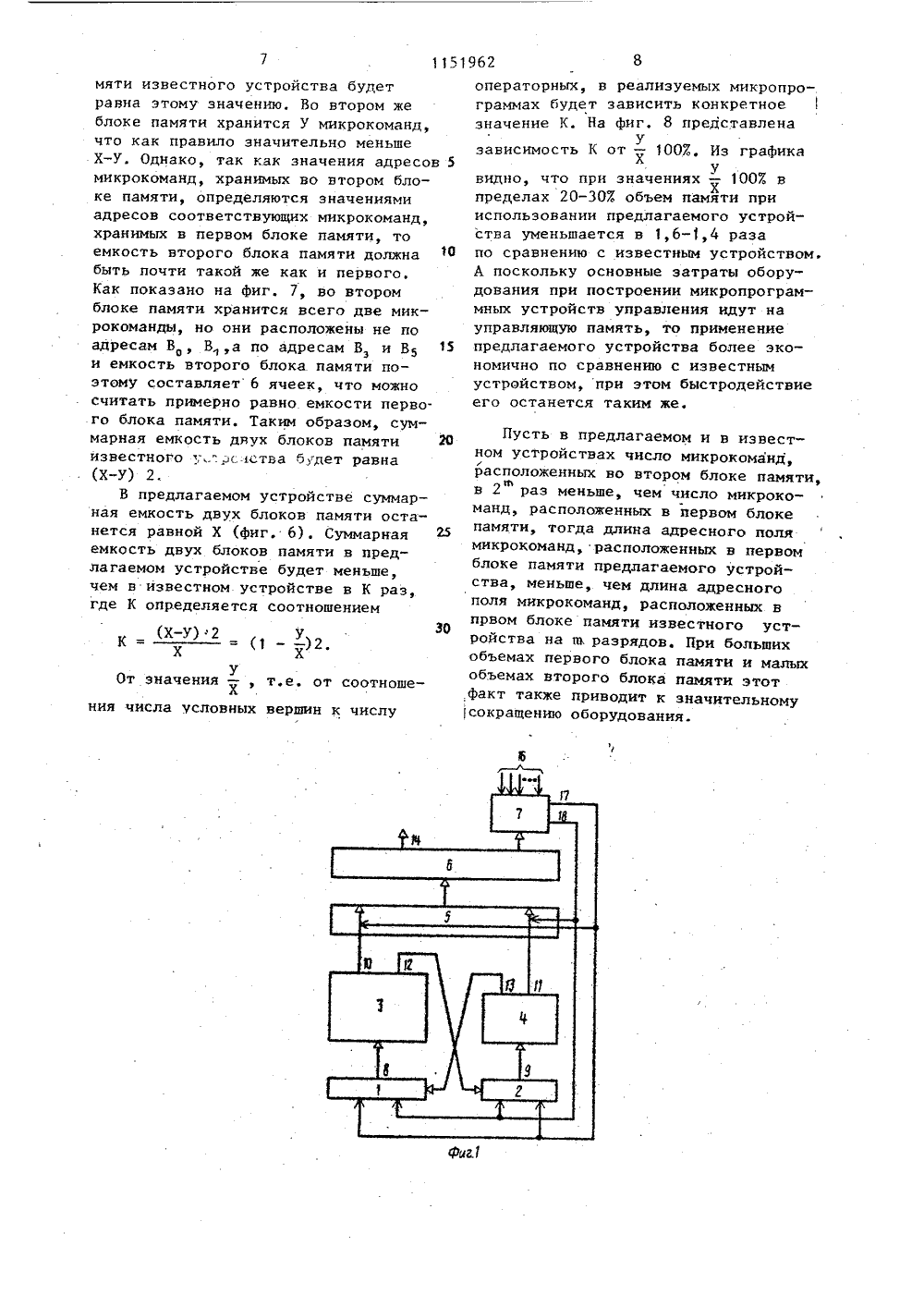

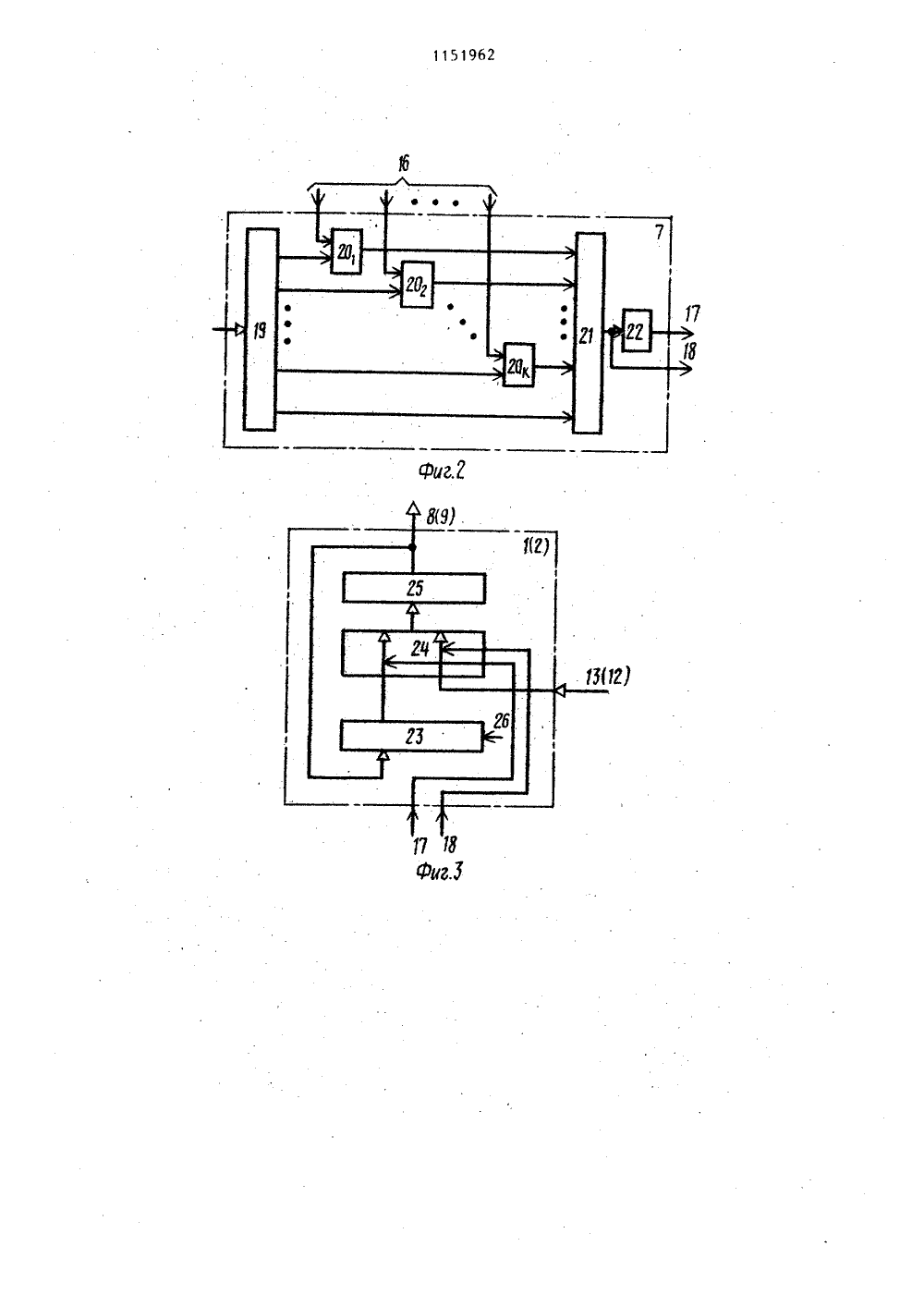

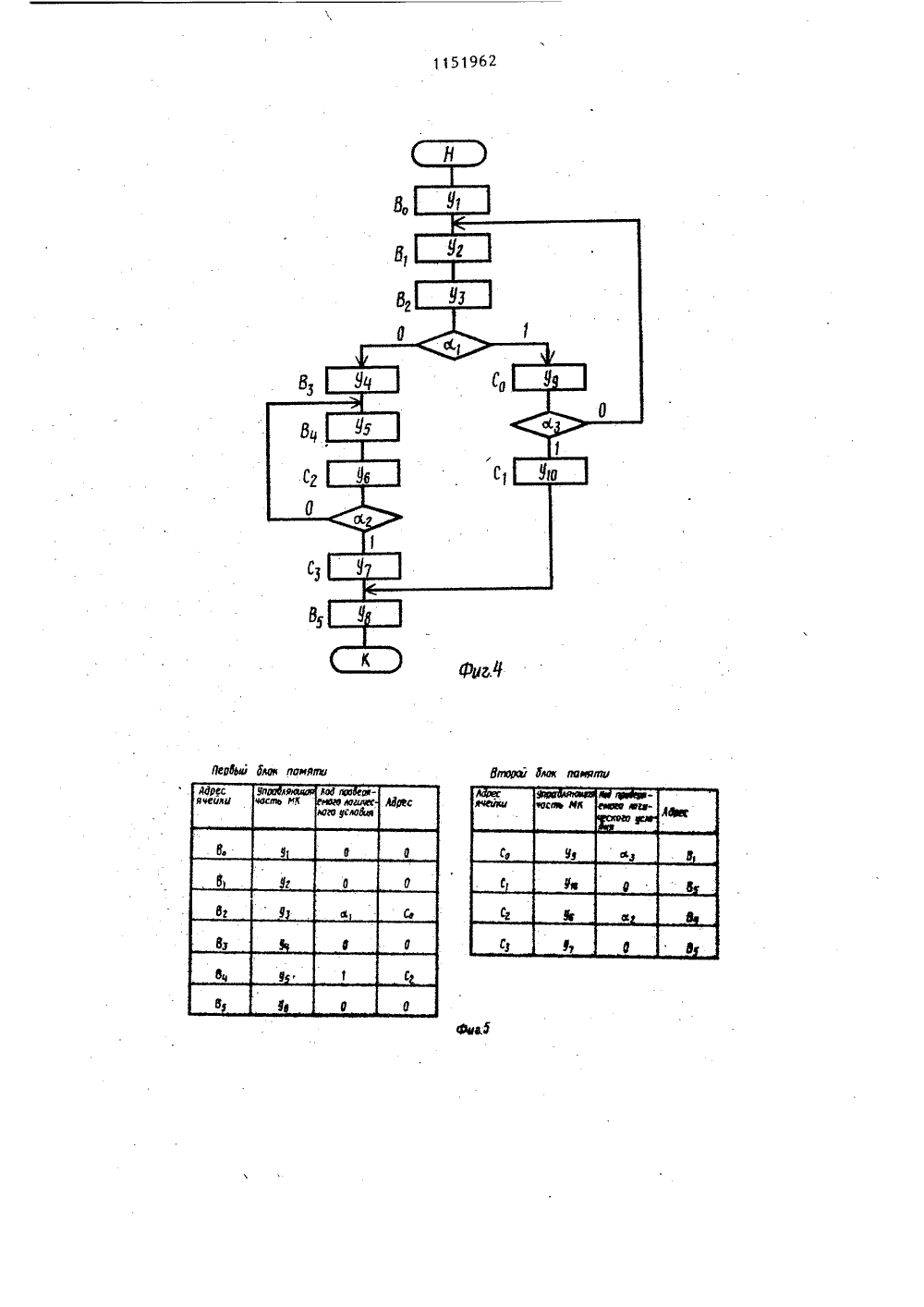

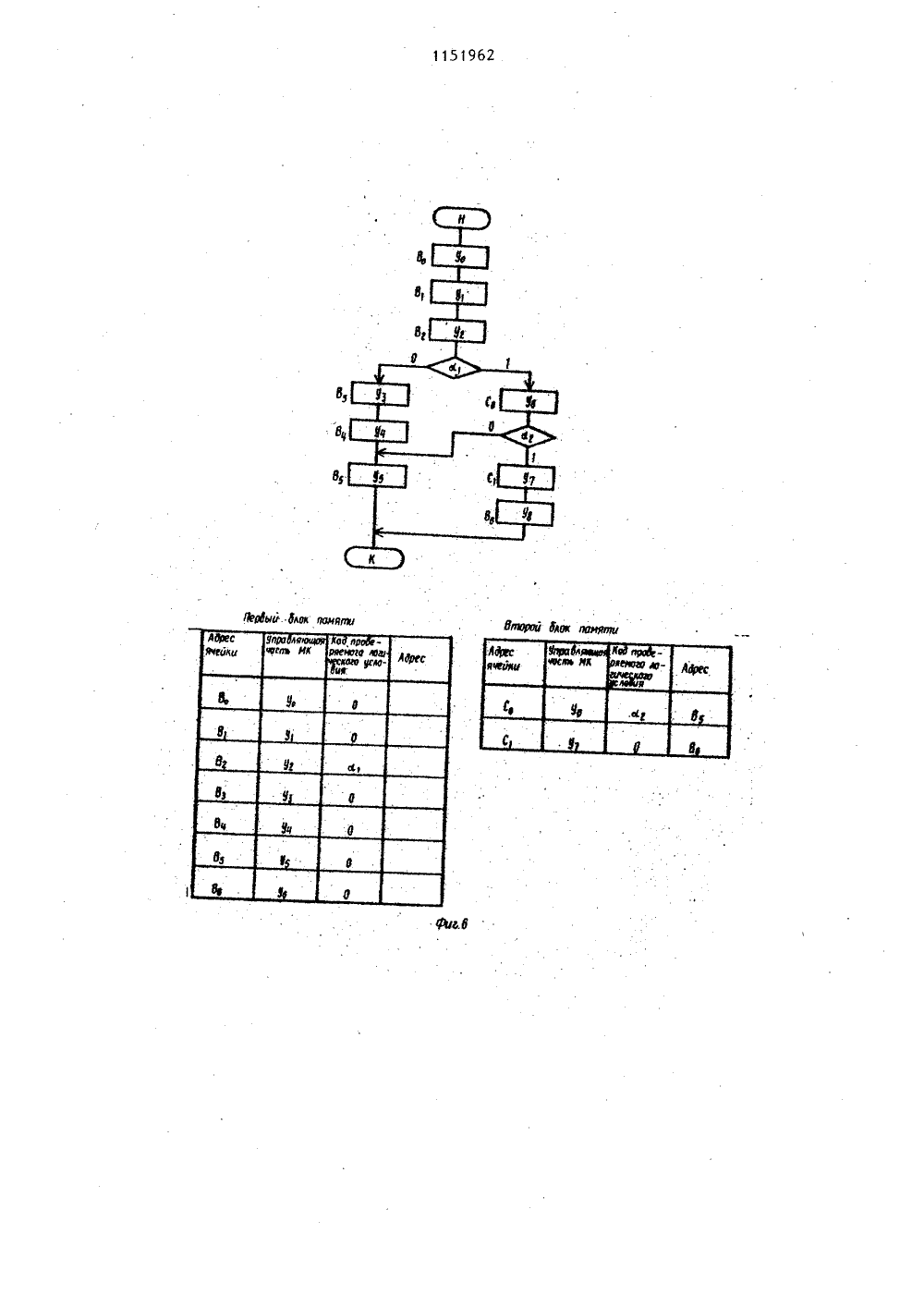

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИН 801151962 А 4(51) С 06 Р 9/22 сь ОПИСАНИЕ ИЗОБРЕ Н. АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и второй выхо вий соединены лока проверки у тветственно с и о ым ос ии инсти Г.И.ние" т в Н,Ивычисплэйш 14. лительая шкотво СС ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(54)(57) 1, МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее два блокапамяти, микрокоманд, коммутатор, регистр микрокоманд и блок проверки условий, причем выход кода микроопераций регистра микрокоманд являетсявыходом устройства, группа выходовкода логических условий регистра микрокоманд соединена с первой группойвходов блока проверки условий, вторая группа входов которого являетсягруппой входов логических условийустройства, информационный вход регисра микрокоманд соединен с выходомкоммутатора, первый и второй информационные входы которого соединены соответственно с выходами кодов операцийи логических условий первого и второго блоков памяти микрокоманд, первый и вторым управляющими входами коммутатора, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования, оно содержит первый и второй блоки формирования адреса, причем, первый и второй управляющие входы первого и второго блоков формирования адреса соединены соответственно с первым и вторым выходами блока проверки условий, выходы первого и второго блоков формирования адреса соединены соответ. ственно с адресными входами первого и второго блоков памяти микрокоманд, выходы кода адреса которых соединены Я соответственно с информационными входами первого и второго блоков формирования адреса.2. Устройство по п. 1, о т л и - С ч а ю щ е е с я тем, что каждый% из блоков формирования адреса содержит регистр, коммутатор и сумматор,Меам причем выход регистра соединен с инЭффайформационным входом сумматора и является выходом блока, информационный вход регистра соединен с выходомзавей коммутатора, первый и второй управ- ф ляющие входы которого являются соот- ф",1 ветственно первым и вторым управля- Я ющими входами блока, первый информационный вход коммутатора соединен с выходом сумматора, вход переноса которого подключен к шине единичного потенциала, второй информационный вход коммутатора является информа,ционным входом блока.1151962 35 Составитель Ю, Ланцор Техред С.йовжий актор Аг ака Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4 И Ц 2 2324/37 Тираж 710ВНИИПИ Государственного комитетапо делам изобретений и открытий 113035, Москва, Ж, Раушская наб Корректор М, МаксимишинецПодписное1151Изобретение относится к вычислительной технике и может бытьиспользовано при построении управляющихавтоматов.Известно микропрограммное устройство управления., содержащее блок памяти, регистр микрокоманд, состоящийиз поля микроопераций, поля логических условий и адресного поля, счетчикадреса микрокоманд и блок проверки 10условий, включающий дешифратор,группу элементов И и элемент ИЛИ 11.Недостатком этого устройства является низкое быстродействие, таккак длительность автоматного тока . 15складывается из времени счета всчетчике адреса микрокоманд, временивыборки микрокоманды из блока памятии времени ее выполнения в операционном автомате. 20Известно также микропрограммноеустройство управления, содержащееблок памяти, регистр микрокоманд,состоящий из поля микрокоманд, полялогических условий и двух адресных 25полей, коммутатор, группу элементовИ, элемент ИЛИ и элемент НЕ 1 2 ,Хотя в сравнении с предыдущимустройством данное устройствои имеет несколько более высокое быстро 0действие (в нем длительность автоматного такта уменьшена на время счетав счетчике адреса микрокоманды), однако оно также .обладает низким быстродействием, так как в .нем выборкаследующей микрокоманды не можетЭ 5быть осуществлена во время выполнения в операционном автомате предыдущей микрокоманды,Наиболее близким по техническойсущности к изобретению являетсямикропрограммное. устройство управления, содержащее два блока памяти,коммутатор, регистр и блок проверкиусловий, причем первый и второй ин 45формационные входы коммутатора соединены с выходами соответственно первого и второго блоков памяти, выходкоммутатора соединен с информационным входом регистра, первый выходкоторого является информационным вы 50ходом устройства, второй выход соединен с информационным входом блокапроверки, условий, третий выход является адресным входом блоков памяти,второй информационный вход блока про верки условий является группой входовусловий устройства, первый и второйвыходы блока проверки условий соеди 962иены соответственно с первым и вторым разрешакнцими входами коммутатора 33. Известное устройство обеспечивает значительно более высокое быстродействие по отношению к предыдущим так как в нем длительность автоматического такта существенно сокращена эа счет распараллеливания процессов выполнения текущей микрокоманды и выборки следующей. Однако недостатком его является большое количество используемого оборудования, поскольку суммарная емкость двух блоков памяти значительно превышает минимально необходимую емкость памяти, требуемую дляразмещения микропрограмм (минимально необходимая емкость памяти при использовании микропрограммных устройств управления равна числу операторных вершин в граф-схемах реализуемых ими микропрограмм).Цель изобретения - сокращение количества используемого оборудования.Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее два блока памяти микрокоманд, коммутатор, регистр микрокоманд и блок проверки условий, причем выход кода микро- операций регистра микрокоманд является выходом устройства, группа выходов кода логических условий регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, информационный вход регистра микрокоманд соединен с выходом коммутатора, первый и второй информационные входы которого соединены соответственно с выходами кодов операций и логических условий первого и второго блоков памяти микрокоманд, первый и второй выходы блокапроверки условий соединены соответственно с первым и вторым управляющими входами коммутатора, введены первый и второй блоки формирования адреса, причем первый и второй управляющие входы первого и второго блоков формирования адреса соединены соответственно с первым и вторым выходами блока проверки условий, выходы первого и второго блоков формирования адреса соединены соответственно с адресными входами первого и второго блоков памяти микрокоманд, выходы962 4ход 14 устройства, группу 15 выходов кода логических условий регистра микрокоманд, группу 16 входов логических условий, первый 17 и второй 18 выходы блока проверки условий.Блок проверки условий (фиг. 2) содержит дешифратор 19, группу элементов И 20 -20 ( К - число логичес 1 Кких условий), элемент ИЛИ 21 и элемент НЕ 22.Блок формирования адреса (фиг, 3) содержит сумматор 23, коммутатор 24, регистр 25 и вход 26 переноса сумматора, подключенный к шине единичного потенциала. 1151 Микропрограммное устройство управления (фиг1) содержит первый 1 и второй 2 блоки формирования адреса, первый 3 и второй 4 блоки памяти микрокоманд, коммутатор 5, регистр 6 микрокоманд, блок 7 провер О ки условий, выходы 8 и 9 первого и второго блоков формирования адреса, выходы 1 О и 11 кода операций и логических условий соответственно первого и второго блоков памяти 55 микрокоманд, выходы 12 и 13 кода адреса соответственно первого и второго блоков памяти микрокоманд, выкода адреса которых соединены соответственно с информационными входами, первого и второго блоков Формирования адреса.Кроме того, каждый из блоков Формирования адреса содержит регистр, коммутатор и сумматор, причем выход регистра соединен с информационным входом сумматора и является выходом блока, информационный вход регистра соединен с выходом коммутатора, первый и второй управляющие Входы которого являются соответственно первым и вторым управляющими входами блока, первый информационный вход коммутатора соединен с выходом сумматора, вход переноса которого подключен к шине единичного потенциала, второй информационный вход коммутатора является информационным входом блока.На фиг. 1 приведена структурная схема предлагаемого микропрограммного устройства управления; на фиг,2 функциональная схема блока проверки условий; на Фиг, 3 - функциональная схема блока формирования адреса; на фиг. 4 и 5 - соответственно граф-схема микропрограммы и принцип ее размещения в блоках памяти предлагаемого устройства; на фиг, 6 принцип размещения в блокахпамяти предлагаемого устройства микропро. - граммы, приведенной в описании известного устройства 3 ; на фиг 7 размещение этой микропрограммы в блоках памяти известного устройства; на фиг. 8 - график уменьшения объема при применении предлагаемого устройства в сравнении с известным устройством в зависимости от про 40 центного отношения числа условных вершин к операторным в граф-схемах, используемых в них микропрограмм. Работу устройства рассмотрим напримере выполнения микропрограммы,граф-схема которой изображена нафиг, 4,Здесь у;(где= 1, 10 являетсяуправляющей частью -й микрокоманды, е (где 3 = 1, 3)-кодом 3-гопроверяемого логического условияВ(где и = 0,5) и С(где ш = 0,3)адресами ячеек соответственно блоков 3 и 4 памяти, по которомы храняться микрокоманды, при этом здесьпредполагается, что отличие значений адресов В от Вд+ и Сот С+1составляет единицу. Размещение микропрограммы в блоках 3 и 4 памятипредлагаемого устройства показанона фиг, 5, В устройстве адрес следующей микрокмоанды, считываемый изблока памяти (первого 3 или второго 4), равен либо адресу предыдущеймикрокоманды этого блоха, увеличенному на единицу, либо определяетсяполем адреса предыдущей микрокоманды соседнего блока памяти,Устройство работает следуащимобразом.В исходном состоянии регистр 6обнуляется, а в регистр первогоблока 1 формирования адреса заносится начальный адрес В выполняемоймикропрограммы (цепи синхронизации,обнуления и занесения адреса В начертежах с целью упрощения не показаны). Так как на первый информационный вход блока 7 проверки условийпоступает нулевой код, то на первом17 и втором 18 выходах этого блокаустанавливаются сигналы логическойединицы и логического нуля соответственно. Сигнал логической единицыразрешает запись через коммутатор 5управляющий части у михрокоманды, 1151962считанной из первого блока 3 памяти по адресу Во в регистр 6, а также запись адреса В. в регистр первого блока 1 формирования адреса с выхода сумматора и адреса с выхода 12 пер ваго блока 3 памяти в регистр второго блока 2 формирования адреса (для .считываемой в данный момент микрокоманды этот адрес является нулевым). За, пись информации в регистры блоков 1 и 2 10 формирования адреса и в регистр 6 осуществляется одним импульсом. Иикрокоманда, считанная из первого блока 3 памяти по адресу В, становится текущей и выполняется. Одновременно 15 с ее выполнением происходит считывание следующей микрокаманды из первого блока 3 памяти по адресу В, а также микрокоманды иэ второго блока 4 памяти по нулевому адресу. Однако поскальку в поле кода проверяемого логического уровня текущей микрокоманды находится нулевой код, то на первом 17 и втором 18 выходах блока 7 проверки условий логические сигналы не 25 изменяются, Это приводит к тому, что в регистр 6 .будет записано значение у микрокоманды, считанной из первого блока 3 памяти по адресу 5. Так как в поле кода проверяемого ЗО логического условия этой микрокоманды также находится нулевой код, то следующей записанной в регистр б микрокомандой будет микрокоманда, считанная с первого блока 3 памяти по адресу В, при этом в регистр первого блока 1 Формирования адреса будет записан адрес В, с выхода его сумматора, а в регистр второго блока 2 формирования адреса - адрес Со 411 с выхода 12 первого блока 3 памяти. Во время выполнения этой микрокоманды будет одновременно происходить считывание .двух возможных следующих микрокоманд иэ первого блока 3 па мяти по адресу 3, и второго блока 4 памяти по адресу С , Так как в поле кода проверяемого логического условия текущей микрокоманды находится код условиями, то в зависимости от 5 О его выполнения или невыполнения будут изменены или не изменены логические сигналы на выходах 17 и 18 блока 7проверки условий, Так, если условиевыполняется, то. на первом 17 и втором 18 выходах блока 7 проверки условий вырабатываются сигналы логического нуля и логической единицы соответственно, Они разрешат запись микрокоманды, считанной по адресу С из второго блока 4 памяти в регистр 6, адреса В с выхода 13 второго блока 4 памяти в регистр первого блока 1 Формирования адреса и адреса С в регистр второго блока 2 Формирования адреса с выхода его сумматора, Если же условие а не выполняется, то на первом 17 н втором 18 выходах блока 7 проверки условий останутся сигналы логической единицы и логического нуля соответственно, По ням разрешается запись значения у микрокоманды, считанной из первого блока 3 памяти по адресу В, адреса В - в регистр первого блока 1 формирования адреса с выхода его сумматора, нулевого адреса - с выхода 12 первого блока 3 памяти в регистр второго блока 2 формирования адреса.Подобным образом устройство работает и при выполнении других микро- команд, В таблице, изображенной на фиг. 5, "О", и "1 в поле кода проверяемого логического условия означают нулевой и единичный коды соответственно, Значение кода "О" используется для записи в регистр 6 управляющей части и кода проверяемого логического условия следующей микро- команды, считанной из первого блока 3 памяти, а значение "1" - для запи- си в регистр 6 управляющей части и кода проверяемого логического условия следующей микрокомнды, считанной из второго блока 4 памяти, Использование этих кодов позволяет разместить в блоках 3 и 4 памяти устройства любую микропрограмму.Оценим требуемую суммарную емкость двух блоков памяти предлагаемого устройства по отношению к требуемой суммарной емкости двух блоков известного фиг. 6 и 7) устройства. Пусть в микропрограммах, размещаемых в двух блоках памяти, содержится Х операторных и У условных вершин. При этом необходима учитывать, что во второй блок памяти известного устрой- ства помещаются мнкрокоманды, которые могут выполняться после условных вершин. Тогда число микрокоманд, расположенных в первом блоке памяти известного устройства будет определяться разностью Х-У и, следовательно, требуемая емкость .первого блока пат,е, от соотношевершин к числу мяти известного устройства будет равна этому значению. Во втором же блоке памяти хранится У микрокоманд, что как правило значительно меньше Х-У. Однако, так как значения адресов 5 микрокоманд, хранимых во втором блоке памяти, определяются значениями адресов соответствующих микрокоманд, хранимых в первом блоке памяти, то емкость второго блока памяти должна быть почти такой же как и первого, Как показано на фиг, 7, во втором блоке памяти хранится всего две микрокоманды, но они расположены не по адресам В , Ва по адресам В и В 5 15 и емкость второго блока. памяти поэтому составляет 6 ячеек, что можно считать примерно равно емкости первого блока памяти. Таким образом, суммарная емкость двух блоков памяти 20 известного у,." с.яства б;дет равна (Х-У) 2В предлагаемом устройстве суммарная емкость двух блоков памяти останется равной Х (фиг, 6). Суммарная емкость двух блоков памяти в предлагаемом устройстве будет меньше, чем в известном устройстве в К раз, где К определяется соотношением 962 8операторных, в реализуемых микропрограммах будет зависить конкретное значение К, На фиг. 8 представленаузависимость К от - 1007. Из графикау видно, что при значениях - 1007. в пределах 20-307 объем памяти при использовании предлагаемого устройства уменьшается в 1,6-1,4 раза по сравнению с известным устройством, А поскольку основные затраты оборудования при построении микропрограммных устройств управления идут на управляющую память, то применение предлагаемого устройства более экономично по сравнению с известным устройством, при этом быстродействие его останется таким же.Пусть в предлагаемом и в известном устройствах число микрокоманд гУ расположенных во втором блоке памятиФ1 в 2 раз меньше, чем число микрокоманд, расположенных в первом блоке памяти, тогда длина адресного ноля микрокоманд, расположенных в первом блоке памяти предлагаемого устройства, меньше, чем длина адресного поля микрокоманд, расположенных в првом блоке памяти известного устройства на щ, разрядов, При больших объемах первого блока памяти и малых объемах второго блока памяти этот факт также приводит к значительному сокращению оборудования.

СмотретьЗаявка

3654671, 19.09.1983

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

СОЛОВЕЙ АЛЕКСАНДР ВЛАДИМИРОВИЧ, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.04.1985

Код ссылки

<a href="https://patents.su/10-1151962-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Многотактное микропрограммное устройство управления

Случайный патент: Магнитный сепаратор