Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1265769

Авторы: Алексенко, Балашов, Бжезинский, Виноградов, Колесников, Куприянов

Текст

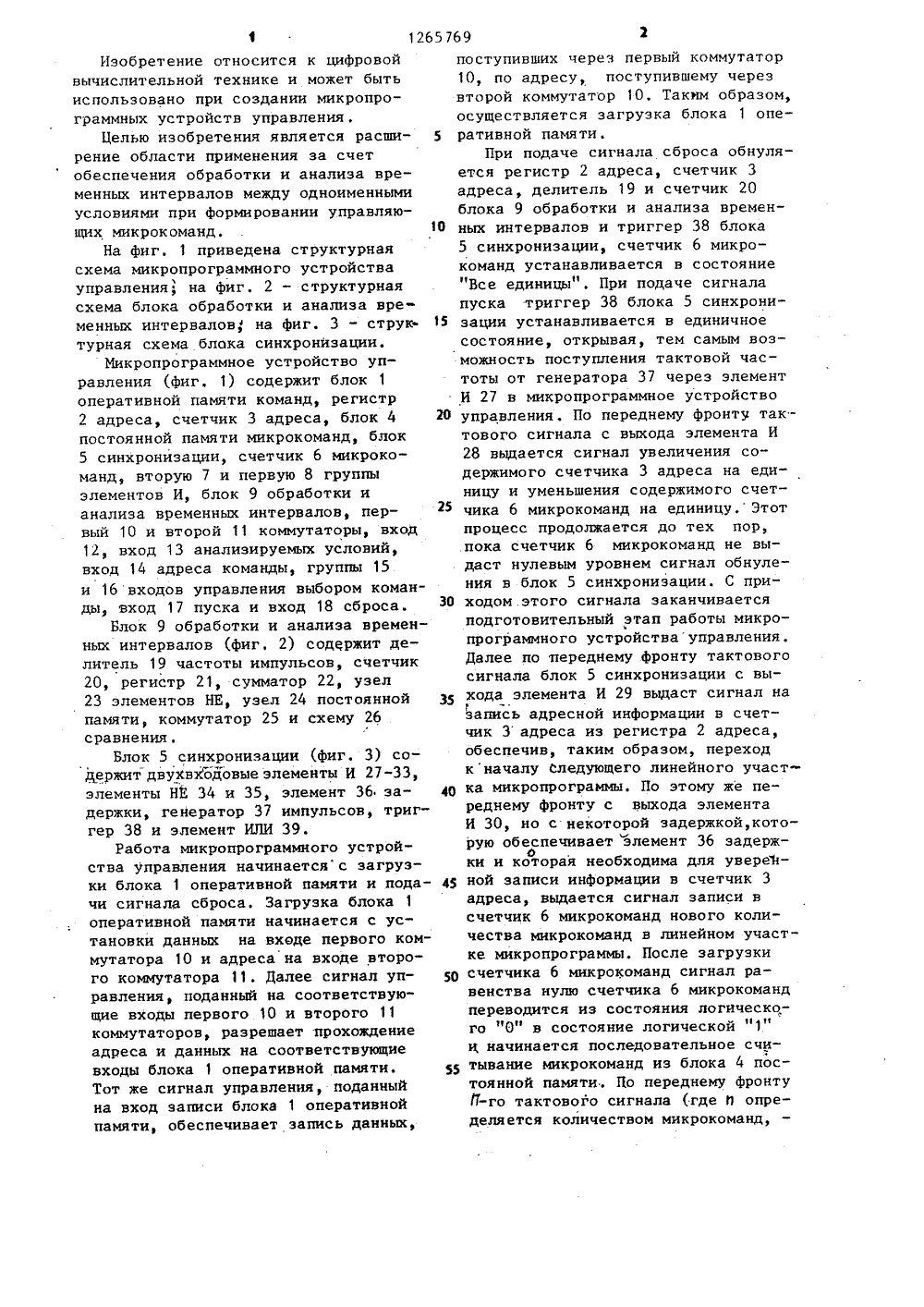

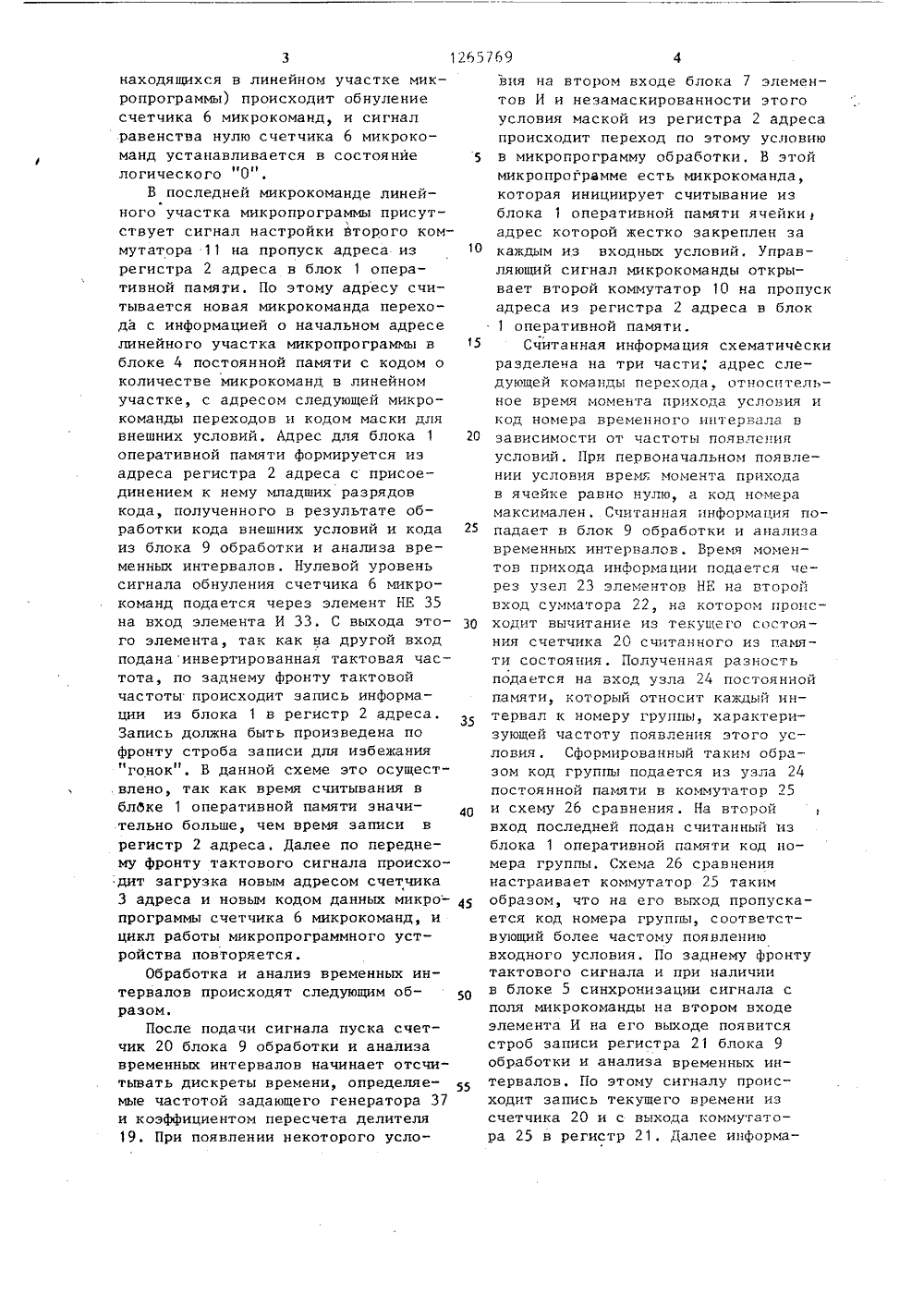

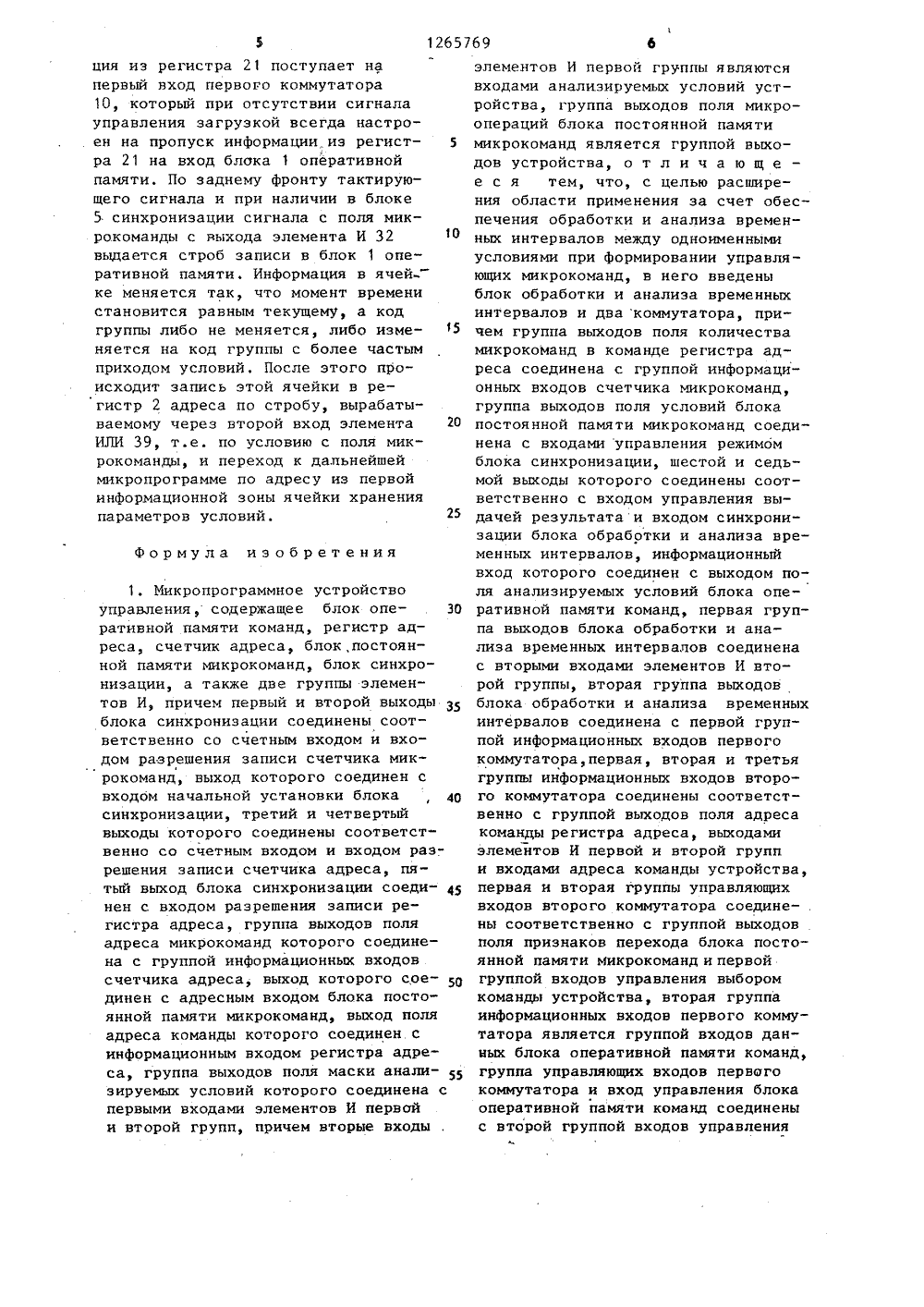

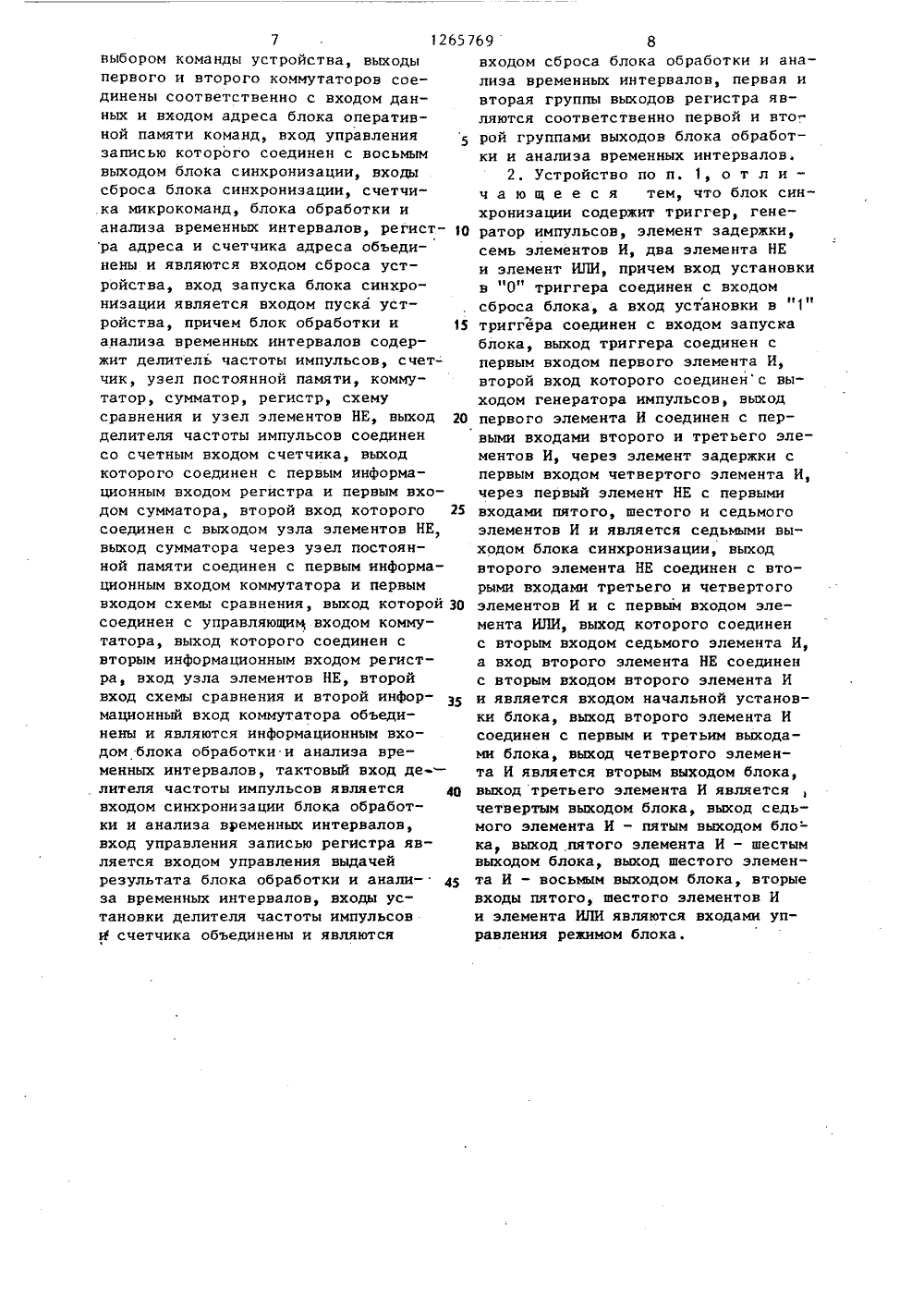

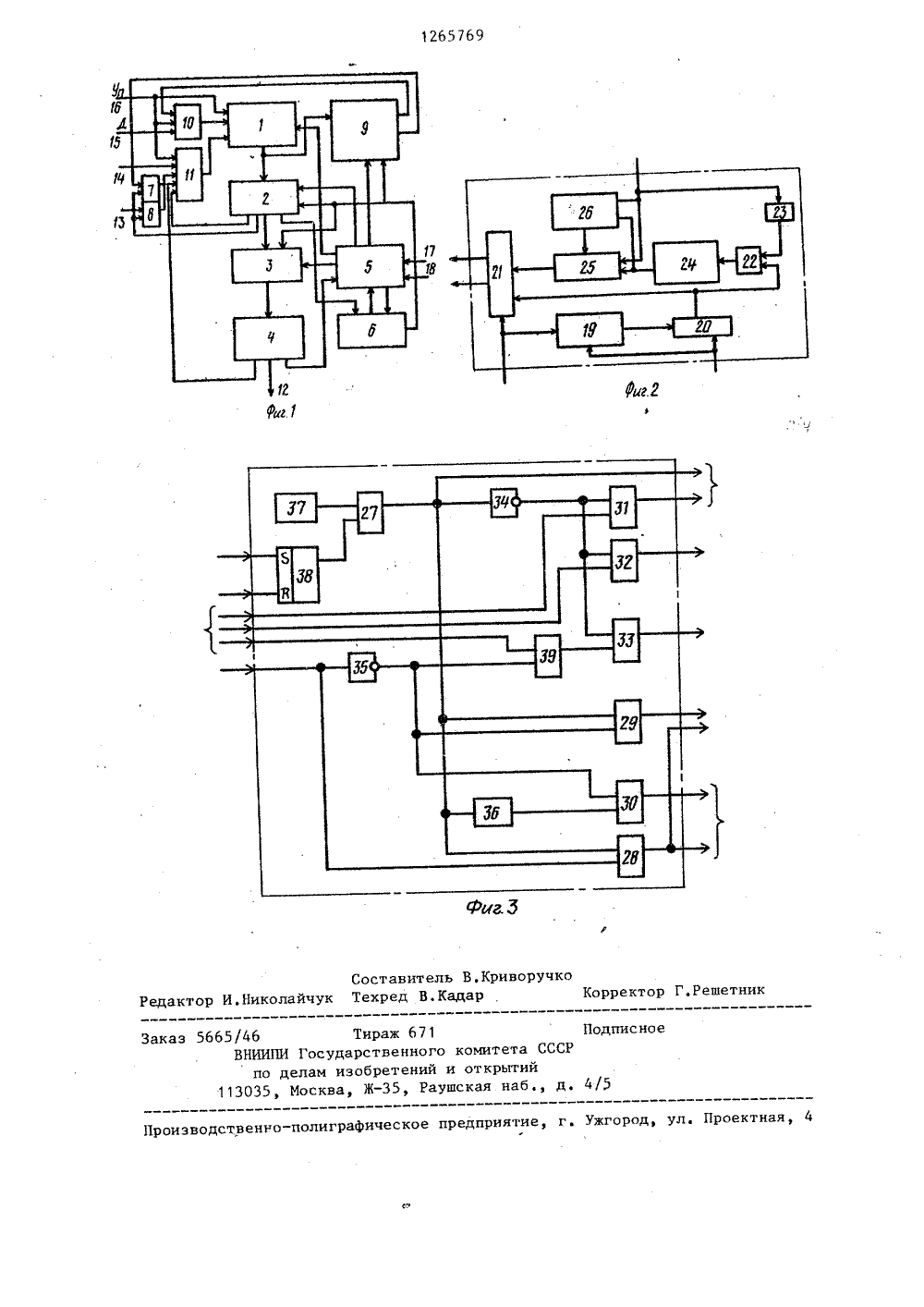

СООЗ СОВЕТСНИХОЦИАЛИСТИЧЕСНИХ РЕСПУБЛ ЕТЕНИЯ ССР5.упльнои техн ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫ ОПИСАНИЕ ИЗОБ К АВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретение относится к областицифровой вычислите ики иможет быть использовано при с да.зоаа 7(Ю 4 С 06 Р 9 22 нии микропрограммных устройств управления. Целью изобретения являетсярасширение области применения засчет обеспечения обработки и анализавременных интервалов между одноименными условиями.при формирований управляющих микрокоманд, Устройствосодержит блок оперативной памяти команд, регистр адреса, счетчик адреса, блок постоянной памяти микрокоманд, блок синхронизации, счетчикмикрокоманд, две группы элементов И,блок обработки и анализа временныхинтервалов и два коммутатора. Указанная совокупность техническихсредств позволяет достичь цели изобретения. 1 з.п. ф-лы, 3 ил.1 1265 7 Изобретение относится к цифровой вычислительной технике и может быть использовано при создании микропрограммных устройств управления .Целью изобретения является расширение области применения за счетобеспечения обработки и анализа временных интервалов между одноименнымиусловиями при формировании управляющих микрокоманд. 1 ОНа фиг. 1 приведена структурнаясхема микропрограммного устройствауправления на фиг. 2 - структурнаясхема блока обработки и анализа временных интерваловф на фиг. 3 - структурная схема блока синхронизации.Микропрограммное устройство управления (фиг. 1) содержит блок 1оперативной памяти команд, регистр2 адреса, счетчик 3 адреса, блок 4 20постоянной памяти микрокоманд, блок5 синхронизации, счетчик 6 микрокоманд, вторую 7 и первую 8 группыэлементов И, блок 9 обработки ианализа временных интервалов, первый 10 и второй 11 коммутаторы, вход12, вход 13 анализируемых условий,вход 14 адреса команды, группы 15и 16 входов управления выбором команды вход 17 пуска и вход 18 сброса.Блок 9 обработки и анализа временных интервалов (фиг, 2) содержит делитель 19 частоты импульсов, счетчик20, регистр 21, сумматор 22, узел23 элементов НЕ, узел 24 постоянной 35памяти, коммутатор 25 и схему 26сравнения,Блок 5 синхронизации (фиг. 3) содержит двухвходовые элементы И 27-33,элементы НЕ 34 и 35, элемент 36 задержки, генератор 37 импульсов, триггер 38 и элемент ИЛИ 39.Работа микропрограммного устройства управления начинается с загрузки блока 1 оперативной памяти и подачи сигнала сброса. Загрузка блока 1оперативной памяти начинается с установки данных на входе первого коммутатора 10 и адреса на входе второго коммутатора 11. Далее сигнал управления, поданный на соответствующие входы первого 10 и второго 11коммутаторов, разрешает прохождениеадреса и данных на соответствующиевходы блока 1 оперативной памяти. 55Тот же сигнал управления, поданныйна вход записи блока 1 оперативнойпамяти, обеспечивает запись данных,69поступивших через первый коммутатор 10, по адресу, поступившему через второй коммутатор 1 О. Таким образом,осуществляется загрузка блока 1 оперативной памяти. При подаче сигнала сброса обнуляется регистр 2 адреса, счетчик 3 адреса, делитель 19 и счетчик 20 блока 9 обработки и анализа временных интервалов и триггер 38 блока 5 синхронизации, счетчик 6 микро- команд устанавливается в состояние "Все единицы", При подаче сигнала пуска триггер 38 блока 5 синхронизации устанавливается в единичное состояние, открывая, тем самым возможность поступления тактовой частоты от генератора 37 через элементИ 27 в микропрограммное устройствоуправления. По переднему фронту тактового сигнала с выхода элемента И 28 выдается сигнал увеличения содержимого счетчика 3 адреса на единицу и уменьшения содержимого счетчика 6 микрокоманд на единицу. Этотпроцесс продолжается до тех пор, пока счетчик 6 микрокоманд не выдаст нулевым уровнем сигнал обнуления в блок 5 синхронизации. С приходом. этого сигнала заканчивается подготовительный этап работы микропрограммного устройствауправления.Далее по переднему фронту тактовогосигнала блок 5 синхронизации с выхода элемента И 29 выдаст сигнал на запись адресной информации в счетчик 3 адреса из регистра 2 адреса, обеспечив, таким образом, переходкначалу следующего линейного участка микропрограммы. По этому же переднему фронту с выхода элементаИ 30, но с некоторой задержкой, которую обеспечивает элемент 36 задержки и которая необходима для уверенной записи информации в счетчик 3 адреса, выдается сигнал записи в счетчик 6 микрокоманд нового количества микрокоманд в линейном участке микропрограммы. После загрузки счетчика 6 микрокоманд сигнал равенства нулю счетчика 6 микрокомандпереводится из состояния логического "0" в состояние логической "1"и начинается последовательное считывание микрокоманд из блока 4 постоянной памяти. По переднему фронту П-го тактового сигнала (где 0 определяется количеством микрокоманд, 1265769находящихся в линейном участке микропрограммы) происходит обнуление счетчика 6 микрокоманд, и сигнал равенства нулю счетчика 6 микрокоманд устанавливается в состояние логического "0".В последней микрокоманде линейного участка микропрограммы присутствует сигнал настройки второго коммутатора 11 на пропуск адреса из регистра 2 адреса в блок 1 оперативной памяти. По этому адресу считывается новая микрокоманда перехода с информацией о начальном адресе линейного участка микропрограммы в блоке 4 постоянной памяти с кодом о количестве микрокоманд в линейном участке, с адресом следующей микро- команды переходов и кодом маски для внешних условий, Адрес для блока 1 оперативной памяти формируется из адреса регистра 2 адреса с присоединением к нему младших разрядов кода, полученного в результате обработки кода внешних условий и кода из блока 9 обработки и анализа временных интервалов. Нулевой уровень сигнала обнуления счетчика б микро- команд подается через элемент НЕ 35 на вход элемента И 33. С выхода этого элемента, так как на другой вход поданаинвертированная тактовая частота, по зацнему фронту тактовой частоты происходит запись информации из блока 1 в регистр 2 адреса. Запись должна быть произведена по фронту строба записи для избежания гонок". В данной схеме это осущест.влено, так как время считывания в блбке 1 оперативной памяти значительно больше, чем время записи в регистр 2 адреса. Далее по переднему фронту тактового сигнала происходит загрузка новым адресом счетчика 3 адреса и новым кодом данных микро- программы счетчика 6 микрокоманд, и цикл работы микропрограммного устройства повторяется.Обработка и анализ временных интервалов происходят следующим образом.После подачи сигнала пуска счетчик 20 блока 9 обработки и анализа временных интервалов начинает отсчитывать дискреты времени, определяемые частотой задающего генератора 37 и коэффициентом пересчета делителя 19. При появлении некоторого условия на втором входе блока 7 элементов И и незамаскированности этогоусловия маской из регистра 2 адресапроисходит переход по этому условию 5 в микропрограмму обработки. В этоймикропрограмме есть микрокоманда,которая инициирует считывание изблока 1 оперативной памяти ячейкиадрес которой жестко закреплен за 10 каждым из входных условий, Управ -ляющий сигнал микрокоманды открывает второй коммутатор 10 на пропускадреса из регистра 2 адреса в блок1 оперативной памяти.15 Считанная информация схематическиразделена на три части; адрес следующей команды перехода, относительное время момента прихода условия икод номера временного интервала в 20 зависимости от частоты появленияусловий, При первоначальном появлении условия время момента приходав ячейке равно нулю, а код номерамаксимален. Считанная информация попадает в блок 9 обработки и анализавременных интервалов. Время моментов прихода информации подается через узел 23 элементов НЕ на второйвход сумматора 22, на котором проис- ЭО ходит вычитание из текущего состояния счетчика 20 считанного из памяти состояния. Полученная разностьподается на вход узла 24 постояннойпамяти, который относит каждый интервал к номеру группы, характеризующей частоту появления этого условия. Сформированный таким образом код группы подается из узла 24постоянной памяти в коммутатор 25 40 и схему 26 сравнения. На второйвход последней подан считанный изблока 1 оперативной памяти код номера группы. Схема 26 сравнениянастраивает коммутатор 25 таким 45 образом, что на его выход пропускается код номера группы, соответствующий более частому появлениювходного условия. По заднему фронтутактового сигнала и при наличиив блоке 5 синхронизации сигнала споля микрокоманды на втором входеэлемента И на его выходе появитсястроб записи регистра 21 блока 9обработки и анализа временных интервалов. По этому сигналу происходит запись текущего времени изсчетчика 20 и с выхода коммутатора 25 в регистр 21. Далее информа ция из регистра 21 поступает напервый вход первого коммутатора10, который при отсутствии сигналауправления загрузкой всегда настроен на пропуск информации иэ регистра 21 на вход блока 1 оперативнойпамяти. По заднему фронту тактирующего сигнала и при наличии в блоке5 синхронизации сигнала с поля микрокоманды с выхода элемента И 32выдается строб записи в блок 1 оперативной памяти. Информация в ячейке меняется так, что момент временистановится равным текущему, а кодгруппы либо не меняется, либо изменяется на код группы с более частымприходом условий. После этого происходит запись этой ячейки в регистр 2 адреса по стробу, вырабатываемому через второй вход элементаИЛИ 39, т.е. по условию с поля микрокоманды, и переход к дапьнейшеймикропрограмме по адресу из первойинформационной зоны ячейки храненияпараметров условий. Формула изобретения1265769 элементов И первой группы являютсявходами анализируемых условий уст -ройства, группа выходов поля микроопераций блока постоянной памятимикрокоманд является группой выходов устройства, о т л и ч а ю щ ее с я тем, что, с целью расширения области применения за счет обеспечения обработки и анализа временных интервалов между одноименнымиусловиями при формировании управляющих микрокоманд, в него введеныблок обработки и анализа временныхинтервалов и два коммутатора, причем группа выходов поля количествамикрокоманд в команде регистра адреса соединена с группой информационных входов счетчика микрокоманд,группа выходов поля условий блока 10 иена с входами управления режимомблока синхронизации, шестой и седьмой выходы которого соединены соответственно с входом управления выдачей результатаи входом синхрони 25 зации блока обработки и анализа временных интервалов, информационный 20 постоянной памяти микрокоманд соеди 1. Микропрограммное устройство управления, содержащее блок опе ративной памяти команд, регистр адреса, счетчик адреса, блок,постоянной памяти микрокоманд, блок синхронизации, а также две группы элементов И, причем первый и второй выходы блока синхронизации соединены соответственно со счетным входом и входом разрешения записи счетчика микрокоманд, выход которого соединен с входом начальной установки блока 40 синхронизации, третий и четвертый выходы которого соединены соответственно со счетным входом и входом разрешения записи счетчика адреса, пятый выход блока синхронизации соеди нен с входом разрешения записи регистра адреса, группа выходов поля адреса микрокоманд которого соединена с группой информационных входов счетчика адреса, выход которого сое динен с адресным входом блока постоянной памяти микрокоманд, выход поля адреса команды которого соединен. с информационным входом регистра адреса, группа выходов поля маски анали зируемых условий которого соединена с первыми входами элементов И первой и второй групп, причем вторые входы вход которого соединен с выходом поля анализируемых условий блока оперативной памяти команд, первая группа выходов блока обработки и анализа временных интервалов соединена с вторыми входами элементов И второй группы, вторая группа выходовблока обработки и анализа временныхинтервалов соединена с первой группой информационных входов первого коммутатора, первая, вторая и третья группы информационных входов второго коммутатора соединены соответственно с группой выходов поля адреса команды регистра адреса, выходами элементов И первой и второй групп и входами адреса команды устройства, первая и вторая группы управляющих входов второго коммутатора соедине- . ны соответственно с группой выходовполя признаков перехода блока постоянной памяти микрокоманд и первой группой входов управления выбором команды устройства, вторая группаинформационных входов первого коммутатора является группой входов даныых блока оперативной памяти команд, группа управляющих входов первого коммутатора и вход управления блокаоперативной памяти команд соединеныс второй группой входов управленияЖ69 8входом сброса блока обработки и анализа временных интервалов, первая и вторая группы выходов регистра являются соответственно первой и втог рой группами выходов блока обработки и анализа временных интервалов.2. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что блок синхронизации содержит триггер, генератор импульсов, элемент задержки, семь элементов И, два элемента НЕ и элемент ИЛИ, причем вход установки в "0" триггера соединен с входом сброса блока, а вход установки в "1" триггера соединен с входом запуска блока, выход триггера соединен с первым входом первого элемента И, второй вход которого соединенс выходом генератора импульсов, выход первого элемента И соединен с первыми входами второго и третьего элементов И, через элемент задержки с первым входом четвертого элемента И, через первый элемент НЕ с первыми входами пятого, шестого и седьмого элементов И и является седьмыми выходом блока синхронизации, выход второго элемента НЕ соединен с вторыми входами третьего и четвертого элементов И и с первым входом элемента ИЛИ, выход которого соединен с вторым входом седьмого элемента И, а вход второго элемента НЕ соединен с вторым входом второго элемента И и является входом начальной установки блока, выход второго элемента И соединен с первым и третьим выходами блока, выход четвертого элемента И является вторым выходом блока, выход третьего элемента И является четвертым выходом блока, выход седьмого элемента И - пятым выходом бло- ка выход пятого элемента И - шестым выходом блока, выход шестого элемента И - восьмым выходом блока, вторые входы пятого, шестого элементов И и элемента ИЛИ являются входами управления режимом блока. 7 1265 7 выбором команды устройства, выходы первого и второго коммутаторов соединены соответственно с входом данных и входом адреса блока оперативной памяти команд, вход управления записью которого соединен с восьмым выходом блока синхронизации, входы сброса блока синхронизации, счетчика микрокоманд, блока обработки и анализа временных интервалов, регист ра адреса и счетчика адреса объединены и являются входом сброса устройства, вход запуска блока синхронизации является входом пуска устройства, причем блок обработки и 15 анализа временных интервалов содержит делитель частоты импульсов, счетчик, узел постоянной памяти, коммутатор, сумматор, регистр, схему сравнения и узел элементов НЕ, выход 20 делителя частоты импульсов соединен со счетным входом счетчика, выход которого соединен с первым информационным входом регистра и первым входом сумматора, второй вход которого 25 соединен с выходом узла элементов НЕ, выход сумматора через узел постоянной памяти соединен с первым информационным входом коммутатора и первым входом схемы сравнения, выход которой 30 соединен с управляющим, входом коммутатора, выход которого соединен с вторым информационным входом регистра, вход узла элементов НЕ, второй вход схемы сравнения и второй информационный вход коммутатора объединены и являются информационным входом блока обработки и анализа временных интервалов, тактовый вход де лителя частоты импульсов является 40 входом синхронизации блока обработки и анализа временных интервалов, вход управления записью регистра является входом управления выдачей результата блока обработки и анали за временных интервалов, входы установки делителя частоты импульсов И счетчика объединены и являются1265769 гФ ФАЗ Составитель В.Криворучактор И.Николайчук Техред В.Кадар.Решетник Корре 65/46 Тираж 671 ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий 113035, Москва, Ж, Раушская наб., д, дписное роиэводственно-полиграфическое предприятие,город, ул. Проектная,

СмотретьЗаявка

3755415, 12.06.1984

ПРЕДПРИЯТИЕ ПЯ Г-4149

АЛЕКСЕНКО АНДРЕЙ ГЕННАДИЕВИЧ, БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, БЖЕЗИНСКИЙ АЛЕКСАНДР СЕМЕНОВИЧ, ВИНОГРАДОВ ВЛАДИСЛАВ БОРИСОВИЧ, КОЛЕСНИКОВ ВЯЧЕСЛАВ ВАСИЛЬЕВИЧ, КУПРИЯНОВ МИХАИЛ СТЕПАНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.10.1986

Код ссылки

<a href="https://patents.su/6-1265769-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Делительно-множительное устройство

Следующий патент: Устройство микропрограммного управления

Случайный патент: Стрелковый тренажер