Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

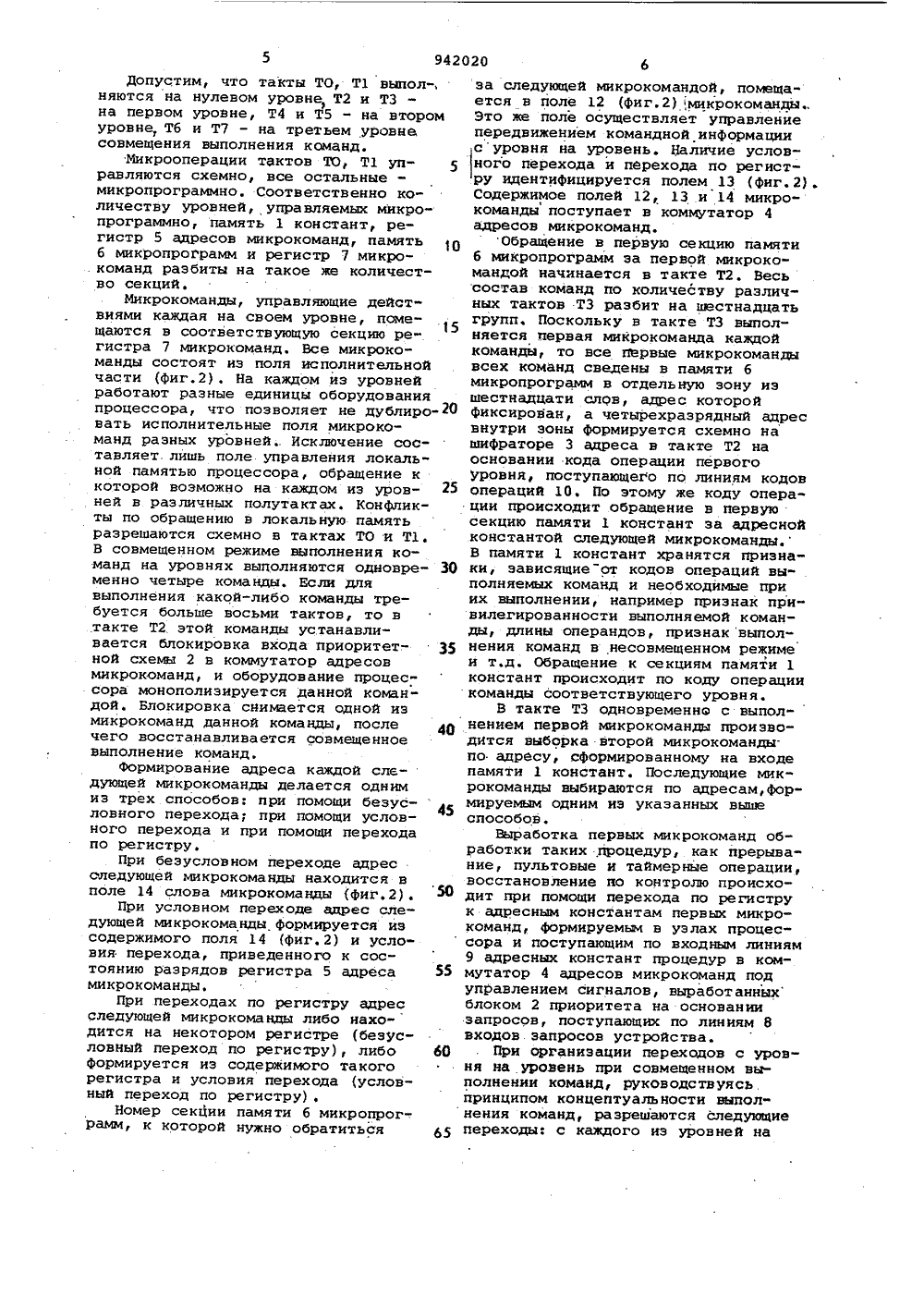

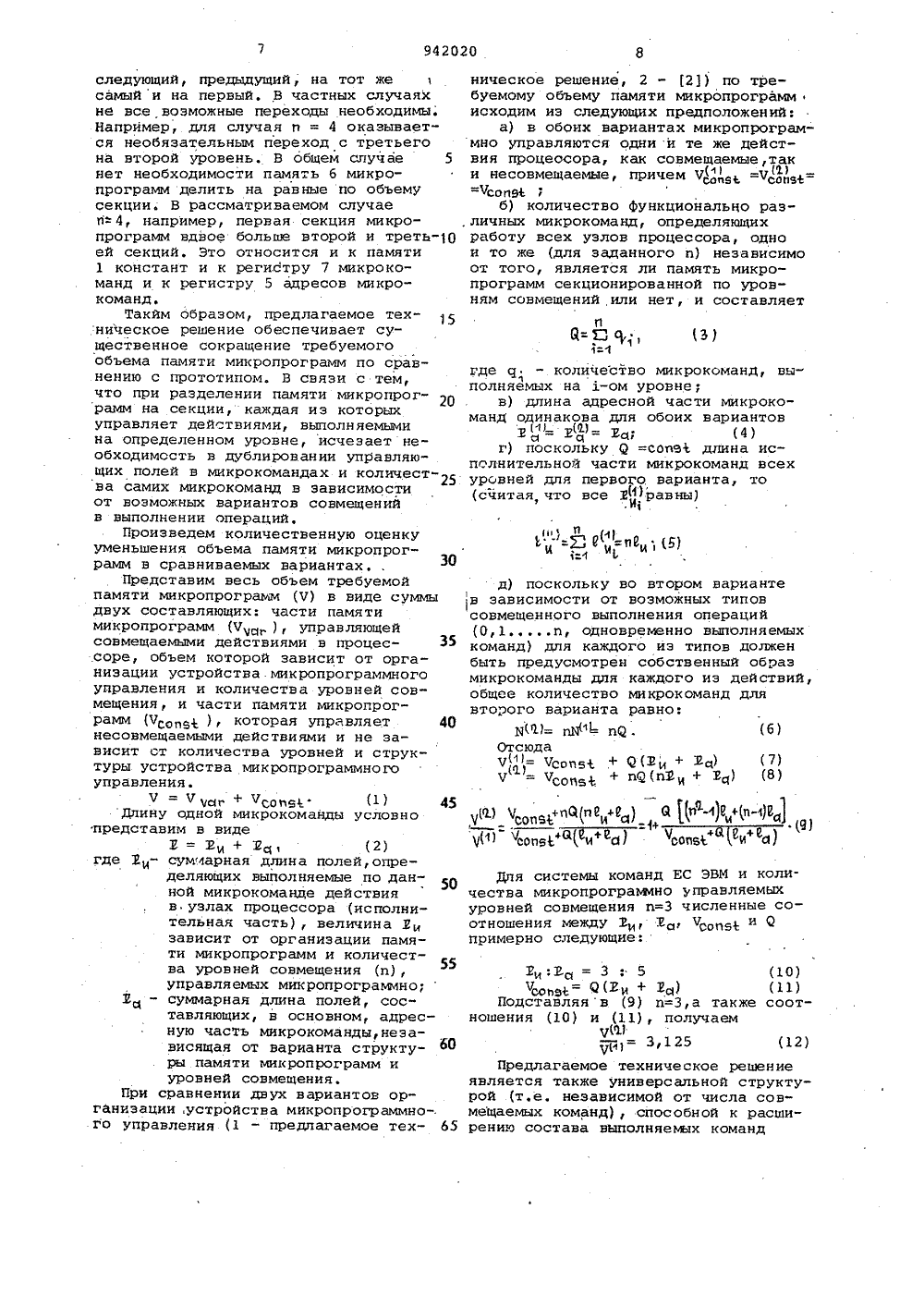

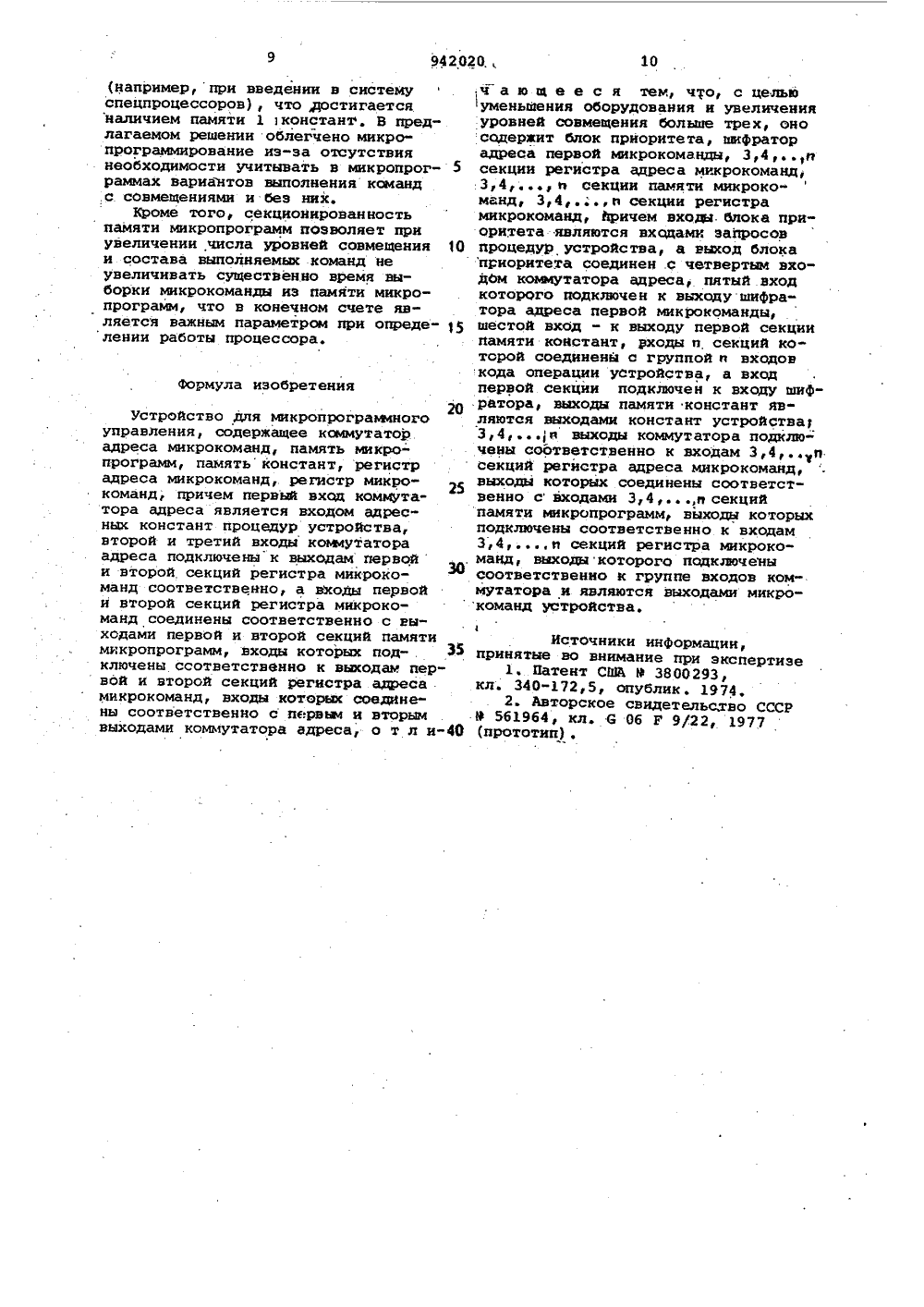

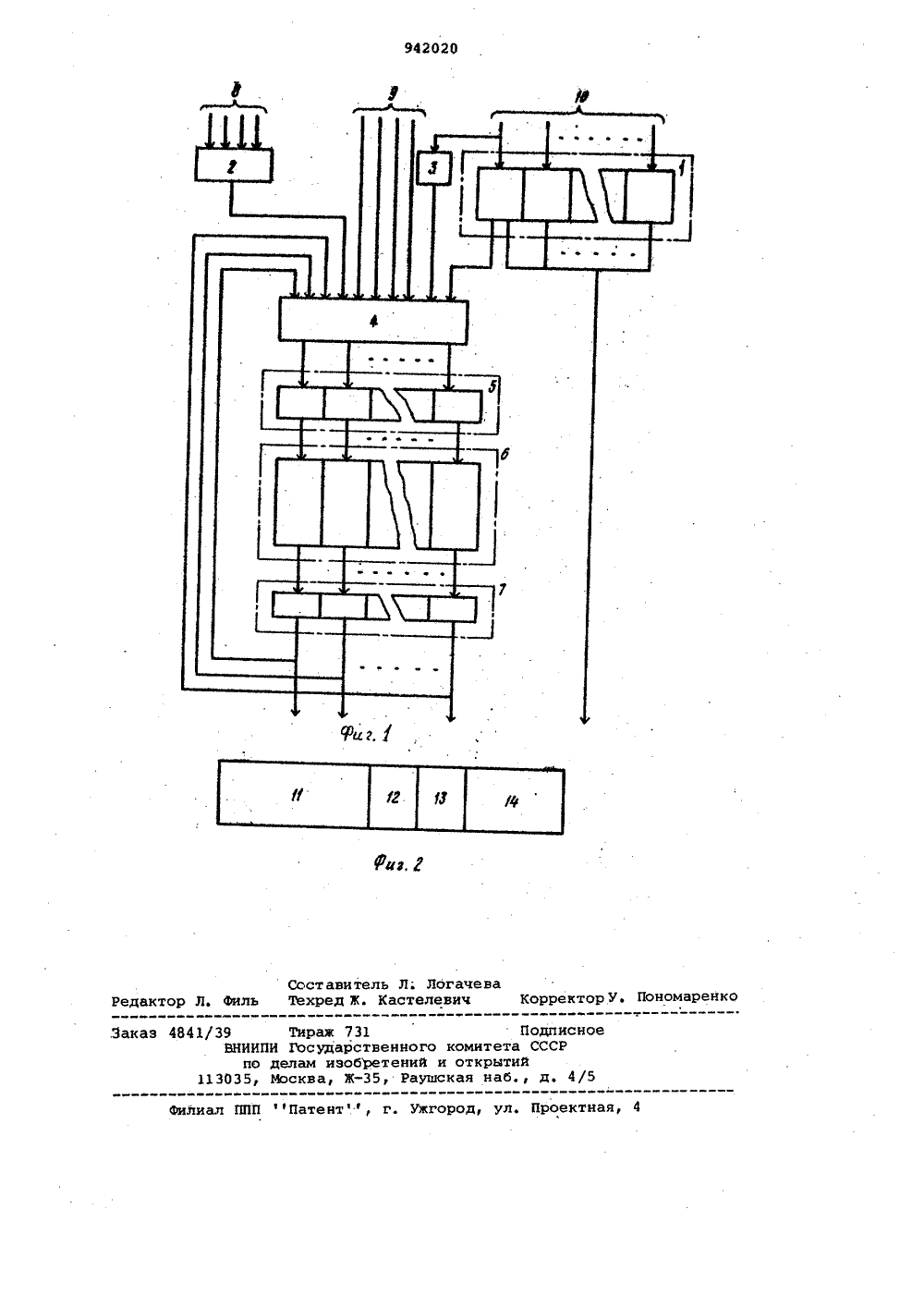

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(22) Заявлено 2 И 0,80 (2) 3219393/18-24 с присоединением заявки Йо И)М.КЛ.з О 06 Р 9/22 Государственный комитет СССР но делам изобретений и открытийОпубликовано 07,07.82, Бюллетень Мф 25 Дата опубликования описания 07.0782(54 ) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛБНИЯ Изобретение относится к вычислительной технике и предназначено для работы в центральном процессоре быстродействующих ЭВМ с уровнями совмещения выполнения команд (и - конечное число уровней совмещения выполнения команд).Известно устройство мчкропрограммного управления, содержащее группы элементов И, ИЛИ, НЕ, блоки основной памяти микропрограмм. Из блоков основной и дополнительной памяти микропрограмм через элементы И, ИЛИ микрокоманда выбираетсяна общий регистр микрокоманд. Увеличение про" изводительности достигается путем совмещенного выполнения последней микрокоманды из последовательности микрокоманд, необходимой для выполнения системной команды, с обращением к первой микрокоманде последовательности.следующей системной команды 1.Недостатком такого устройства является то, что оно обеспечивае-,. только двухуровневое совмещение.Это не позволяет достигнуть высокой скорости обработки команд, требуемой в больших вычислительных системах,Наиболее близким к предлагаемому является устройство микропрограммного управления, предназначенное для работы в составе процессора с тремя уровнями совмещения ксыанд.Это устройство;содержит группы элементов И, ИЛИ, НЕ, блоки основной и дополнительной памяти микропрограмм, первый и второй регистры адреса, регистры кода операции первой команды и второй команды, регистры основной и дополнительной микрокоманд и узел модификации адреса микрокоманды. Из двух блоков основной и дополнительной памяти микропрог- рамм синхронно выбираются две микро команды. Действия, зависящие от кодаоперации системной команды, управляются основной микрокомандрй, а действия, зависящие от такта выпол" нения команды, управляются микроко" 20 мандой, выбираемой из дополнительнойпамяти микропрограмм. Система адре. сации микрокоманд обеспечивает обращение к основной или дополнительной памяти микропрограмм без потери вре мени 2) . К недостаткам известного устройства относится то, что в дополнительной памяти микропрограмм необходимо для каждого случая выполнения команд (с совмещением выполнения трехкоманд, двух команд и без овмещения) иметь свой образ микрокоманды.Это существенно увеличивает емкостьпамяти микропрограмм и затрудняетмикропрограммирование, По этой причине нецелесообразно использовать такое устройство в центральном процес.соре с числом уровней совмещения выполнения команд больше трех.Кроме того, расширение состававыполняемых команд невозможно без 10увеличения объема памяти микропрограмм, объема оборудования устройства микропрограммного управления ипроцессора,Цель изобРетения - уменьшениеоборудования и упрощение микропрограммирования для процессора с количеством уровней совмещения больше)трех.Поставленная цель достигаетсятем, что в устройство микропрограммного управления, содержащее .коммутатор адреса микрокоманд, памятьмикропрограмм, память койстант, регистр адреса микрокоманд, регистрмикрокоманд, причем первый вход коммутатора адреса, является входом адресных констант процедур устройства,второй и третий входы коммутатораадреса подключены к выходам первой,и второй секций регистра микрокоманд соответственно, а входы первойи второй секций регистра микрокомандсоединены соответственно с выходамипервой и второй секций памяти микропрограмм, входы которых подключены 35соответственно к выходам первой ивторой секций регистра адреса микрокоманд, входы которых соединены со-.ответственно с первым и вторым выходами коммутатора адреса, введены 40блок приоритета, шифратор адресапервой микрокоманды, 3,4 и секциирегистра адреса микрокоманд,3,4 ясекции памяти микрокоманд, 3,4,псекции регистра микрокоманд, причем 45входы блока приоритета являются входами запросов процедур устройства,а выход блока приоритета соединен счетвертым входом коммутатора адреса,пятый вход которого подключен квыходу шифратора адреса первой микрокоманды, шестой вход - к выходупервой секции памяти констант, входый секций которой соединены с группой и входов кбда операции устройства, а вход первой секции подключенк входу шифратора, выходы памяти констант являются выходами константустройства, 3,4,п выходы коммутатора подключены соответственно квходам 3,4, и секций регистра адреса микрокоманд, выходы которыхсоединены соответственно с входами3,4, ь секций памяти микропрограмм,выходы которых подключены соответственно к входам 3,4.;., ь секций ре гистра микрокоманд, выходы которогоподключены соответственно к группевходов коммутатора и являются выходами микрокоманд устройства.На фиг.1 представлена блок-схемапредлагаемого устройства; на фиг.2 -состав микрокоманды,Устройство состоит из памяти 1констант, блока 2 приоритета, шифратора 3 адреса первой микрокоманды,коммутатора 4 адреса микрокоманд,регистра 5 адресов микрокоманд, памяти б микропрограмм, регистра 7микрокоманд, входов 8 запросов процедур устройства, входов 9 адресныхконстант процедур, входов 10 кодовопераций.Устройство предназначено для обработки команд типа принятых в ЕСЭВМ, процедур восстановления поконтролю, обработки прерываний,таймерной и пультовых операций.Рассмотрим работу предлагаемогоустройства, ограничившись четырьмяуровнями совмещения команд, на примере выполнения команды Формата РХ,Команда формата РХ (например,сложение с Фиксированной точкой)вЫполняется в процессоре за восемьмашинных тактов (каждый из которыхвыполняется на определенном уровнесовмещения);ТО - такт работы блока 2 приоритета обслуживания запросов на выполнение в процессоре процедур восстановления по контролю, обработкипрерывания, пультовой (сервисной)операции, таймерной операции или команды,Т 1 - такт выборки команды из буфера командных слов и расшифровкикоманды.Т 2 - такт модификации адреса. Вэтом такте модифицируется адрес обращения в главную память. Разновидностей действий, выполняемых в этомтакте - четыре. Эти четыре типадействий инициируются схемными приказами, полученныМи на основаниикода операции команды на шифраторе3 адреса первой микрокоманды в тактеТ 1,ТЗ - такт трансляции адреса. Втакте ТЗ производится преобразованиелогического адреса в абсолютный,если задан режим переадресации и выдается запрос в буферную (главную)память.Т 4 " такт работы буферной памяти,Т 5 " такт получения операндов избуферной (главной) памяти и из локальной памяти процессора и передачиих в операционное устройство.Тб - такт работы операционногоустройстваТ 7 - такт записи результата операции в местную память процессора.Допустим, что такты ТО, Т 1 выпол",няются на нулевом уровне Т 2 и ТЗ)на первом уровне, Т 4 и Т 5 - на второмуровне, Тб и Т 7 - на третьем уровнесовмещения выполнения команд.Микрооперации тактов ТО, Т 1 управляются схемно, все остальныемикропрограммно. Соответственно количеству уровней, управляемых микропрограммно, память 1 констант, регистр 5 адресов микрокоманд, памятьб микропрограмм и регистр 7 микрокоманд разбиты на такое же количество секций.Микрокоманды, управляющие действиями каждая на своем уровне, помещаются в соответствующую секцию ре"гистра 7 микрокоманд. Все микрокоманды состоят иэ поля исполнительнойчасти (фиг.2), На каждом иэ уровнейработают разные единицы оборудованияпроцессора, что позволяет не дублиро"20вать исполнительные поля микрокоманд разных уровней Исключение составляет лишь поле управления локальной памятью процессора, обращение ккоторой возможно на каждом из уровней в различных полутактах, Конфликты по обращению в локальную памятьразрешаются схемно в тактах ТО и Т 1.В совмещенном режиме выполнения команд на уровнях выполняются одновременно четыре команды. Боли длявыполнения какой-либо команды требуется больше восьми тактов, то в.такте Т 2. этой команды устанавливается блокировка входа приоритетной схемы 2 в коммутатор адресовмикрокоманд, и оборудование процессора монополиэируется данной командой. Блокировка снимается одной иэмикрокоманд данной команды, после 40чего восстанавливается совмещенноевыполнение команд.Формирование адреса каждой следующей микрокоманды делается однимиз трех способов: при помощи безусловного перехода; при помощи условного перехода и при помощи переходапо регистру.При безусловном переходе адресследующей микрокоманды находится вполе 14 слова микрокоманды (Фиг.2) . 50При условном переходе адрес следующей микрокоманды формируется изсодержимого поля 14 (фиг.2) и условия перехода, приведенного к состоянию разрядов регистра 5 адреса 55микрокоманды,При переходах по регистру адресследующей микрокоманды либо нахо"дится на некотором регистре (безусловный переход по регистру), либо 60формируется из содержимого такогорегистра и условия перехода (условный переход по регистру) .Номер секции памяти б микропрогРамм, к которой нужно обратиться 65 за следующей микрокомандой, помещается в поле 12 (фиг.2),микрокомандыЭто же поле осуществляет управлениепередвижением командной информациисуровня на уровень. Наличие условного перехода и перехода по регистру идентифицируется полем 13 (фиг.2).Содержимое полей 12, 13 и 14 микрокоманды поступает в коммутатор 4адресов микрокоманд,Обращение в первую секцию памятиб микропрограмм эа первой микрокомандой начинается в такте Т 2. Весьсостав команд по количеству различных тактов ТЗ разбит на шестнадцатьгрупп. Поскольку в такте ТЗ выполняется первая микрокоманда каждойкоманды, то все первые микрокомандывсех команд сведены в памяти бмикропрограмм в отдельную зону иэшестнадцати слОв, адрес которойфиксирован, а четырехраэрядный адресвнутри эоны Формируется схемно нашифраторе 3 адреса в такте Т 2 наосновании кода операции первогоуровня, поступающего по линиям кодовопераций 10. По этому же коду операции происходит обращение в первуюсекцию памяти 1 констант эа адреснойконстантой следующей микрокоманды.В памяти 1 констант хранятся признаки, зависящие от кодов операций вы- .полняемых команд и необходимые приих выполнении, например признак при"вилегированности выполняемой команды, длины операндов, признаквыполнения команд в несовмещенном режимеи т.д. Обращение к секциям памяти 1констант происходит по коду операциикоманды соответствующего уровня.В такте ТЗ одновременно с выполнением первой микрокоманды производится выборка второй микрокоманды.по адресу, сформированному на входепамяти 1 констант. Последующие микрокоманды выбираются по адресам,формируемым одним иэ указанных вышеспособов.Выработка первых микрокоманд обработки таких процедур, как прерывание, пультовые и таймерные операции,восстановление ио контролю происходит при помощи перехода по региструк адресным константам первых микрокоманд, формируемьж в узлах процессора и поступающим по входным линиям9 адресных констант процедур в коммутатор 4 адресов микрокоманд подуправлением сигналов, выработанныхблоком 2 приоритета на основаниизапросов, поступающих по линиям 8входов запросов устройства.При организации переходов с уровня на уровень при совмещенном выполнении команд, руководствуясьпринципом концептуальности выпол"нения команд, разрешаются следующиепереходы; с каждого из уровней на(например, при введении в систему спецпроцессоров), что достигается наличием памяти 1 констант. В предлагаемом решении облегчено микро" программирование из-за отсутствия необходимости учитывать в микропрог раммах вариантов выполнения команд с совмещениями и без них.Кроме того, секционированность памяти микропрограмм позволяет при увеличении числа уровней совмещения и состава выполняемых команд не увеличивать существенно время выборки микрокоманды из памяти микропрограмм, что в конечном счете является важным параметром при опреде ленни работы процессора. 1 О формула изобретенияУстройство для микропрограммного20 управления, содержащее коммутатор адреса микрокоманд, память микропрограмм, память констант, регистр адреса микрокоманд, регистр микро- команд, причем первый вход коммутатора адреса является входом адреснык констант процедур устройства, второй и третий входы ковюутатора адреса подключенык выходам первой и второй секций регистра микрокоманд соответственно, а входы первой и второй секциЯ регистра микрокоманд соединены соответственно с выходами первой и второй секций памяти микропрограмм, входы которых под- . З ключены ссответственно к вькодам первой и второй секций регистра адреса макрокоманд, входы которыс соединены соответственно с первьв и вторым выходами коммутатора адреса, о т л и"40,ч а ю щ е е с я тем, что, с целью уменьйения оборудования и увеличения :уровней совмещения больше трех, оно содержит блок приоритета, зщфратор адреса первой микрокоманды, 3,4,.п секции регистра адреса микрокоманд, 3,4п секции памяти микрокоманд, 3,4,.;.,и секции регистра микрокоманд, йричем входы. блока приоритета являются входами запросов процедур устройства, а выход блока приоритета соединен .с четвертым входом коыаутатора адреса, пятый вход которого подключен к выходу шифратора адреса первой микрокоманды, шестой вход - к выходу первой секции памяти констант, входы и секций которой соединены с группой п входов кода операции устройства, а вход первой секции подключен к входу шиф" .ратора, выходы памяти констант являются выходами констант устройства 3,4,д выходы коммутатора подклю чены соответственно к входам 3,4, и секций регистра адреса мнкрокоманд, выходы которых соединены соответственно с входами 3,4п секций памяти микропрограмм, выходы которых подключены соответственно к входам 34,п секций регистра микрокоманд, выходы которого подключены соответственно к группе входов коммутатора и являются выходами микро- команд устройства.Источники информации,принятые во внимание при экспертизе 1, Патент СшА 9 3800293,кл. 340-172,5, опублик . 1974. 2. Авторское свидетельсдво СССР 561964 кл, 6 06 Р 9/22, 1977942020 Составитель Л; ЛогачеваТехред Е. Кастелевич Корректор У. Пономарен дактор Л. Фи Филиал ППП 1 Патент.ф, г. Ужгород, Ул. Проектная, 4 731рственнообретенийЖРа Заказ 4841/39 Тираж ВНИИПИ Госуд по делам 113035, Москва

СмотретьЗаявка

3219393, 23.10.1980

ПРЕДПРИЯТИЕ ПЯ М-5769

НИКИТИН АНАТОЛИЙ ИВАНОВИЧ, ЗАК ЛАРИСА СЕМЕНОВНА, МАЛИКОВА НАДЕЖДА МИХАЙЛОВНА

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 07.07.1982

Код ссылки

<a href="https://patents.su/6-942020-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Многоуровневое микропрограммное устройство управления

Следующий патент: Устройство переменного приоритета

Случайный патент: Виброгасящее устройство