Микропроцессор для управления памятью микрокоманд

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 793153

Авторы: Белоус, Горовой, Красницкий, Кузьменко, Савотин, Сосновский, Хвощ, Шкроб

Текст

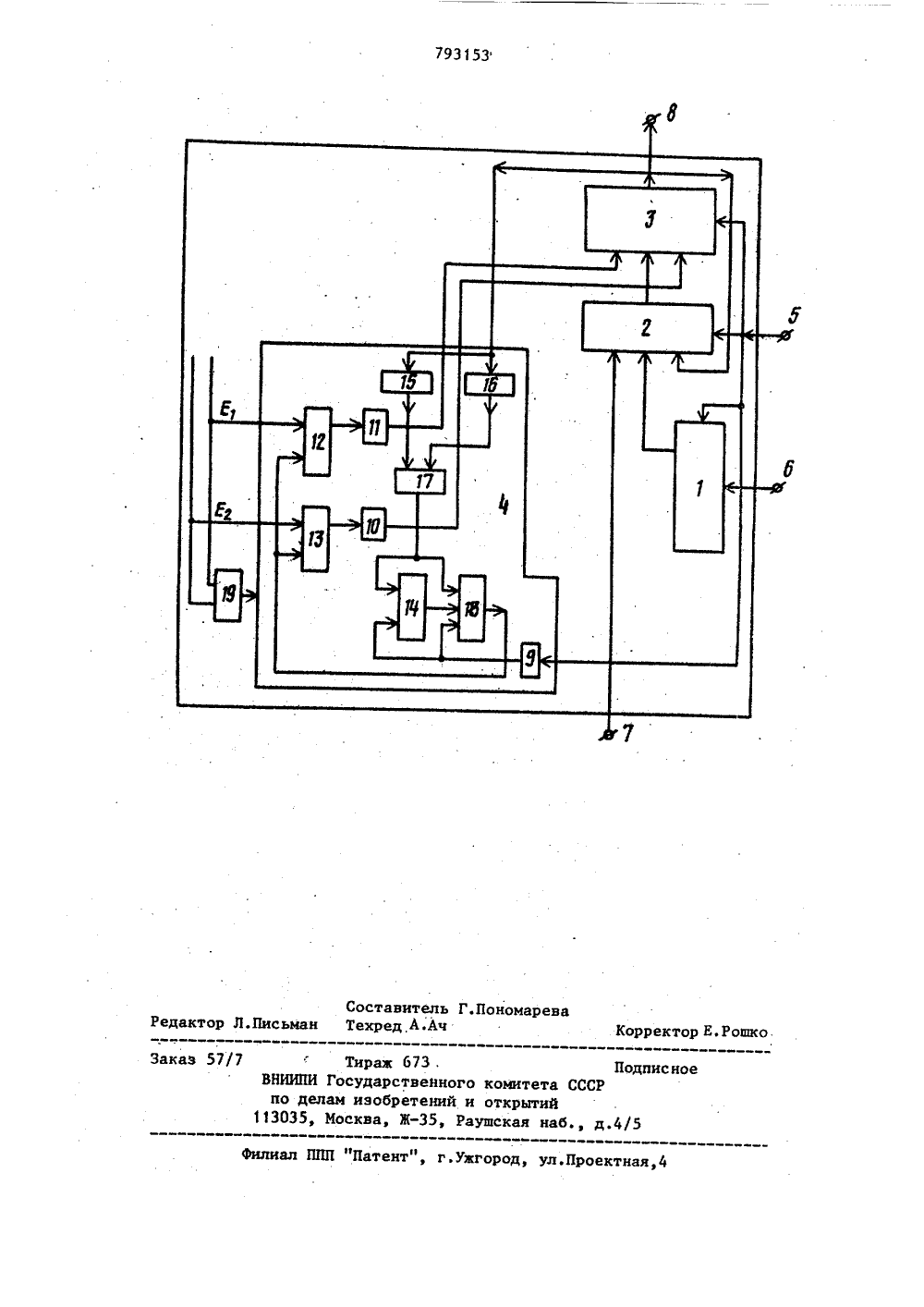

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН зо .79 з 1 ы.в)4 С 06 Г 9/06 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1иЙ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Микропроцессорный комплект БИСТТЛ с диодами Шотки Серии К 589,Справочные данные. М., 1977,Микропроцессор для управленияпамятью микрокоманд, техническоеописание, 1979.(54)(57) 1. МИКРОПРОЦЕССОР ДЛЯ УПРАВЛЕНИЯ ПАМЯТЬЮ МИКРОКОМАНД, содержащий регистр микрокоманд, информационный вход и выход которо" го соедиены соответственно с входом микрокоманд микропроцессора и первым входом блока формирования адреса, второй вход которого является синхровходом микропроцессора и соединен с тактовыми входами регистра микро- команд и регистра адреса микрокоманд, адресный вход которого соединен с выходом блока формирования адреса, третий вход которого является информационным входом микропроцессора, выход регистра адреса микрокоманд является выходом адреса микрокоманд микропроцессора и соединен с четвертым входом блока формирования адреса, о т л и ч а ю щ и йс я тем, что, с целью расширения функциональных воэможностей за счет обеспечения автоматической генерации адресов микропрограмм при включении или сбоях по питанию, в него введен блок контроля питания, гричем первый вход блока контроля питания соединен с синхровходом.микропроцессо" ра, второй вход блока контроля питания соединен с выходом регистра адреса микрокоманд, третий и четвертый входы блока контроля питания являются соответственно первым и вторым входом питания микропроцессора,первый и второй выходы блока контроля питания соединены соответственно с первым и вторым контрольными входами регистра адреса микрокоманд.2. Микропроцессор по п.1, о т л и. ч а ю щ и й с я тем, что блок контроля питания содержит два Й 8 -триггера, 3 -триггер,дешифраторы нуля и единицы, элементы И, ИЛИ, НЕ причем единичные входы первого и второго 05-триггеров соединены соответственно с третьим и четвертым входами блока, а нулевые входы - с выходом элемента И, первый вход которого соединен с синхровходом Ы -триггера и через первый элемент НЕ с первым входом блока, второй вход элемента И соединен с выходом 3 -триггера, информационный вход которого соединен с выходом элемента ИЛИ и с третьим входом элемента И, первый и второй входы элемента ИЛИ соединены соответственнр с выходами дешифратора нуля и дешифратора единицы, выходы которых соединены с вторым входом блока, выход первого Ю-триггера через второй элемент НЕ соединен с первым выходом блока, выход второго 08-триггера через третий элемент НЕ соединен со вторым выходом блока.Изобретение относится к области цифровой вычислительной техники, а именно к проектированию цифровых вычислительных машин на основе больших интегральных схем (БИС) микропроцессоров.Известны микропроцессорные наборные БИС, отличительной чертой которых является наличие микропрограммного устройства управления, предназначенные для конструирования цифровых вычислительных машин.Недостатками аналогов являются; невозможность образования начального адреса подготовительной программы, подготавливающей микро-ЭВМ к работе: невозможность отслеживания сбоев по пптанпо и принятию необходимых мер при их появлении.Наиболее близким по технической сущности к изобретению является микропроцессор для управления памятью микрокоманд, содержащий регистр микрокоманд (РМК), схему образования адреса (СОА), регистр адреса микро- команд (РАМК), шину адреса (ША), шипу входа (Ш ), шину микрокоманд (ШМК) и шину синхронизации (ШС),Иедостатком микропроцессора является невозможность выработки начального адреса подготовительной програм. мы, потому, что при включении питания регистр адреса микрокоманд может установиться в любое состояние и на шине адреса появится произвольный адрес, кроме того микропроцессор для управления памятью микропрограмм пе способен формировать признаки, отмечающие моменты кратковременного исчезновения питания.При использовании прототипа в сос. тане микро-ЭВМ для реализации указан. ных функций требуется использование дополнительного оборудования, что увеличивает аппаратурные затраты и снижает ее надежность. Цель изобретения - расширение функциональных возможностей микропроцессора за счет выработки начального адреса при включении питания, и выработки адреса микропрограммы при кратковременном сбое питания.Цель достигается тем, что в микро процессор для управления памятью микрокоманд, содержащий регистр микрокоманд, информационный вход и выход которого соединены соответственно с входом микрокоманд микропроцессора и первым входом блокаформирования адреса, второй входкоторого является синхровходом микропроцессора и соединен с тактовыми 5 входами регистра микрокоманд и регистра адреса микрокоманд, адресныйвход которого соединен с выходом бло.ка формирования адреса, третий входкоторого является информационным 10 входом микропроцессора, выход регистра адреса микрокоманд являетсявыходом адреса микрокоманд микропроцессора и соединен с четвертымвходом блока формирования адреса, 15 введен блок контроля питания, причем первый вход блока контроля питания соединен с синхровходом микропроцессора второй вход блока контроля питания соединен с выходом ре гистра адреса микрокоманд, третий ичетвертый входы блока контроля питания являются соответственно первыми вторым входом питания микропроцессора, первый и второй выходы блока 25 контроля питания соединены соответственно с первым и вторым контрольными входами регистра адреса микрокоманд.Кроме того, блок контроля питаниясодержит два 05 -триггера, З -триггер,дешифраторы нуля и единицы, элементы И, ИЛИ, НЕ, причем единичные входы первого и второго Ю -триггеровсоединены соответственно с третьими четвертым входами блока, а нулевыевходы - с выходом элемента И, первыйвход которого соединен с синхровходом З -триггера и через первый элемент НЕ с первым входом блока, второйвход элемента И соединен с выходомЭ-триггера, информационный вход которого соединен с выходом элементаИЛИ и с третьим входом элемента И,первый и второй входы элемента ИЛИ45соединены соответственно с. выходамидешифратора нуля и дешифратора единицы, входы которых соединены со вторым входом блока, выход первогоб-триггера через второй элемент НЕсоединен с первым выходом блока, вы.ход второго Ю -триггера через третий элемент НЕ соединен со вторымвыходом блока. 55, На чертеже приведена блок-схемамикропроцессора. Микропроцессор для управления памятью микрокоманд содержит регистр1 микрокомацд, блок 2 формирования адреса, регистр 3 адреса микрокоианд блок 4 контроля питания, вход 5 синхронизации устройства, вход 6 микрокомащ устройства, информационный вход 7 устройства, выход 8 адреса микрокоманд устройства. Блок 4 контроля питания содержит элементы НЕ 9-11, два 5 -триггера 12 и 13 д-триггер 14, дешифратор 15 нуля, дешифратоР 16 единицы, элемент ИЛИ 17, элемент И 18, элемент ИЛИ 19.Питание всех элементов, входящих в блок 4 контроля питания, осуществляется по логической Функции ИЛИ от входов питания Е и Г через элемент ИЛИ 19. Общие входы всех элементов, входящих в блок 4 контроля питания, подключены к земляной шине. Микропроцессор для управленияпамятью микрокомацд работает следующим образом.1. Нормальный режим. В каждоммикротакте в регистр микрокомацдподается новая микрокоцструкцият,блок 2 формирования адреса генерирует адрес микрокоманд ца основекода на информационном входе 7 микрокоманды в регистре микрокомацд 1и содержимого регистра 3 адресамикрокоманд. Образованный адреспереписывается в регистр 3 адресамикрокоманд и затем выдается по выходу 8 адреса микрокоманд из микропроцессора. Работа всего микропроцессора синхронизируется двумя синхросигцалами (СИ 1 и СИ 2) по входусинхронизации 5.2. Включение питанияМежду одним иэ входов питания и землянойшиной устанавливается конденсатор С,.При включении питания напряжение наодной шине будет задержано по отношению к напряжению ца другой шине.Через цепь 8-триггер 12, элементНЕ 19, регистр 3 адреса микрокомандбудет принудительно установлен вовсе единицы. На выходе 8 адреса микрокоманд формируется код 1 ЦП,Через дешифратор 16 единиц сигнална сброс 15 -триггера 12 пройдет через 3-триггер 14, элемент И 18 ибудет задержан на один такт. Следовательно, при полностью нормальном питании ца выходе адреса микрокоманд8 код 111 будет присутствоватьне менее двух микротактов, что достаточно для входа в подпрограмму на- чального сброса при включении питания.3. Режим сбоя питания. ПРИ кратковременном сбое питания ца внешнем конденсаторе по одной пз шин будет поддержано напряжение логической единицы ца время;ВН БИС (1 О Если перерыв по питанию больше ,,то блок контроля питания воспримет,его как начальное включенные. Внутреннее сопротивление БИС микропроцессора (Р , ) есть величина постоянН Бис 1ная и лежит в пределах единиц Ом.Следовательно, подбирая С, можноустанавливать порогвремеци, котороевоспринимается как время сбоя питания.Далее схема работает аналогичнорежиму включения с той разницей,что сигнал проходит через другой15 -триггер ц вызывает установку вноль регистра 3 адреса микрокомацд.Код на выходе 8 вырабатывается ввиде 000.Перестановка конденсатора С, цадругую шину питания автоматическименяет адреса микропрограмм сбоеви включения птания, следовательно,разработчик имеет возможностьпрограммировать зти адреса.Особенностью блока 4 контроляпитания является то, что все входящие в его состав элементы должныработать в случае наличия питающего 35напряжения хотя бы на одной из двухшин питания микропроцессора. Поэтомудля реализации блока 4 контроля пи- .тания необходимо использовать элементы, эапитанные по функции логического ИЛИ от шин питающего напряжения.При реализации микропроцессорана основе ИЛ технологии блок конт-,роля питания построен на основе элементов НЕ с двумя инжекторами. Этоэквивалентно питанию ее по логическому ИЛИ от шиц питающего напряжения.Таким образом, достоинствами микропроцессора для управления памятью50микрокоманд являются: автоматическая генерация адресов лшкропрограмм при включении или сбоях по питанию; отсутствие необходимости в дополнительном оборудовании и внешних выводах для контроля питания микро-ЭВМ;55программируемость адресов микропрограмм обработки сбоев и включенияпитания.793153 Корректор Е, Рошк Тираж 673 . П ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д.4Заказ 57/ одписное филиал ППП "Патент", г.ужгород, ул.Проектна Составитель Г.ПономареваРедактор Л.Письман Техред А.Ач

СмотретьЗаявка

2837047, 30.07.1979

ПРЕДПРИЯТИЕ ПЯ Р-6155, ОРГАНИЗАЦИЯ ПЯ Р-6007

СОСНОВСКИЙ Ю. Я, КРАСНИЦКИЙ Б. М, ХВОЩ С. Т, КУЗЬМЕНКО Н. Г, ГОРОВОЙ В. В, БЕЛОУС А. И, САВОТИН Ю. И, ШКРОБ В. С

МПК / Метки

МПК: G06F 9/06

Метки: микрокоманд, микропроцессор, памятью

Опубликовано: 23.01.1986

Код ссылки

<a href="https://patents.su/4-793153-mikroprocessor-dlya-upravleniya-pamyatyu-mikrokomand.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор для управления памятью микрокоманд</a>

Предыдущий патент: Лазер

Следующий патент: Устройство для проведения ремонтных работ внутри корпусов ядерных реакторов

Случайный патент: Фундамент под колонну