Преобразователь n-разрядного параллельного кода в последовательный и обратно

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

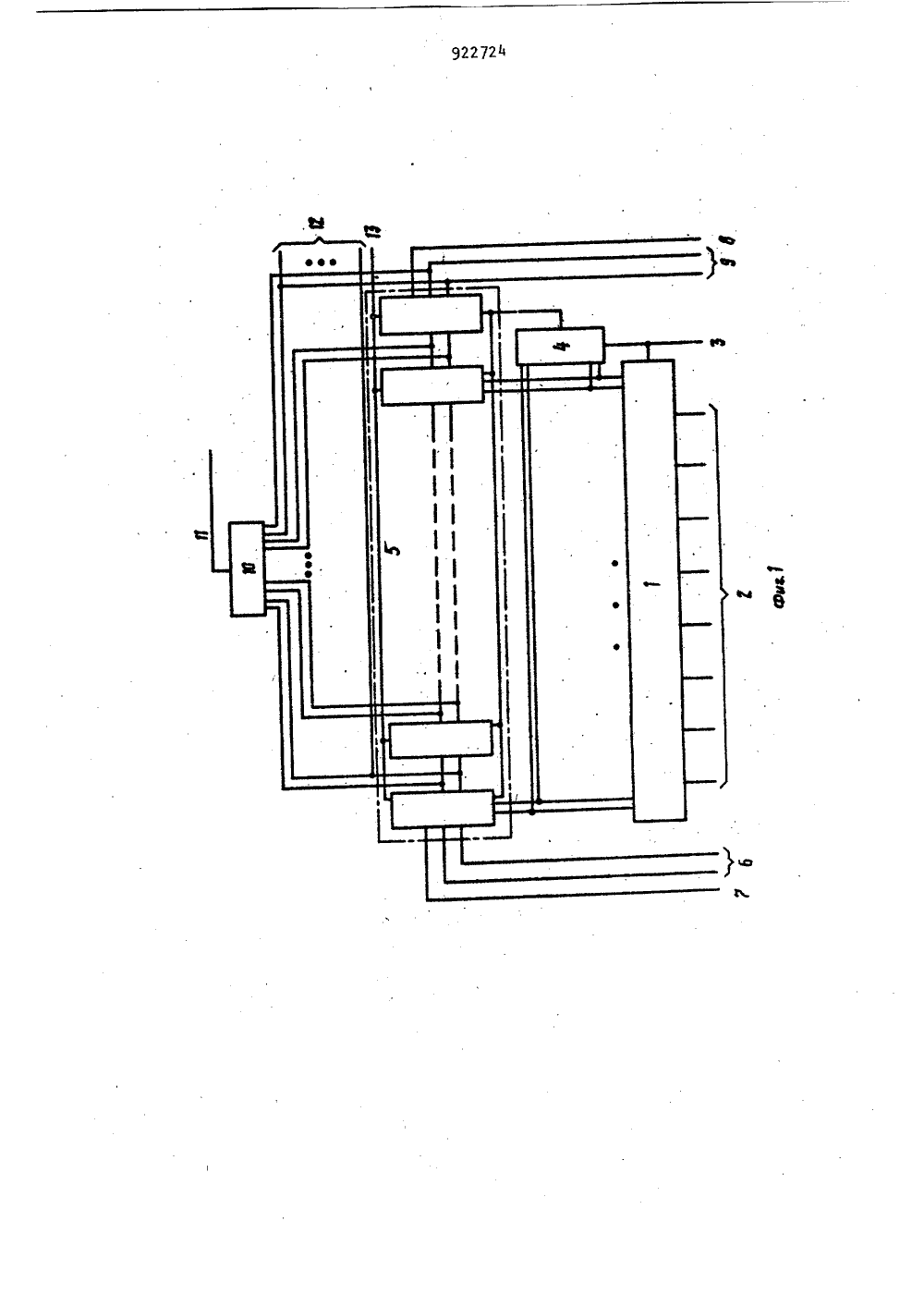

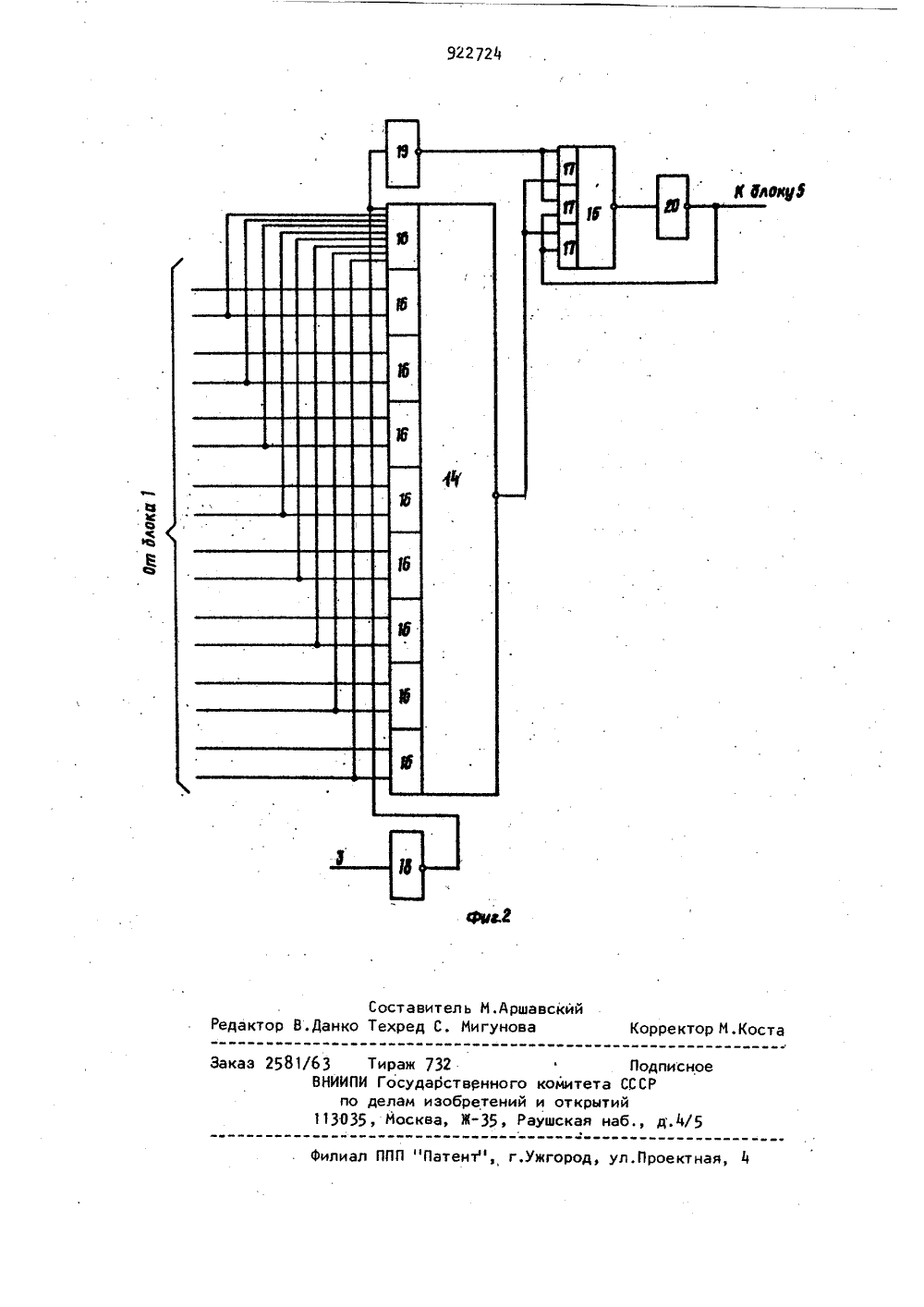

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 922724 Союз СоветскикСоциалистическикРеспублик(6 ) Дополнительное к авт. свид-ву(22)Заявлено 100979 (21) 2815714/18-24с присоединением заявки Рй -ав делам иэебретеиий и етерытий( 54 ) ПРЕОБРАЗОВАТЕЛЬ й"РАЗРЯДНОГОПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙИ ОБРАТНО 2 о преобразоватносительно низ евысокая достоотсутствием льсо Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано в устройствах обмена, хранения и преобразования информации. Известен преобразователь параллельного кода в последовательный и обратно, содержащий сдвигающий регистр; разделенный на тетрады, блоки коррекции, выходы которых подключены к входам сдвигающего регистра, блоки анализа, первые входы которых подключены к выходам сдвигающего регистра, и блок управления сдвигающим регистром, выход которого подключен к вторым входам блоков анализа 11.Недостаток известного преобразователя состоит в низкой достоверности преобразования, в отсутствии контро" ля преобразования, а также в низком быстродействии, являющимся следствием использования генератора тактовых имНаиболее близким к изобретению по технической сущности является преобразователь параллельного кода в последовательный и обратно, содержащий асинхронный сдвигающий регистр с 2 й разрядами, где Й-число разрядов преобразуемого кода, парафазные информационные входы и выходы последовательного кода которого являются соответ" ственно информационными входами и выходами последовательного кода преобразователя, а управляющие вход и выход асинхронного сдвигающего регистра являются соответственно управляющими входом и выходом преобразователя, вход сброса которого соединен с входом сброса асинхронного сдвигающего регистра с 21 . Недостатком даннотеля также являетсякое быстродействие иверность, связаннаяконтроля.3 9227Цель изобретения - увеличение быстродействия и повышение достоверностипреобразователя,Поставленная цель достигается тем,что в преобразователь М-разрядного5параллельного кода в последовательный и обратно, содержащий асинхронныйсдвигающий регистр с 2 М разрядами,где М - число разрядов преобразуемогокода, парафазные информационные входы ои выходы последовательного кода которого являются соответственно информационными входами и выходами последовательного кода преобразователя, ауправляющие вход и выход асинхронного сдвигающего регистра являются соответственно управляющими входом ивыходом преобразователя, вход сбросакоторого соединен с входом сбросаасинхронного сдвигающего регистра,введены блок элементов И-НЕ, блокуправления и блок контроля, входы которого соединены с парафазными инФормационными выходами асинхронногосдвигающего регистра, являющимисяинформационными параллельными выходами преобразователя, парафазные информационные входы четных разрядовасинхронного сдвигающего регистрасоединены с парафазными выходами блока элементов И-НЕ и с информационными входами блока управления, выходкоторого соединен с сигнальным входомасинхронного сдвигающегося регистра,выход блока контроля является управляющим выходом готовности преобразо 3вателя, управляющий вход запускапреобразователя соединен с управляю-.щими входами блока элементов И-НЕ иблока управления,40Кроме того, блок управления содержит первый и второй элементы ИЛИ-НЕпервую группу (М+1)-го .элемента И,выходы которых соединены с входамипервого элемента ИЛИ-НЕ, вторую груп 45пу из трех элементов И, выходы которых соединены с входами второго элемента ИЛИ-НЕ, и три инвертора, входыМ элементов И первой группы являютсяпарафазными информационными входамиблока управления, информационные вхо- Оды прямого кода блока управления соединены соответственно с М входами(М+1)-го элемента И первой группы,вход первого инвертора является управляющим входом. блока управления, а выход первого инвертора соединен с(М+1)-ым входом (М+1)-го элемента Ипервой группы и входом второго инвер 4тора, выход которого соединен с первыми входами первого и второго элементов И второй группы, выход второго элемента ИЛИ-НЕ через третий ин-вертор соединен с вторым входом второго и первым входом третьего элемента И второй группы, вторые входы первого и третьего элементов И второй группы соединены с выходом первого элемента,ИЛИ-НЕ, выход третьего инвертора является выходом блока управления.На фиг.1 представлена блок-схема управления предлагаемого преобразователя; на фиг,2 - блок-схема блока управления.Преобразователь содержит блок 1 элементов И-НЕ с М информационными входами 2 и управляющим входом 3 блок 4 управления с управляющим входом, подключенным к управляемому входу блока 1, асинхронный сдвигающий регистр 5 с парафазными информационным входом 6 в последовательномкоде, управляющим входом 7 асинхронного сдвигающего регистра 1, управляющим входом 8, парафазным информационным выходом 9 в последовательном коде, выходы блока 1 поразрядно подключены к входам блока 4 управления и установочными входами четных разрядов асинхронного сдвигающего регистра 5, сигнальные входы которых подключены .к выходу блока. 4 управления, блок 10 контроля, входы которого поразрядно подключены к информационным выходам параллельного кода регистра 5, а выход 11 блока 10 является выходом готовности преобразователя, информационные выходы асинхронного сдвигающего регистра 5 подключены к информационным параллельным выходам преобразователя, входы сброса асинхронного сдвигающего регистра 5 подключены к входу 13 сброса преобразователя.Блок 4 управления содержит первый и второй элементы ИЛИ-НЕ 14-15, первую группу 16 из (М+1)-го элементаИ, вторую группу 17 из- трех элементов И и три. инвертора 18-20, Блок контроля может быть выполнен из 6 М/8 элементов И-НЕ и И-ИЛИ-НЕ.Преобразователь работает следующимобразом;Блок 1 элементов И-НЕ закрыт уровнем логического нуля на управляющем входе 3, поступающим от управляющего выхода источника информации в паралЦ 6По заполнении асинхронного сдвигающе-, го регистра 5 на выходе 11 блока 10 устанавливается уровень логической единицы, подтверждающий появление информации в параллельном коде на информационных выходах 12. Достоверность преобразования информации подтвержда". ется уровнем логической единицы на выходе 11 блока 10. Установление единичного уровня на выходах 13 в ответ на уровень логической единицы на выходе 11 блока 10 подтверждает прием информации потребителем иразрешает сброс информации в регистре 5. После сброса информации на выходе 11 блока .10 устанавливается уровень логическа" го нуля, чем разрешается перевод сигнала на входах 13 на уровень, соответствующий лагическому нулю.Предлагаемое устройство позволяет осуществить преобразование цифровой информации из параллельного кода в последовательный и наоборот с выработкой сигнала о достоверности преобразования информации. При использовании преобразователей, на вырабатывающих такого сигнала, необходимо дублирование преобразователя с сравнением результатов. Кроме того, даже при дублировании с использованием схемы сравнения преобразователи и схема сравнения не выполняют своих функциональных задач при увеличении выше расчетного значения временных задержек логических элементов, на которых они построены.Применение предлагаемого преобразователя, построенного на асинхронном сдвигающем регистре, позволяет отказаться от дублирования и от схем сравнения, т.е. с помощью предлагае" мого устройства реалИзуется задача, для выполнения которой используется набор устройств, реализующих эту же задачу по частям. Кроме того, работоспособность преобразователя и высокая достоверность сохраняются при любых временных задержках логических элементов, на которых построено устройство, за счет введения схем управления, контроля и использования асин" хронного сдвигающего регистра. 45 Формула изобретения 1. Преобразователь й-разрядного параллельного кода в последовательный и обратно, содержащий асинхрон 5 . 92272лельном коде, При поступлении на управляющий вход 3 уровня логическойединицы блок 1 преобразует информацию,поступающую с информационных выходовисточника информации, в парафазныйкод. По окончании процесса преобразования на выходе блока ч управленияустанавливается уровень логическойединицы, который разрешает занесениепараллельной парафазной информации в щасинхронный сдвигающий регистр 5.После окончания занесения информациина выходе блока 10 устанавливаетсяуровень логической единицы. Уровеньлогической единицы на выходе 11 блока 1510 является признаком готовности выдачи последовательной информации иэасинхронного сдвигающего регистра 5на информационных выходах 9,Выдача информации в последовательном коде осуществляется следующимобразом.В начальный момент времени на информационных выходах 9 находятсяуровни логической единицы, а на управляющем входе 8 - уровень логического нуля. После занесения информации в асинхронный сдвигающий регистр5 и появления на выходе 11 блока 10уровня логической единицы инФормацияв регистре сдвигается, и на одном изинформационных выходов 9 появляется,уровень логического нуля. Это значит,цто очередной бит информации находится по выходах 9. Сигналом логической35единицы, подтверждающим прием битаинформации, разрешается сброс информации на выходах 9 и переход информационных выходов 9 в состояние, прикотором на обоих выходах находятся 4 Оуровни логической единицы, цто всвою очередь, разрешает перевод сигнала на управляющем входе 8 на уровень логического нуля Эта процедураповторяется й раз, По освобождениюрегистра 5 от информации после И-ойвыдачи на выходе 11 блока 10 устанав- .ливается уровень логицеского нуля,что является признаком конца передачи.ОПри обратном преобразовании инфор-мации иэ последовательного кода в параллельный информация в последовательном коде поступает на информационныевходы 6 асинхронного сдвигающего ре 55гистра 5. Управление приемом последовательной информации осуществляется с помощью управляющего выхода 7асинхронного сдвигающего регистра.7 9227ный сдвигающий регистр с 2 й разрядами,где М - число разрядов преобразуемогокода, парафазные информационные входыи выходы последовательного кода кото"-рого являются соответственно информационными -входами и выходами последовательного кода преобразователя, ауправляющие вход и выход асинхронногосдвигающего регистра являются соответственно управляющими входом и выходом 10преобразователя, вход сброса которогосоединен с входом сброса асинхронного сдвигающего регистра, о т л и ч аю щ и й с я тем, что, с целью повышения быстродействия и увеличения его 5достоверности, в него введены блокэлементов И-НЕ, блок управления иблок контроля, входы которого соединены с парафазными информационнымивыходами асинхронного сдвигающего 20регистра, являющимися информационными параллельными выходами преобразователя, входы четных разрядов асинхронного сдвигающего регистра соеди"нены с парафазными выходами блока 25элементов И-НЕ и с информационнымивходами блока управления, выход которого соединен с сигнальным входомасинхронного сдвигающего регистра,выход блока контроля является управ- золяющим выходом готовности преобразователя, вход запуска преобразователясоединен с управляющими входами блокаэлементов И-НЕ и блока управления.2. Преобразователь по п.1,о т л и- З 5ч а ю щ и й с я тем, что в нем блокуправления содержит первый и второй 24 8элементы ИЛИ-НЕ, пер вую группу из(К+1)-го элемента И, выходы которыхсоединены с входами первого элементаИЛИ-НЕ, вторую группу из трех элементов И, выходы которых соединены свходами второго элемента ИЛИ-НЕ, итри инвертора, входы М элементов Ипервой группы являются парафазнымиинформационными входами блока управления, информационные входы прямогокода блока управления соединены соответственно с входами (И+1)-го элемента И первой группы, вход первого ин-вертора является управляющим входомблока управления, а выход первогоинвертора соединен с (И+1)-ым входом(И+1)-го элемента И первой группы ивходом второго инвертора, выход которого соединен с первыми входами первого и второго элементов И второйгруппы, выход второго элемента ИЛИ-НЕчерез третий инвертор соединен с втрым входом второго и первым входомтретьего элемента И второй группы,вторые входы первого и третьего элементов И второй группы соединены свыходом первого элемента ИЛИ-НЕ, выход третьего инвертора является выходом блока управления,Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРИ 624226, кл. С 06 Г 5/02, 19752. Апериодические автоматыПодред. В,И.Варшавского. М ., "Наука",1975, с.309 (прототип),

СмотретьЗаявка

2815714, 10.09.1979

ПРЕДПРИЯТИЕ ПЯ А-3706

ПЕЛЕНОВИЧ ИГОРЬ ИВАНОВИЧ, СТАЛИН ЕВГЕНИЙ ГЕОРГИЕВИЧ, ЛОБАЧЕВ СЕРГЕЙ ЛЬВОВИЧ

МПК / Метки

МПК: G06F 5/04

Метки: n-разрядного, кода, обратно, параллельного, последовательный

Опубликовано: 23.04.1982

Код ссылки

<a href="https://patents.su/6-922724-preobrazovatel-n-razryadnogo-parallelnogo-koda-v-posledovatelnyjj-i-obratno.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь n-разрядного параллельного кода в последовательный и обратно</a>

Предыдущий патент: Преобразователь двоично-десятичного кода в двоичный

Следующий патент: Устройство поиска экстремального значения параметров

Случайный патент: Стенд для градуировки и поверки оптического измерителя скорости движения протяженного объекта