Устройство для вычисления показательно-степенной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

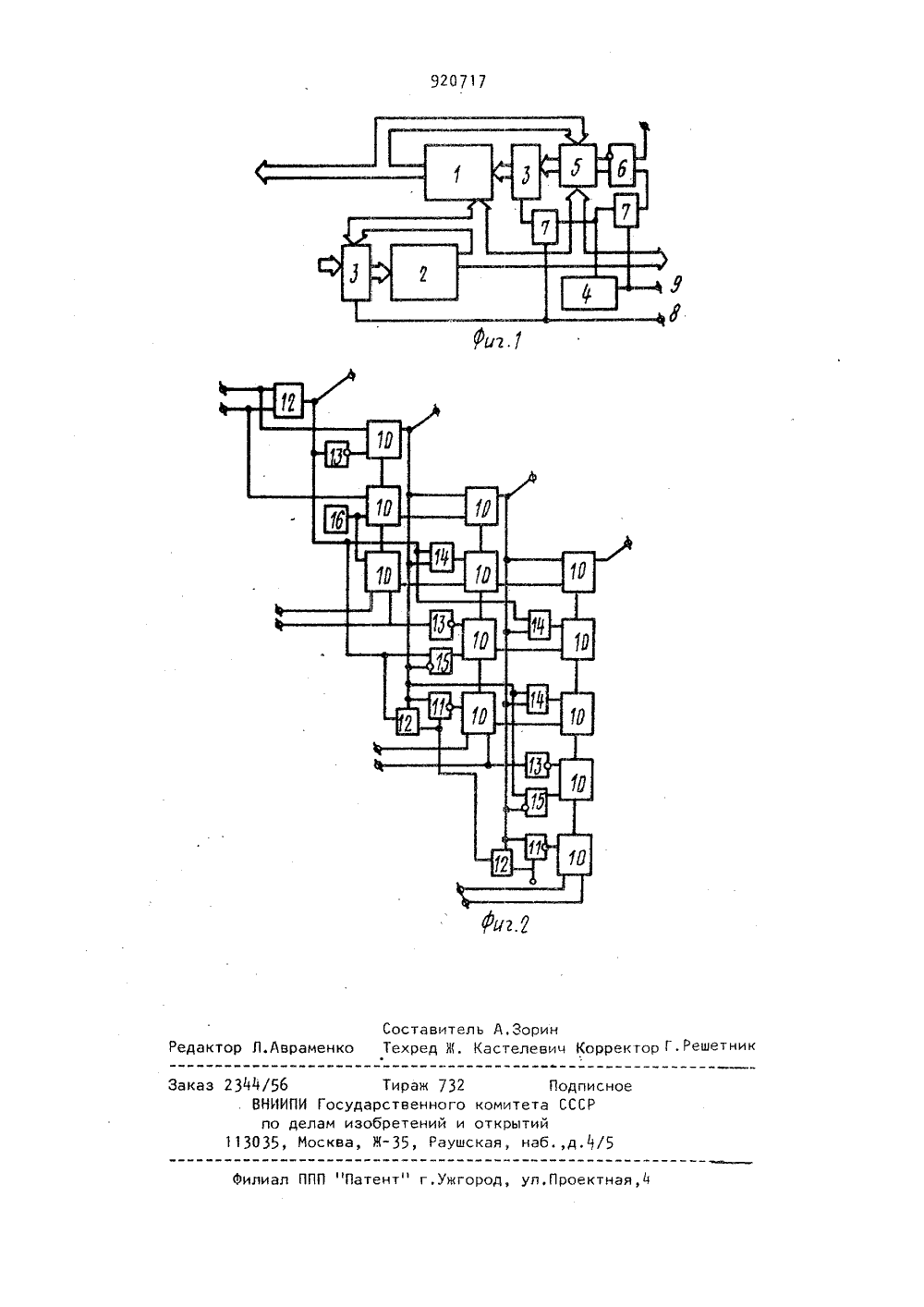

Союз СоветскикСоциалистическиеРеспублик ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 920717(5)М, Кд. О 06 Г 7/556 Ъеудерстеекый коиитвт СССР яо делаи изобретение и открытки(71) Заявитель Институт электродинамики АН Украинскои ССР(511) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПОКАЗАТЕЛЬНО- СТЕПЕННОЙ ФУНКЦИИ Изобретение относится к вычислительной технике и может быть применено в комплексе с цифровой вычислительной машиной или в спецпроцессорах для оперативного вычисления показательно-степенной Функции, например,в системах автоматического управления динамическими объектами.Известно устройство для возведения в дробную степень, содержащее блок па 10 мяти, блок возведения в дробную степень, блок извлечения корня, схемы сравнения, блоки ключей, цифро-аналоговый преобразователь, подключенный ко второму входу схемы сравнения,15 соединенной своим выходом с управляющим входом блока возведения в дробную степень 11.Недостатками известного устройства являются ограниченные функциональ ные возможности (так как число вос", производимых функций с дробными пока" зателлни ограничено), сложность изза наличия блока памяти и необходимости цифро-аналогового преобразования, а также относительно низкое быстродействие.Наиболее близким к предлагаемому по технической сущности является устройство, содержащее первый входной регистр, три блока умножения, два запоминающих блока, второй входной регистр, причем выход старших разрядов второго входного регистра соеди" нен со входом второго запоминающего блока, а выход младших разрядов " с первым входом второго блока умноже- . ния 123.Недостаток известного устройства " ограниченные функциональные возможности, так как в устройстве вычисляется только та функция= х ф, для которой в блоках памяти записано значение натурального логарифма старшихустразрядов хс , х , и т/х , низкая точность вычислений из-за применения приближенного алгоритма воспроизведения функции, а также сложность оп.92071ределяемая наличием двух блоков памяти и трех блоков умножения.Цель изобретения - увеличение точности, расширение Функциональных возможностей и упрощение устройства для вычисления показательно-степенной Функции.Указанная цель достигается тем, что в устройство для вычисления показательно-степенной Функции, содержа щее первый регистр, блок умножения и второй регистр, дополнительно введены сдвигающий регистр, блок извлечения корня, коммутатор, триггер и два элемента И, причем выход блока 5 извлечения корня соединен с первым выходом устройства и первыми входами блока умножения, коммутатора и первого регистра, подключенного выходом ко входу блока извлечения корня, вход 20 и выход второго регистра соединены соответственно с выходом коммутатора и вторым входом блока умножения, выход которого подключен к второму входу коммутатора, управляющие 2 Б входы которого соединены с прямым и инверсным выходами триггера, старший разряд регистра сдвига соединен с первыми входами первого и второго элементов И, выходы которых подключе. З 0 ны соответственно к управляющему входу второго регистра и первому входу триггера, второй вход которого является входом устройства управляющий вход первого регистра и второй вход первого элемента И соединены с первым управляющим входом устройства, второй управляющий вход которого подключен к второму входу второго элемента И и управляющему входу сдвиго вого регистра, выход блока умножения является вторым выходом устройства.При этом блок извлечения карня содержит (и) группу последовательно соединенных одноразрядных сумматоров ( и - разрядность аргумента), группу сумматоров по модулю два, группу элементов ИЛИ, группу элементов НЕ, (и) дополнительных группы по (и-1) (где 1 - номер 0 группы) сумматоров по модулю два в каждой группе, генератор единиц и группу из (и) элементов И, каждая 1-я группа(1 = 1,2,п"1) одноразрядных сумматоров выполнена из (и + у + 2 - 1) одноразрядных сумматоров, а группы элементов ИЛИ, элементов НЕ и сумматоров по модулю два соответ 7ственно из (и"1) и (и) элементов, причем выход каждого 1-го одноразрядного сумматора (1 + 1)-ой группы соединен с первым входом (1-1)-го одноразрядного сумматора 1-ой группы, второй вход первого одноразрядного сумматора 1"ой группы соединен с выходом переноса первого одноразрядного сумматора (1 + 1)-ой группы, первыми входами 1,-ых элементов И, элементов ИЛИ, сумматоров по модулю два групп и сумматоров по модулю два-ой дополнительной группы, выходы которых соединены с вторыми входами= х ( = 2, , и " 1) одноразрядных сумматоров 1-ой группы, вторые входы 1-ых (1 = 2 п-1) сумматоров по модулю два 1-ой дополнительинои группы соединены с выходами переноса первых одноразрядных сумматоров (и -) + 1)-ых групп, выход 1-го элемента НЕ группы подключен к первому входу (и + 1 - 1)-го одноразрядного сумматора 1-ой группы, второй вход которого соединен с выходом 1-го элемента И группы, подключенного своим вторым входом к выходу переноса первого одноразрядного сумматора ( 1-2)-ойгруппы, первый вход (п + 2 - )-го одноразрядного сумматора 1-й группы подключен к выходу 1-го сумматора по модулю два группы, подключенного своим вторым входом к выходу1-го элемента ИЛИ группы, второй входкоторого соединен с выходом (1+1)-го элемента ИЛИ группы, выход(и)-го элемента ИЛИ которой соединен с первым входом первого сумматора по модулю два каждой 1-ой дополнительной группы, входом (и)-го элемента НЕ группы и вторым входом (и) -го элемента ИЛИ группы, второй вход (и + 2 - 1) -го одноразрядного сумматора 1-ой группы соединен с входом (2 п - 21 + 1)-го разряда блока, (2 п - 21 + 2)-й разряд которого подключен к третьему входу одноразрядного сумматора и входу (1-1)-го элемента НЕ группы, входы первого ивторого разрядов блока подключены ко входам (и)-го элемента ИЛИ группы, к первым входам соответственно первого и второго одноразрядного сумматора (и)-й группы, вторые входы которыхсоединены соответственно с выходом (и"1)-го элемента НЕ группы и генератора единиц, подключенного к первому входу третьего одноразрядного сум5 9207 матора (п)-й группы, выходы переносов первых одноразрядных сумматоров и выход (и) -го элемента ИЛИ группы являются выходами блока, а вход каждого элемента И и выход каждого 1-го э сумматора по модулю два групп выполнены в виде инверсных.На фиг, 1 представлена блок-схема устройства; на фиг. 2 - блок извлечения корня. 1 ОУстройство содержит блок 1 умножения, блок 2 извлечения корня, регистры 3, сдвигающий регистр 4 коммутатор 5, триггер б, элементы И 7, управляющие входы 8 и 9, Блок 2 из" 1 Э влечения корня содержит одноразрядные сумматоры 10, сумматоры 11 по модулю два, элементы ИЛИ 12, элементы НЕ 13, сумматоры 14 по модулю два, элементы И 15 и генератор 1 б единиц. 20Работу устройства рассмотрим на примере вычисления покаэательно-степенной функции вида у = аф при а ) 0, -1 с х с 1, представленной в разрядной форме. 23"(1 1) 1 б, Ь б-С тФМ2 а 2 2 2 2 21 у1 0Де Х: Х Г,Х,а:С 1.,а СС 1 разрядные векторы, представляющиесобой разрядное изображение чиселх, а и у соответственно.В соответствии с выражением (1)чвектор у может быть представлен ввиде следующей зависимости 17 бч1,2,п искомого вектора г определяем по выражению- значение переноса иэстаршего разряда векто" ра Р 1 , определяемого на основании выраженияОч у))10) 1 где В" - величина, принимающая зна- чения а нектоЮ ч 111. иэвлекателя х = % осуществляетсяследующим образом. Старший разряд гискомого вектора г определяется наосновании зависимости=а ча .(4)Далее каждый последующий разряд 2 где 7:ХЛ 2, Ъ"=1 М,ВфМ,Вс 1Работа устройства для вычисленияпоказательно-степенной функции происходит следующим образом,В исходном состоянии в первом вход"ном регистре 3 записано а во второмрегистре 3 - нуль, в сдвигаючщем ре гистре 4 записано значение х, а триггер б находится в нулевом состоянии,5 ф эа счет чего первый вход коммутато"ра 5 подключен к выходу. Посколькуна вход блока извлечения корня 2 пос"тупает с выхода первого входного ре"чгистра 3 значение а, в блоке 2 проис"ЭЭ ходит переходной процесс, после окончания которого на выходе его по выражениям (4-7) образуется значение Ьпоступающее на первый выход и первыевходы коммутаторабг.1 ьи первого регистра 3, пале; - , вый управлющий вход устройсрза даЕТГя ИМПУЛЬС 11, ПОС уГ 1 сВщ 11 .1 а ПЕрвЫй ЗЛЕМРнт Й р И уяраВЛЛВ;ц;" -хор грерс ого регистра .Е.ли значение старшего ра".lВЕКТОРВ Х, ПОСтУПаЮЩЕЕ На Ггв элементов7 равно еди 1 ицс :,ХОДЕ ГЕРВОГО ЭЛЕМЕ - , с 1;4 -я сигнат х, которыи пост. управлярвщ 11 й вход второго рви по переднему ронту заплс "г . нега значение 1 а, поступа-с 1" коммута гор 5 на вход Втооог" 3. 1(роме того, сигналомему фронту записывает в пер 11" сои г, - и; -Р, ЗнаЧРЧ,.бгОке умнонрения 1 и бпо"я: 1 ",ОДИТ ПЕРЕХОДНОЙ ПРОЦЕСС а ;а ЗТ-,Рг. управляющий вход устр-йстеа =рЕМя ПОдаЕТСя СИГ 1-З 1 ": . ОТ(рц.с,Ог-.,- .,ЛЕМНсоонту станавлиБР=- -ичное состояние (которь,й нахс с, В этом состоянии в течение всего цикЛа РаООТЬ:) Зд СЧЕЗ ТОГО В 1 ОММУ,сп","эе 0 Вторси Вхор под . юч - .=/, : пс з. Днему фрор с ализует а сдвиговом ре-ист;е ИнфОРМаЦИИ ВЛЕВО На ОДИН РсЗЗРЯ. 10 С ле Окончания переходного г 1 ро.:.:с.:" .а арвом выхсре устройства ;бг; - ; ., ЗнасЕНИЕ "с а На ВТОРО:11 011-Г"ЕД "-рг .40гИЕ 1 С ",О ., ЕСЛИ ЗНаЕНИЕ - ,.О ряда х Вектора х ",.а.-.;-0Лрарвый входной регистп Сой рс.ГИГТр 3 СООВЕТС ВЕНН ЗРЧ"у 1 ррн 1 еЙ /6, после чего проце с рВто: ,;яется Ес и х = 1, го вр сггрзр ре;истре 3 останется предыдулая и 1 ворМа ЦИЯ, а ПССЛЕ ОКОН " с 1 НИЯ ПОСЛЕДУ;,1 Е ГО ПЕРЕХОДНОГО ПРОЦЕССВ Нс 1 ГЕР 301: ВЫ" .Оде образуется значение сЬргсле поступ пе ни я ( п" 1) пар си галг С, С,на втором выходе устВой. - Ва Выра 1 ению (2) образуется зн сниеурискомого вектора У. В зтом случае. когда в первом такте работь: знв.ениестаршего разряда х = р или к старших разрядов равно нулю, то при поступлении сигнала С ., реализуется запись :.с лько В первый регистр 3 до тех пор пока поср,е очередного сдвига ин 1100110- ЦИИ В С.,гВГВЮЩЕМ РЕГИСТРЕ Я ПС 01:Г"1налу 11 ; а выходе старлего разрядаЕГО Нг ПОЛВИтСЯ ЕДИНИЦа, ПОС 1.Е З;огО01 и 1110 ОИ -НI,;,- -Сойст.1:.:,:,.-1 Вычисления покаЗа 1-Л ЬНО-Г Г:ГЕННЙ 11 ,с 1 Ц 1 ИСОДЕрНра 1 е.- , ряр.й г, гиг т 1. бпск срноения и ВтОРОй Р.-ссСТР, ОЛ И Ч а Ю Щ Е Ег Я ТЕМ, Т , С 1 ГЬЮ ПОВЫШЕНИЯ ТОЧ 1 с НР - .ер-с в,.-.е;ень сдвигающий реГ .ЛОК ЗВ- С ИК 11 Я,СОММУ1 Р Р,; Гс 1 гГЕ 1, и, Г.а 3 Е 11 РНТа 1, ПРИ,е: зхо блока извлечения корня сое, ", 1 с рервьрм В,хгр.гтро,рстяс1 е:Выр 11 Входамк бргк-;1 11011 ения, коми-1) сумматоров по модулю два1-ой дополнительной группы соединеныс выходами переноса первых одноразрядных сумматоров(п- + )-ых групп,выход 1-го элемента НЕ группы подклю"чен к первому входу(М 1-1)-го одноразрядного сумматора 1-ой группы, вто"рой вход которого соединен с выходом1-го элемента И группы, подключенногосвоим вторым входом к выходу переноса первого одноразрядного сумматора;одноразрядного сумматора 1-ой группы подключен к выходу 1-го сумматорапо модулю два группы, подключенногосвоим вторым входом к выходу 1-гоэлемента ИЛИ группы, второй входкоторого соединен с выходом( + 1) -гоэлемента ИЛИ группы, выход(п)-гоэлемента ИЛИ которой соединен с первым входом первого сумматора по модулю два каждой 1-ой дополнительнойгруппы, входом (и)-го элемента НГгруппы и вторым входом (и)-го злемента ИЛИ группы, второй вход+ 2)-й разряд которого подключен ктретьему входу одноразрядного сумматора и входу (1-1) -го элемента НЕгруппы, входы первого и второго разрядов блока подключены к входам (и)-юэлемента ИЛИ группы, к первым входамсоответственно первого и второго од,норазрядного сумматоров (п) -й группы, вторые входы которых соединенысоответственно с выходом (и)-гоэлемента НЕ группц и генератора еди"ниц, подключенного к первому входутретьего одноразрядного сумматора(и)-го элемента ИЛИ группы являются выходами блока, а вход каждого элемента И и выход каждого-го сумматора по модулю деа групп выполнены ввиде инверсных. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРГ 59634 1, кл. С 06 Г 7/38, 978.2. Авторское свидетельство СССР575647, кл. С 06 Г 7/38, 1977(прототип) . 9 920717 1 Оченного выходом к входу блока извлечения корня, вход и выход второго регистра соединены соответственно с выходомкоммутатора и вторым входом блока умножения, выход которого подключен квторому входу коммутатора, управляю-.щие входы которого соединены с прямым иинверсным выходами триггера, старший разряд регистра сдвига соединен с первымивходами первого и второго элементов И,0выходы которых подключены соответственно к управляющему входу второго регистра и первому входу триггера, второй вход которого является входом устройства, управляющий вход первого ре гистра и второй вход первого элементаИ соединены с первым управляющим входом устройства, втоюй управляющийвход которого подключен к второму входу второго элемента И и управляющему 20входу сдвигового регистра, выход блока умножения является вторым выходомустройства.2., Устройство по п.1, о т л ич а ю щ е е с я тем, что блок изелечения корня содержит (и) группу последовательно соединенных одноразряднщхсумматоров(п - разрядность аргумента),группу сумматоров по модулю два,группу элементов ИЛИ, группу элементовНЕ, (и) дополнительных группы по(и -1-1) (где 1 - номер группы) сумматоров по модулю два в каждой группе, генератор единиц и группу из(и) элементов И, каждая 1-ая Группа ( = 1,2, и) одноразрядныхсумматоров выполнена из (и + 2 - )одноразрядных сумматоров, а группыэлементов ИЛИ, элементов НЕ и сумматоров по модулю два соответственноиз (п) и (и) элементов, причемвыход каждого 1-го одноразрядного сумматора ( + 1)-ой группы соединен спервым входом (1-1) -го одноразрядного сумматора 1-ой группы, второй входпервого одноразрядного сумматора -ойгруппы соединен с выходом переносапервого одноразрядного сумматора( + 1)-ой группы, первыми входами1-х элементов И, элементов ИЛИ, сумматоров по модулю два групп и сумматоров по модулю два 1-ой дополнитель"ной группы, выходы которых соединены с920717 Составитель А.Зоринвраменко Техред И. Кастелевич Корректор Г.Решетник Редакто д, ул,Проектная,Филиал ППП "Пг.ужго каз 23 М/56 Тираж 732 ВНИИПИ Государственного по делам изобретений и 113035, Москва, 8-35, Раущ Подписнкомитета СССРоткрытийкая, наб.,д,/5

СмотретьЗаявка

2972144, 28.05.1980

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УССР

КУЛИК МИХАИЛ НИКОЛАЕВИЧ, СТАСЮК АЛЕКСАНДР ИОНОВИЧ, ЛИСНИК ФЕДОР ЕРЕМЕЕВИЧ, МАЗУРЧУК ВИКТОР СЕМЕНОВИЧ, БЕЛЕЦКИЙ ВЛАДИМИР НИКОЛАЕВИЧ, РЫБЧЕНКО ВЛАДИМИР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, показательно-степенной, функции

Опубликовано: 15.04.1982

Код ссылки

<a href="https://patents.su/6-920717-ustrojjstvo-dlya-vychisleniya-pokazatelno-stepennojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления показательно-степенной функции</a>

Предыдущий патент: Устройство для вычисления элементарных функций

Следующий патент: Генератор псевдослучайных кодов

Случайный патент: Устройство для транспортировки велосипедов