Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 742937

Автор: Соколов

Текст

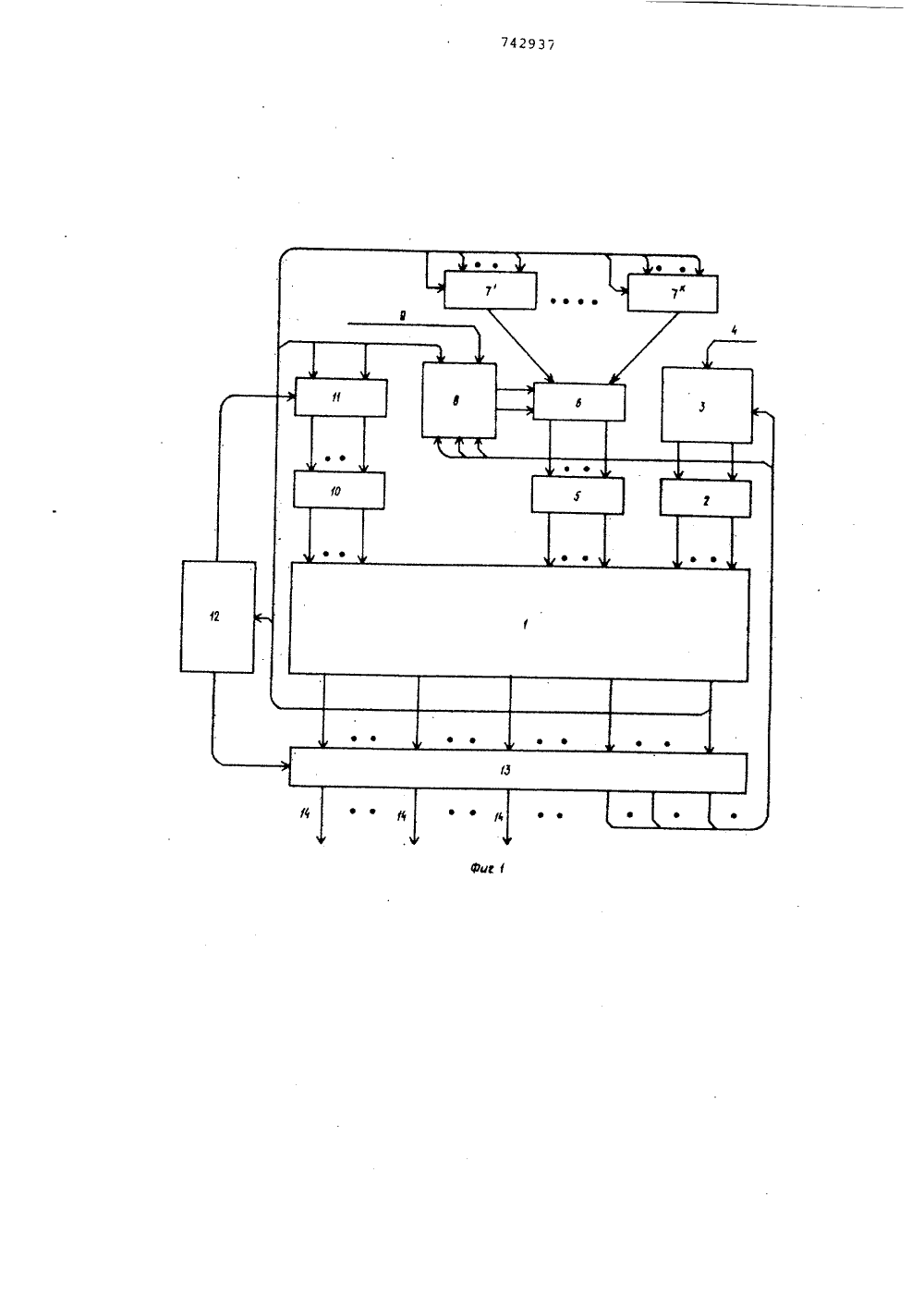

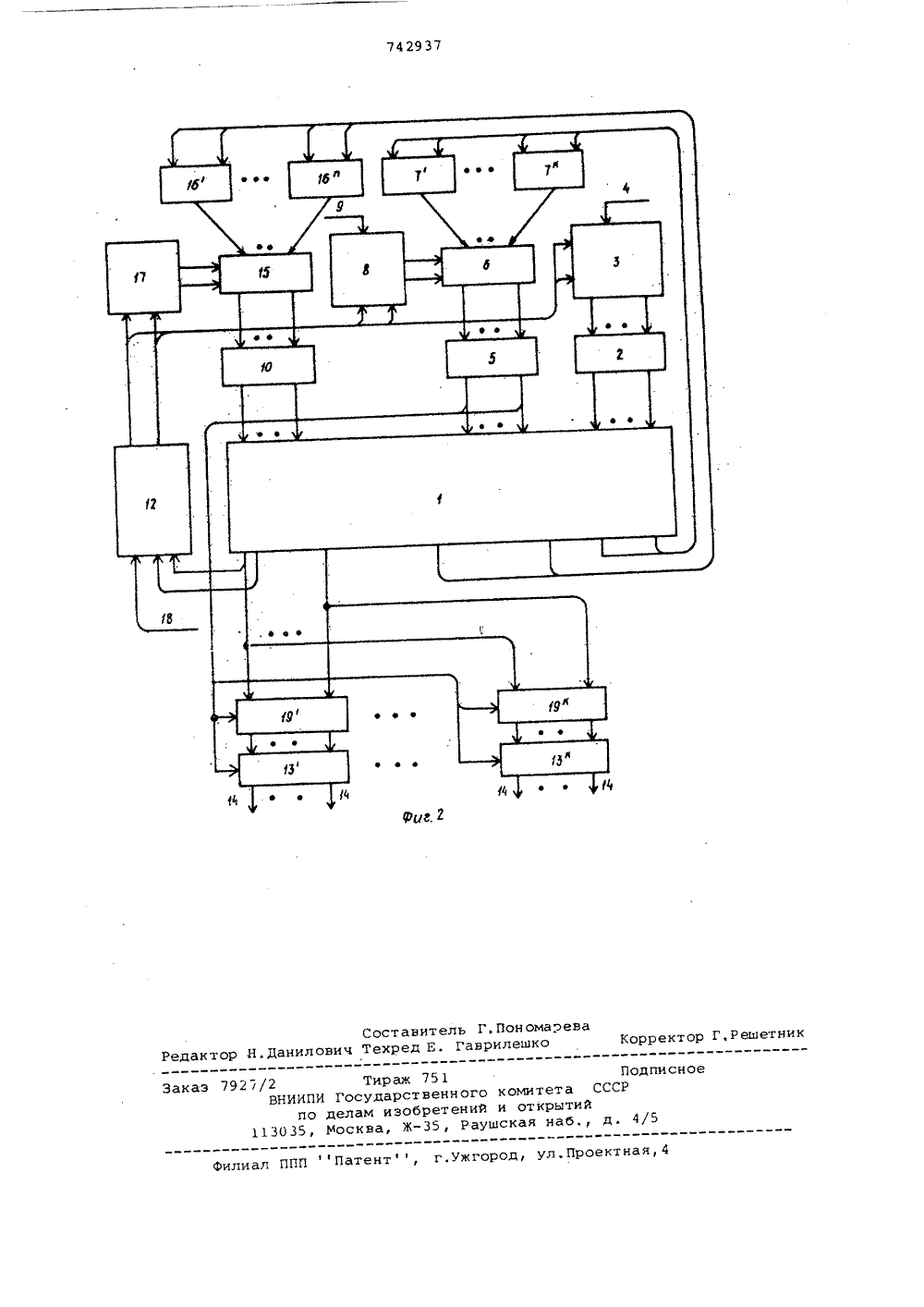

Союз Советских Социалистических Республик(51)М. Кл.2 С 06 Р 9/14 Государственный комитет СССР по делам изобретений н открытий(54) МИКРОПРОГРАММНОЕ УСТРОИСХВО УПРАВЛЕНИЯ Изобретение относится к вычисли-,тельной технике и может быть использовано в устройствах управления раз-","личного рода радиотехническими системами, в частности, для управления 5выполнением операции в ЦВМ,Известно микропрограммное устрой"ство управления, содержашее регистркоманд, дешифратор операций, счетчик адреса микрокоманд, дешифратор 1 Оадреса микрокоманд, блок памяти микрокоманд, генератор импульсов, узелпуска-останова, блок памяти команд,регистр управляющих сигналов, регистры адреса микрокоманд безусловногоперехода, дешифратор безусловных переходов, регистр позиционных адресов безусловных переходов, коммутатор 1) .недостатком известного устройства является низкая надежность устройства в работе,Наиболее близким к предлагаемомупо технической сущности и достигаемому результату является микропрограммное устройство управления (23,содержашее блок памяти, первые входы которого связана через дешифратор адреса операций и блок Формирования адреса операции 3 со входом 4 микропрограммного устройства управления. Вторые входы блока памяти 1 подключены через дешифратор адреса фаз операции 5 и коммутатор адресов фаз операции 6 к выходам К - регистров адреса фазы 7, где К: - максимальное количество Фаз (этапов) при выполнении операции, входы которых подключены к выходам блока памяти 1, Управляюшие входы коммутатора адреса фаэ операции б связаны с выходами дешифратора блока управления коммутатором адресов Фаз операции 8, (блок 8 выполнен на счетчике, подключенном ко входам дешифратора), подключенного ко второму входу 9 микропрограммного устройства управления. Третьи входы блока памяти 1 связаны через дешифратор адреса микрокоманд 10 с выходами счетчика адреса микрокоманд 11, подключенного к узлу пуска-останова 12, Выходы блока памяти 1 связаны через регистр микрокоманд 13 с выходами 14 микропрограммного устройства управления,Известное устройство имеет низкую надежность иэ-за того, что длина слова, выбираемого нэ накопителя, имеет большую разрядность, достигаюшую 100-200 разрядов.Целью изобретения является повьпаение надежности работы микропрограммного устройства управления,Поставленная цель достигается тем, что н микропрограммное устройстно упранления, содержащее блок памяти, парвая группа входов которого соединена через дешифратор адреса операции с группой выходов блока формирования адреса операции, вход признаков которого является первым входом устройства, а управляющая группа входон блока управления коммутатором адресбв Фазы операции, вход которого является вторым входом устройства, а группа выходов блока управления коммутатором адресов Фазы операции соединена с группой входов управления кОммутатора адресов фазы операции, вторая группа входов которого соединена с выходами регистров адреса Фазы, а группа выходов - с группой входов дешифратора адресов Фазы операции, группа выходов которого сОединена со второй группой входов блока памяти, третья группа входон которого соединена с группой выходбн дешифратора адреса микрокоманды, первая группа выходов блока памяти соединена с группами входов регистров адреса Фазы, вторая группа выходов - с первой группой входов узла пуска-останова, и регистр микрокоманд, группа выходов которого является группой выходов устройства, введены коммутатор адресов микрокоманд, блок управления коммутатором адресов микрокоманд, регистры адресов микрокоманд, группы элементов И, причем первая группа входов коммутатора адресов микрокаманд соединена с выходами регистров адресов микрокоманд, группа входов упранления коммутатора адресов микро- команд - с группой выходов блока управления коммутатором адресов микрокоманд, а группа выходов коммутатора адресов микрокомандс группой нходаа дешифратора адреса микрокоманд, группа входов всех регистров адресов микрокоманд соединены с третьей группой выходов блока памяти, группа выходов узла пуска-оста- нова соединена с группой входов блока управления коммутатором адресов микрокоманд и с первой группой входов блока управления коммутатором адресов микрокоманд и с первой группой входов блока управления коммутатором адресов фазы операции, а второй вход является третьим входам устройства, вторая группа выходон блока памяти подключена к соотьетствующим входам элементов И всех групп, входы упранления которых соединены С соответствующими выходами дешифратора адресов фаз операции и с входами управления регистров микрокоманд, группа входов которых сое ции 3 со входом 4 микропрограмного устройства управления, Вторые входы блока памяти 1 подклюпамяти 1 Цепи управления коммутатора б связаны с выходами дешифратора блока управления коммутатором адресов Фаз операции 8, (блок 8 выполнен на счетчике, подключенном ко входам дешифратора), подключенного ко второму входу 9 микропрограммного устрййства, Третьи входы блока памяти 1 подключены к выходам дешифратора адреса микрокоманд 10, Узел пускаостанова 12, подключенный к выходам блока памяти 1, связано с блоками управления коммутатором адресов Фаз операции 8 и блоком Формирования адреса операции 3, Выходы регистра микрокоманд 13 подключены к выходам 14 микропрограммного устройства управления, Входы дешифратора адреса микрокоманд 10 связаны через коммутатор адресов микрокоманд 15 с выходами п регистров адреса микрокоманд 16, где и - максимальное количество микрокоманд в фазе выполняемой операции, входы которых подключены ко вторым выходам блока памяти 1, Цепи управления коммутатора 15 связаны с выходами дешифратора блока управления коммутатором адресов микрокоманд 17 (блок 17 выполнен на счетчике, подключенном ко входам дешифратора), подключенного к узлу пуска-останова 12, связанного с третьим входом 18 микропрограммного устройства управления, Третьи выходы блока памяти 1 подключены параллельно к.о входам К групп элементов И 19, связанных с соответствующими группами триггеров регистра микрокоманд 13, Цепи управления групп элементОв И 19 и триггеров регистра микрокоманд 13 подключены к 15 20 25 ЗО 35 40 45 50 55 60 динена с группой выходов элементов И соответствующей группы,Сущность изобретения поясняется чертежами, где:на фиг,1 - предстанлена блок-схема известного микропрограммного устройства управления;на Фиг,2 - представлена блок-схема данного микропрограмкого устройства управления,Микропрограммное устройство управления (фиг,2) содержит: блок памяти 1, первые нходы которого связаны через дешифратор адреса операций 2 и блок формирования адреса операчены через дешифратор адреса Фазопераций 5 и коммутатор адресовфаз операции б к выходам К - регистров адреса фазы 7, где К - максимальное количество фаз (этапов)при выполнении операции, входы которых подключены к первым выходам блокасоответствующим выводам дешифратораадресов фаз 5,Микропрограммное устройство управления (фиг.2) работает следующим образом.В последней микрокоманде последней фазы выполняемой операции на вход 4 в блок 3 поступают необходимые признаки из блоков ЦВМ, и в нем формируется код следующей операции, который затем поступает через дешифратор адреса операций 2 на перные входы блока памяти 1 и обеспечиваетвыбор иэ него начальных адресов всех 0 Фаэ, необходимых для использования в этой операции, Эти начальные адреса фаэ переписываются из блока памя 15 ти 1 в регистры адреса фазы 7, прн этом выход регистра адреса первой Фазы 7 сразу же подключается ко вторым входам блока памяти 1 через дешифратор адреса фазы операции 5 и ком- ф мутатор адресов фаз операции 6 блоком управления коммутатора адресов 8, что обеспечивает выбор из блока памяти 1 всех адресов микрокоманд дяя первой фазы операции, которые 25 переписываютс я вире ги с тров адреса микрокоманд 1 б,причем выход регистра адреса первой микрокоманды 161 первой Фазы сразу же подключается к третьим входам блока памяти 1 Зр через дешифратор адреса микрокоманд 10 и коммутатор адресов микрокоманд 15 блоком управления коммутатором адреса микрокоманд 17, что обеспечивает прохождение новой микрокоманды на Выход устройства. Далее, отключается нход 4 от блока 3 и подключается узел пуска-останона 12, При этом на вход счетчика и блоке 17 подаются импульсы, что обеспечивает последовательное подключение выходов регистрон адресов микрокоманд 16 - 16и ко входам дешифратора адреса микро- команд 10, а значит и последонательную выборку из блока памяти 1 всех микрокоманд для 1-й фазы данной опе рации, которые проходят только через первую группу элементов И 19 и первую группу триггеров 13 регистра микрокоманд 13 на выходы 14 микропрограммного устройства управления,под ключаемые коммутатором 5, Следует заметить, что так как в каждой фазе операции используются только вполне определенные управляющие сигналы, например, сигналы, необходимые для Формирования адреса команды, адреса операнда, сигналы, необходимые для осуществления выполнения действий над операндами, и т.д поэтому длина слова, выбираемого иэ блока памяти, может быть .существенно уменьше на, а в идеальном случае она можетбыть уменьшена в К раэ, В последней микрокоманде 1-й фазы счетчик блока 17 обнуляется, а счетчик блока 8 подключает выходы регистра адреса 2-й фазы 7 через коммутатор адресов Фаз операции б и дешифратор адресов фаэ операции 5 ко вторым входамблока памяти 1, что обеспечивает выбор из блока памяти 1 всех адресовмикрокоманд для второй фазыоперацийкоторые переписываются в и регистров адреса микрокоманд 16, причем выход регистра адреса первой микрокоманды 16 второй Фазы сразу жеподключается.к третьим входам блокапамяти 1 через дешифратор адресамикрокоманд 10 и коммутатор адресовмикрокоманд 15 блоков управления коммутатором адресов микрокоманд 17,чтообеспечивает выборку и прохождениепервой микрокоманды второй фазы операции на выход 14 микропрограммногоустройства упранления, но уже черезвторую группу элементов И 192которая подключается дешифратором адресов Фаз 5 на время выборки всех микрокоманд для второй Фазы операции,Далее, на вход счетчика блока 17 подаются импульсы, что обеспечивает последовательное подключение выходоврегистров адресов микрокоманд 1616 ко входам дешифратора адреса микрокоманд 10 и т.д.В последней микрокоманде последней фазы выполняемой операции на вход4 н блок 3 поступают необходимые признаки для следующей операции иэ блоков ЦВМ, и в нем формируется код следующей операции, после чего цикл работы повторяется,В данное микропрограммное устройство управления дополнительно введены группы элементов И, коммутаторадресов микрокоманд, регистры адресонмикрокоманд, блок управления коммутатором адресов микрокоманд и ряд ноных связей, что позволило повыситьнадежность микропрограммного устройства управления за счет:- подключения только 1 к частивыходов микрокоманд, используемых ввыполняемой фазе операции, так какпри этом исключаются сющбки от нерабочей, большей части микрокоманде;- отключения выходов большей части микрокоманд, не используемых в выполняемой фазе операции, т.е. отключения (К) групп выходов, с исключением ошибок работы соответствующихгрупп элементов И и триггеров регистра микрокоманд;- сокрашения длины слов, записываемых в блок памяти, примерно в Краэ, так как при этом сокращаетсяколичество элементов и связей в блокепамяти,Формула изобретенияМикропрограммное устройство управления содержащее блок памяти, перная. группа нходон которого соединена че 742937реэ дешифратор адреса операций с группой выходов блока формирования адреса операции, вход признаков которого является первым входом устройсгва, а управляюшая группа входов соединена с первой группой входов блока управления коммутатором адресов фазы операции, вход которого является вторым входом устройства,а группа выходов блока управления коммутатором адресов Фазы операции соединена с группой входов управления коммутатора адресов Фазы операции, вторая группа входов которого соединена с выходами регистров адреса фазы, а группа выходов - с группой входов дешифратора адресов фазы операции, группа вы ходов которого соединена со второй груцпой входов блока памяти, третья группа входов которого соединена с группой выходов дешифратора адреса микрокоманды, первая группа выходов Щ блока памяти соединена с групгами входов регистров адреса фазы, вторая группа выходов - с первой группой входов узла пуска-останова, и регистр микрокоманд, группа выходов которого является группой выходов устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены коммутатор адресов микрокоманд, блок управления коммутатором адресов микрокоманд, регистры адресов микрокоманд, группы . элементов И, причем группа входов коммутатора адресов микрокоманд соединена с выходами регистров адресовмикрокоманд, группа входов управления коммутатора адресов микрокомандс группой выходов блока управлениякоммутатором адресов микрокоманд, агруппа выходов коммутатора адресовмикрокоманд - с группой входов дешифратора адреса микрокоманд, группавходов всех регистров адресов микрокоманд соединена с третьей группойвыходов блока памяти, группа выходовузла пуска-останова соединена с группой входов блока управления коммутатором адресов микрокоманд и с первойгруппой входов блока управления коммутатором адресов фазы операции, авторой вход является третьим входомустройства, вторая группа выходовблока памяти подключена к соответствуюшим входам элементов И всех групп,входы управления которых соединены ссоответствующими выходами дешифратора адресов Фаэ операции и с входамиуправления регистров микрокоманд,группа входов которых соединена сгруппой выходов элементов И соответствуюшей группы,Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССРР 492874 кл, С 06 Р 9/14, 1974 г,2, Заявка Р 2317818/24,кл, С Об Г 9/14, 1976 г( по которойпринято положительное решение о выдаче авторского свидетельства (прототип), 742937

СмотретьЗаявка

2610690, 04.05.1978

ПРЕДПРИЯТИЕ ПЯ А-7162

СОКОЛОВ ИГОРЬ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 9/14

Метки: микропрограммное

Опубликовано: 25.06.1980

Код ссылки

<a href="https://patents.su/6-742937-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Оптоэлектронный сумматор

Следующий патент: Устройство приоритета

Случайный патент: Комбинированный рабочий орган