Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

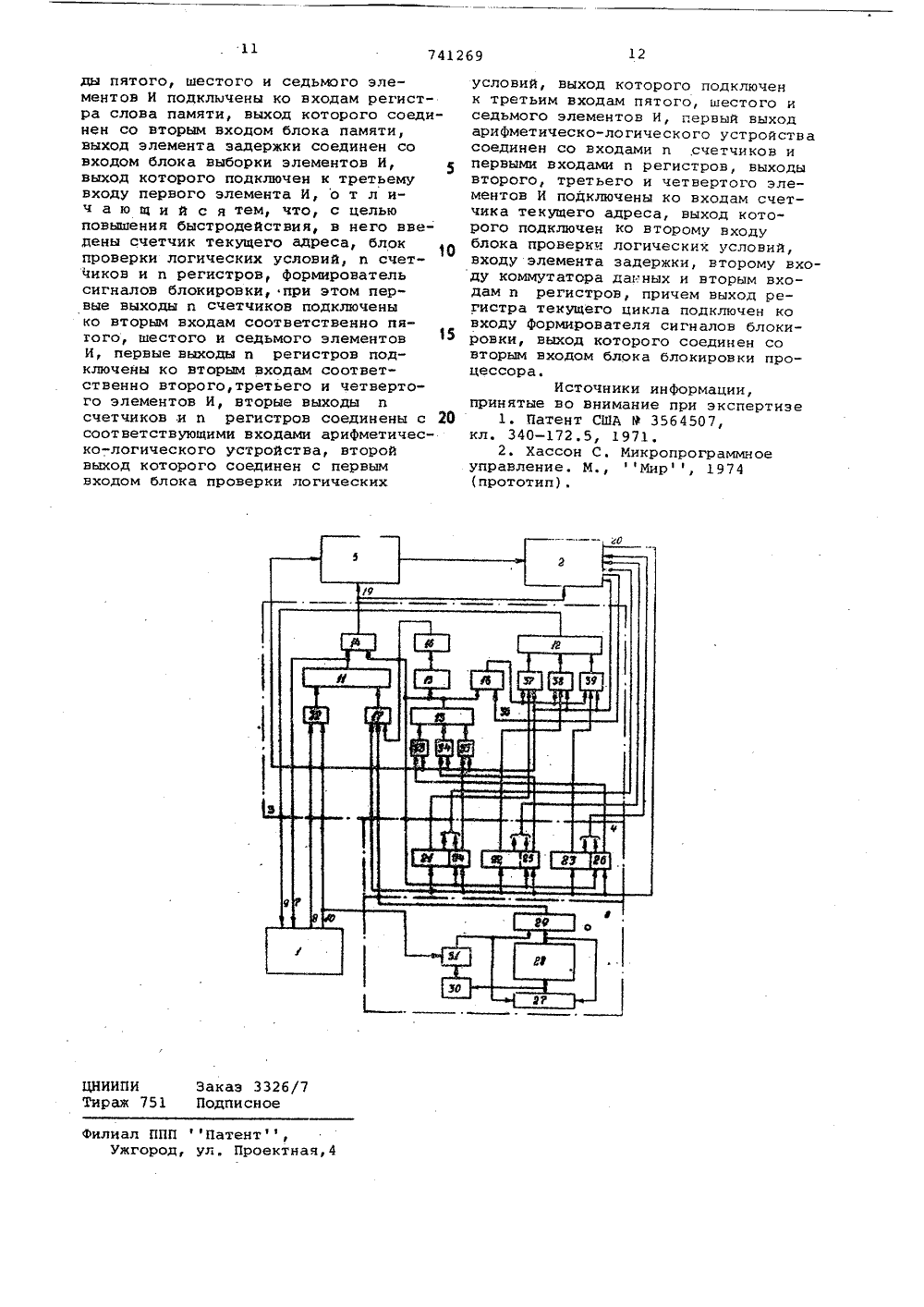

Оп ИСАНИЕ ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республик(22) Заявлено 043178 (21) 2566799/18-24 (51) М. КЛ,с присоединением заявки Йо(23) Приоритет 0 06 Р 15/00 Государственный комитет СССР по делам изобретений н открытий(71) Заявитель Специальное конструкторское бюро вычислительныхмашин(54 ) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР Изобретение относится к вычислительной технике и может быть использовано в ЦВМ.Известно устройство, осуществляющее асинхронную связь между более медленной оперативной памятью и более быстродействующим процессором (11Недостатком данного устройства является то, что после обращения прОцесса к оперативной памяти егодействие блокируется на время, равное времени выборки данных из памяти, т.е. одновременная параллельная раббта Оперативной памяти и процессора возможна только во второй половине цикла оперативной памяти.Наиболее близким по технической сущности является микропрограммный процессор, содержащий оперативную память, местную память, схему для выполнения арифметических операций, аппаратуру для формирования адресов, аппаратуру для обмена данными и блок микропрограммного управления, В данном процессоре для увеличения быстродействия также организована асинхронная работа оперативной памяти и процессора 2,. Недостатком данного процессора,является также блокирование его работы на время, равное времени выборки данных из памяти.Цель изобретения - увеличениебыстродействия процессора.Эта цель достигается тем, что впроцессор, содержащий буферную р память, арифметическо-логическоеустройство, регистр слова памяти,регистр данных, коммутатор данных,блок выборки элементов И, элементзадержки, блок памяти, память микропрограмм, дешиФратор ьщкрокоманд;регистр текущего цикла, блок блокировки процессора, восемь элементов И,причем вход-выход арифметическо-логического устройства соединен свыходом-входом буферной памяти, выходдешифратора микрокоманд соединен спервыми входами первого, второго,третьего, четвертого, пятого шестого, седьмого элементов И, первымвходом буферной памяти и первым входом арифметическо-логическогоустройства, первый выход блока памятисоединен с первым входом восьмогоэлемента И, выход которого подключенк первому входу регистра данных,выход которого соединен с первым вхо дом блока памяти и первым входам коммутатора данных, выход каторога .подключен ко второму входу буферной памяти и второму входу арифметическо-логическога устройства, второй выход блока памяти соединен со вторым входом восьмого элемента И и первым входом блока блокировки процессора, выход которого подключен к первому входу дешифратора микрокоманд и первому входу регистра текущего цикла, выход которого соединен со входом памяти микропрограмм, выход которой соединен со вторым входом дешифратора микрокоманд и вторым входом регистра текущего цикла, первый выход арифметическо-логического устройства соединен са вторым входом первого элемента И, выход которого подключен ко второму входу регистра данных, выходы пятого, шестого и седьмого элементов И подключены ка входам регистра слова памяти, выход которого соединен са Вторым входом блока памяти, выход элемента задержки соединен со входом блока выборки элементов И, выход которого подключен к третьему входу первого элемента И, введены счетчик текущего .адреса блок проверки логических условий, п счетчиков и и регистров, Формирователь сигналов блокировки при этом первые выходы и счетчиков подключены ко вторым входам соответственна пятого, шестого и седьмого элементов И, первые выходы и регистров подключены ка вторым входам соответственно второго, т 1.етьега и четвертого элементов И, вторые выходы и счетчиков и г. регистров соединены с соответствующими входами арифметическо-логического устройства, второй выход которого соединен с первым входом блока проверки логических условий, выход которого подключен к третьим входам пятого, шестого и седьмого элементов И, первый выход арифметическо-логическога устройства соединен со входами п счетчиков и первымн входами п регистров, выходывторого, третьего и четвертого элементов И подключены ко входам счетчика текущего адреса, выход которого подключен а второму входу блока проверки логических условий, входуэлемента задержки, второму входу коммутатора данных и втормет входам .п регистров, причем выход регистра текущего цикла подключен ко входу Формирователя сигналов, блокировки, выход которого соединен са вторым входом блока блокировки процессора.На чертеже приведена схема микропрограммного процессора.Схема микропрограммного процессаа состоит из блока 1 памяти, арифетика-логическаго устройства 2,блока 3 обмена данными, адресногоблока 4, буферной памяти данных 5и блока 6 микропрограммного управления. Оперативная память 1 связана сблоком 3 обмена данными входными информационными шинами 7, выходнымиинФормационными шинами 8, шинами 9управляющего слова памяти и шинами10 контроля состояния памяти, ас блоком 6 микропрограммного управления шинами 10 контроля состоянияпамяти, Блок 3 обмена.да. ными содержит регистр 11 данных, регистр 12слова памяти, счетчик 13 текущегоадреса, связанный с коммутатором14 данных и через элемент 15 задерж ки и блок выборки элементов 16 Ис входными элементами 17 И регистра11 данных, а также содержит блок 18определения момента обращения к оперативной памяти (блок проверки ло гических условий), связанный по входу 36 .с арифметика-логическим устройством 2 и счетчиком 13 текущего адреса, а па выходу с входнымиэл ментами И регистра 12 слова памяд 5 ти,. Блок 3 обмена данными связан сарифметика-логическим устройствам 2и буферной памятью данных 5 выходными информационнычи шинами 19 ивходными информационными шинами 20.Адресный блок 4 содержит счетчик21 адреса команды и счетчики 22 и23 адресов операндов (и счетчиков),связанные па выходу с арифметикологическим устройством 2, а такжесодержит регистры 24, 25 и 26, номера байта (п регистров относящиеся соответственно к адресу командыи адресам операндовБуфернаяпамять данных 5 связана с арифметико-логическим устройством 2 вход О ными и выходными информационными шичами. Блок 6 микропрограммного управления содержит регистр 27 текущегоцикла, память микропрограмм 28, дешиФратор 29 микрокоманд, формирователь 30 сигналов блокировки и блок31 блокировки процессора, элементы32, 33, 34, 35, 17, 37, 38, 39 И.Микропрограммный процессор предназначен для выполнения арифметических и логических операций надданными, расположенными в виде полейпа:тоянной или переменной длины вперативной памяти 1 . Обычный процесс выполнения операции в микропрограммном процессоре включает выборку из оперативной памяти данныхпа адресу одного или по адресамдвух операндов, выполнение нужнойоперации в арифметика-лагическомустройстве и размещение результатав оперативной памяти по адресу одного из операндов, наименьшей адресуемой единицей данных являетсябайт. Предусмотренный набор операцийвыполняется арифметика-логическимустройствам 2, причем обработкаполей происходит побайтно, а их длина определяется командой. За один цикл процессора может выполняться одна операция обработки данных, имеощих длину 1 байт.5Цикл оперативной памяти можно условно разделить на четыре равные части, отличающиеся между собой процессами, которые происходят в памяти,т.е. на части, соответствующие различным состояниям памяти. В состоянии 0 в оперативной памяти принимается управляющее слово, определяющее адрес данных и характер операции. В состоянии 1 работа памяти определяется операцией: в операции чтения происходит выборка данных, в операции записи прием данных, подлежащих хранению в памяти. Состояния 2 и 3 определяют регенерацию считанной информации или запись 20 информации, принятой в состоянии 1.Таким образом, данные для записи должны быть подготовлены процессором до того, как память достигнет состояния 1, а в операции чтения . 25 данные могут быть использованы процессором не ранее, чем память достигнет состояния 2, т.епо истечении времени выборки ТВ. Длительность цикла оперативной памяти в предлагае мом микропрограммном процессоре составляет 2,5 мкс, длительность цикла процессора 0,625 мкс, т.е. одну четвертую часть цикла оперативной памяти.35В микропрограммном процессоре предусмотрена аппаратура, позволяющая частично или полностью совместить циклы обработки данных процессором с циклами оперативной памяти, что приводит к. увеличению быстродействия процессора, Совмещение достигается эа счет того, что в процессоре организуется выборка и размещение данных в памяти группами при байтовой обработке, что позволяет при обработке данных текущей выборки заранее организовать обращение к оперативной памяти с целью чтения или записи данных, которые потребуются по окончании обработки данных теку щей выборки. Обмен между оперативной памятью и остальной частью микропрограммного процессора происходит 8-байтовыми словами.Основной для органиэации такого 55 обмена является разделение текущего адреса байта данных или текущегоадреса команды на две части: физический адрес слова памяти и номер байта в слове памяти, причем физичес ким адресом слова являются старшие разряды адреса байта, а номерами байта в слове - младшие разряды адреса байта. Физический адрес слова и номер байта в процессе обработки мо гут изменяться неэависимо друг отдруга,Обмен данными с оперативнойпамятью и обработка происходят впредлагаемом микропрограммном процессоре следующим образом. При необходимости чтения или записи данныхв регистре 12 слова формируется управляющее слово, содержащее физическийадрес 8-байтового слова памяти,запрос обращения к оперативной памяти,код операции памяти и другие данные,и передаются в блок 1 памяти черезшины 9 управляющего слова. В операции чтения по окончании времени выборки ТВ, что соответствует состоянию памяти 2, сигналы контроля состояния памяти 10 разрешают запись8-байтового слова с инФормационныхшин 8 памяти в регистр 11 данных через элементы 32 И. Если в управляющемслове указана операция записи, топосле приема управляющего слова,чтосоответствует состоянию памяти 1,оперативная память принимает черезвходные информационные шины 7-8-.бай-.товое слово, сформированное заранеев регистре 11 данных.Текущие адреса команды и операндов хранятся в адресном блоке 4таким образом, что физический адресслова памяти, которому принадлежатбайты команды или операндов, содержится в счетчиках 21, 22, 23соответственно, а номера байтов - врегистрах 24, 25 и 26. Если в регистр 11 данных выбрано слово, соответствующее физическому адресу всчетчиках 21, 22 или 23, значениеномера байта переписывается подуправлением микрокоманд иэ регистра24, 25 или 26 через элементы 33, 34или 35 И в счетчик 13 текущего адреса 1 нужный байт появляется на выходекоммутатора 14 данных и может бытьиспользован арифметико-логическимустройством 2.Последовательное изменение Физического адреса осуществляется под управлением микрокоманднепосредственно в счетчиках 21 и 22или 23, а переход к непоследовательнорасположенным словам осуществляетсяпутем измерения адресов в арифметикологическом устройстве 2, для чеговыходы счетчиков 21, 22, 23 и регистров 24, 25 и 26 соединены со входами арифметико-логического устройства 2. а выходы счетчиков с выходными шинами 20 арифметико-логического устройства 2Текущая адресация данных внутрислова осуществляется е помощью счетчика 13 текущего адреса, содержимоекоторогс может последовательно изменяться под управлением микрокомандв сторону увеличения или уменьшения,После выборки нужного количествабайтов данных текущее значение счетчика 13 может быть возвращено под управлением микрокоманд в 1 егистр 24, 25 или 26 номера байта.При обработке после одного из операндов обычно размещается частично или частично или полностью в буФерной памяти данных 5. При этом осуществляется требуемое количество обращений к оперативной памяти и последовательная пересылка байтов данных через шины 19 с коммутатора 14 данных в буферную память 5, Таким образом создается достаточный запас данных для обработки без обращений к оперативной памяти по адресу этого операнда. Далее таким же способом происходит выборка данных из поля другого операнда в памяти, но данные побайтно пересылаются через шины 19 на вход арифметико-логического устройства 2. Одновременно происходит побайтнаЯ выборка другого операнда из буферной памяти 5 и формирование байта результата. Результат как правило должен быть размещен в оперативной памяти. Накопление результата происходит в регистре 11 данных на месте использованных байтов исходных данных под управлением счетчика 13 текущего адреса следующим образом. Значение счетчика 13, в соответствии с которьм сформирован выход коммутатора 14 данных, поступает через элемент 15 задержки на блок 16 выборки элементов И. Элеменг 15 задержки обеспечивает запаздывание счетчика 13 текущего адреса на один цикл процессора. Таким образом, когда новым значением счетчика 13 выбирается очередной байт исходных данных, на блоке 16 выборки элементов И имеется предыдущее значение номера байта а на выходных шинах арифметико-логи ческого устройства 2 имеется результат обработки предыдущего байта. Этот результат и записывается под управлением микрокоманд в регистр 11 данных через элементы 17 И на место, определяемое блоком 18 выборки элементов И, который дешифрует задержанное значение номера байта.Текущее значение номера байта в счетчике 13 используется также для определения моменга формирования управляющего слова памяти, что озна" чает и момент обращения к памяти,так как управляющее слово содержит запрос на выполнение операцчи памяти. Еслипри обработке поля данных справа налево текущее значение номера байта в счетчике 13 НБ = О или при обработке поля данных слева направо НБ = 7, происходит обработка последнего байта в слове, и для продол" жения операции бзз прностанова в следующем цикле процессора необходимо, чтобы в регистр 11 данных были приняты новые данные, или чтобы регистр 11 данных к началу следующегоцикла был освобожден от результата,Для этого необходимо сформироватьзапрос обращения к оперативной памя ти раньше, чем процессор закончитобработку последнего байта в слове,Если поле данных заканчивается впределах данного слова памяти, тоновое обращение для выборки данныхне требуется, т,е. момент формирования запроса на выполнение операции памяти зависит и от текущейдлины обрабатываемого поля. Формирование управляющего слова определяется схемой 18 определения моментаобращения к оперативной памяти,формирующей управляющие сигналы какфункции текущего значения номерабайта НБ и текущего значения длиныполя Л. Текущее значение длины поля, 2 О указыва щее в каждый момент времениколичество байтов данных, подлежащихобработке в данной операции, формируетая в процессе обработки в арифметико-логическом устройстве 2 ипередается в схему 18 определениямомента обращения к оперативной памяти через шины 36 текущей длиныполяСхема 18 может проверять несколько различных соотношений номера ЗО байта и длины в зависимости от выполняемой операции, Например, приобработке байтов ноля слева направоможет проверяться соотношение типа(НБ =- 5)(ЛЪ 2) + (НБ = 6): (ЛЪ 1) + 35 + (НБ = 7), где знак+указывает логическое сложение.Если схема 18 сформировала управляющий сигнал, то в регистре 12 слова памяти Формируется требуемое щ управляющее слово, причем физическийадрес очередного слова памяти записывается под управлением микрокомандчерез элементы 37, 38 или 39 и изнужного счетчика (21 22 или 23).После этого операция памяти считаетсяинициированной, а содержимое счетчиков 21, 22 или 23 может изменятьсяпроцессором с целью подготовки следующего обращений.Из приведенного соотношения междуномером байта и текущей длиной полявидно, что эалрос на выполнениеогерации памяти в этом случае можетФормироваться во,время обработкипроцессором байта 5, байта б илибайта 7 текущего слова данных. Еслизапрос на выполнение операции памятиформируется во время обработки байта5, то первая половина цикла памяти(Т) используется процессором для 6 О обработки байтов б и 7, а после выборки и приема в регистр 11 данныхнового слова памяти при состояниипамяти 2 начинается обработка байтаО следующего слова без приостановки 65 действия процессора. В этом случае10 741269 процессор работает одновременно ипараллельно с блоком памяти в течение всего цикла памяти, т.е. осуществляется полное перекрытие циклаоперативной памяти циклами процессора. Обращение к блоку памяти во 5время обработки процессором байта 6или байта 7 возможно тогда, когдаобработка заданного поля начинаетсяс этих байтов. Однако в этих случаяхвозможно только частичное перекрытие цикла памяти циклами процессора,так как процессор не имеет запасатекущих данных на два цикла процессора, соответствующих времени выборки оперативной памяти (ТБ), иего действие должно блокироватьсядо получения нового слова данныхиз памяти, т.е. до достижения памятью состояния 2. Блокирование действия процессора производится в блоке 6 микропрограммного управления..Блок 6 микрбпрограммного управления содержит постоянную память 28.для хранения микропрограмм, согласно которым выполняются операции процессора. Номер текущего. цикла процессора хранится в регистре 27 текущего цикла и представляет собой одновременно и адрес постоянной памяти 28, по 30 которому находится слово микрокоманды данного цикла. Извлеченное из памяти 28 слово дешифруется на дешифраторах 29 микрокоманд, на вы-ходах которых формируются сигналы 35 управления вентилями микроопераций. Схема 30 определения момента блокировки формирует сигнал при появлении в регистре текущего цикла процессора 27 номеров таких циклов, в которых требуется результат очередной операции оперативной памяти. Блок 31 блокировки процессора при наличии сигнала с формирователя 30 анализирует состояние оперативной памяти по сигналам, поступающим по шинам 10 контроля состояния памяти. Если память находится в состоянии 2, которое означает, что в оперативной памяти завершается запись предыдущего 8-байтового слова результата, либо выбрано новое 8-байтовое слово Юйнных, действие процессора не блокируется, т.е. микропрограмма процессора продолжается без задержки, Если память не достигла состояния 2, схема блокирования вырабатывает сигналы, блокирующие выход микрокоманд и изменение номера цикла. Таким образом, процессор оказывается в состоянии ожидания до тех пор, пока 60 устанавливается состояние 2 оперативной памяти.Изобретение применимо в вычислительных машинах, имеющих быстродействующие арифметико-логические уст ройства и оперативную память низкого быстродействия,В предлагаемом микропрограммном процессоре при его реализации может модифицироваться величина порции данных для обмена с оперативной памятью и соотношение между длительностью цикла оперативной памяти длительного процессора, что приведет к изменению разрядности счетчика 13 и регистров 24, 25, 26, к изменению разрядности регистра 11 данных,блока 16 выборки, а также к выбору другого объема буферной памяти данных 5. Уменьшение времени выполнения операций находится в пределах от 1,6 до 2 раэ для различных операций. Формула изобретения Микропрограммный процессор, содержащий буферную память, арифметикологическое устройство, регистр слова памяти, регистр данных, коммутатор данных, блок выборки элементов И, элемент задержки, блок памяти, память микропрограмм, дешифратор микрокоманд, регистр текущего цикла, блок блокировки процессора, восемь элементов И, причем вход-выход арифметическо-логического устройства соединен с выходом-входом буферной памяти, выход дешифратора микрокоманд соединен с первыми входами первого, второго, третьего, четвертого, пятого, шестого, седьмого элементов И, первым входом буферной памяти и первым входом арифметическо-логического устройства, первый выход блока памяти соединен с первым входом восьмого элемента И, выход которого подключен к первому входу регистра данных, выход которого соединен с первым входом блока памяти и первым входом коммутатора данных, выход которого подключен ко второму входу буферной памяти и второму входу арифметическо-логического устройства, второй выход блока памяти соединен со вторым входом восьмого элемента И и первым входом блока блокировки процессора, выход которо" го подключен к первому входу дешифратора микрокоманд и первому входу регистра текущего цикла, выход которого соединен со входом памяти микропрограмм, выход которой соединен со вторым входом дешифратора микрокоманд и вторым входом регистра текущего цикла, первый выход арифметическо-логического устройства соединен со вторым входом первого элемента И, выход которого подключен ко второму входу регистра данных, выхо12 741269 Патент,л, Проектная,4 лиал ППП Ужгород,ды пятого, шестого и седьмого элементов И подключены ко входам регистра слова памяти, выход которого соединен со вторым входом блока памяти,выход элемента задержки соединен совходом блоха выборки элементов И, 5выход которого подключен к третьемувходу первого элемента И, о т л ич а ю щ и й с я тем, что, с цельюповышения быстродействия, в него введены счетчик текущего адреса, блокпроверки логических условий, и счетчиков и и регистров, формировательсигналов блокировки, при этом первые выходы и счетчиков подключеныко вторым входам соответственно пятого, шестого и седьмого элементовИ, первые выходы и регистров подключены ко вторым входам соответственно второго, третьего и четвертого элементов И, вторые выходы исчетчиков .и и регистров соединены с 20соответствующими входами арифметическо-логического устройства, второйвыход которого соединен с первымвходом блока проверки логических ЦНИИПИ Заказ 332 б Тираж 751 Подписное условий, выход которого подключенк третьим входам пятого, шестого иседьмого элементов И, первый выходарифметическо-логического устройствасоединен со входами и счетчиков ипервыми входами и регистров, выходывторого, третьего и четвертого элементов Й подключены ко входам счетчика текущего адреса, выход которого подключен ко второму входублока проверки логических условий,входу элемента задержки, второму входу кою 4 утатора данных и вторым входам п регистров, причем выход регистра текущего цикла подключен ковходу формирователя сигналов блокировки, выход которого соединен совторым входом блока блокировки процессора.Источники информации,принятые во внимание при экспертизе1. Патент США Р 35 б 4507,кл. 340-172.5, 1971.2. Хассон С. Микропрограммноеуправление, М., Мир, 1974

СмотретьЗаявка

2566799, 04.01.1978

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКОЕ БЮРО ВЫЧИСЛИТЕЛЬНЫХ МАШИН

БЕЛЯУСКАС БРОНИСЛОВАС-ПЯТРАС БРОНИСЛАВОВИЧ, ВАЛАТКАЙТЕ РЕГИНА ИОНОВНА, ЖИНТЕЛИС ГИНТАУТАС БЕРНАРДОВИЧ, ЛАНЦМАН ОЛЕГ МОИСЕЕВИЧ, ЛУКШЕНЕ ДАЛЯ КАЗИМЕРОВНА, НЕМЕЙКШИС АНТАНАС МИКОЛОВИЧ НЕМЕ, СВЕТИАС КАЗИМЕРАС-РИМВИДАС СТАСЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 15.06.1980

Код ссылки

<a href="https://patents.su/6-741269-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для контроля счетчиков

Следующий патент: Устройство для моделирования отказов

Случайный патент: Цилиндровый механизм замка