Система для обмена данными между информационными процессорами

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1001070

Автор: Кирпичев

Текст

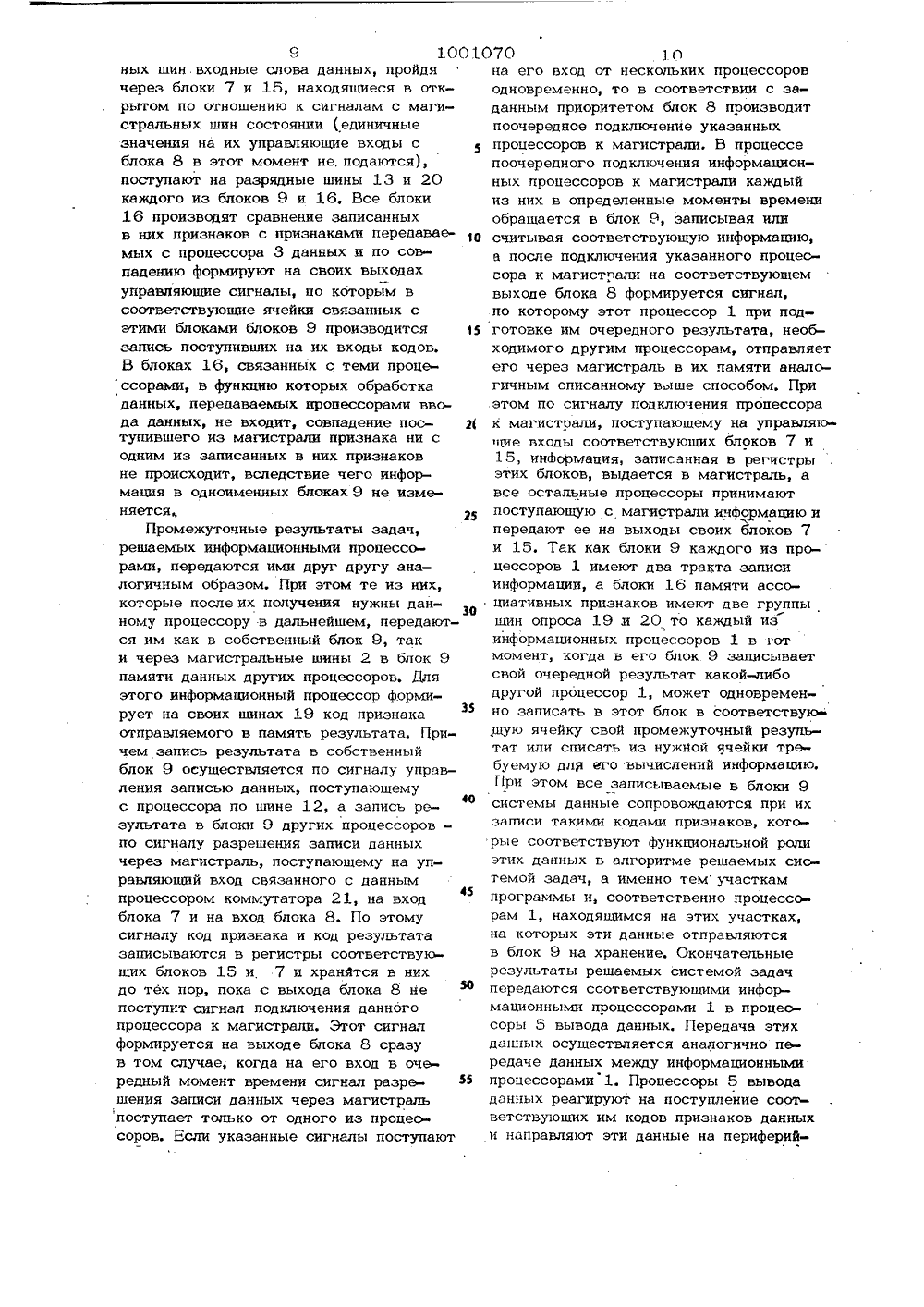

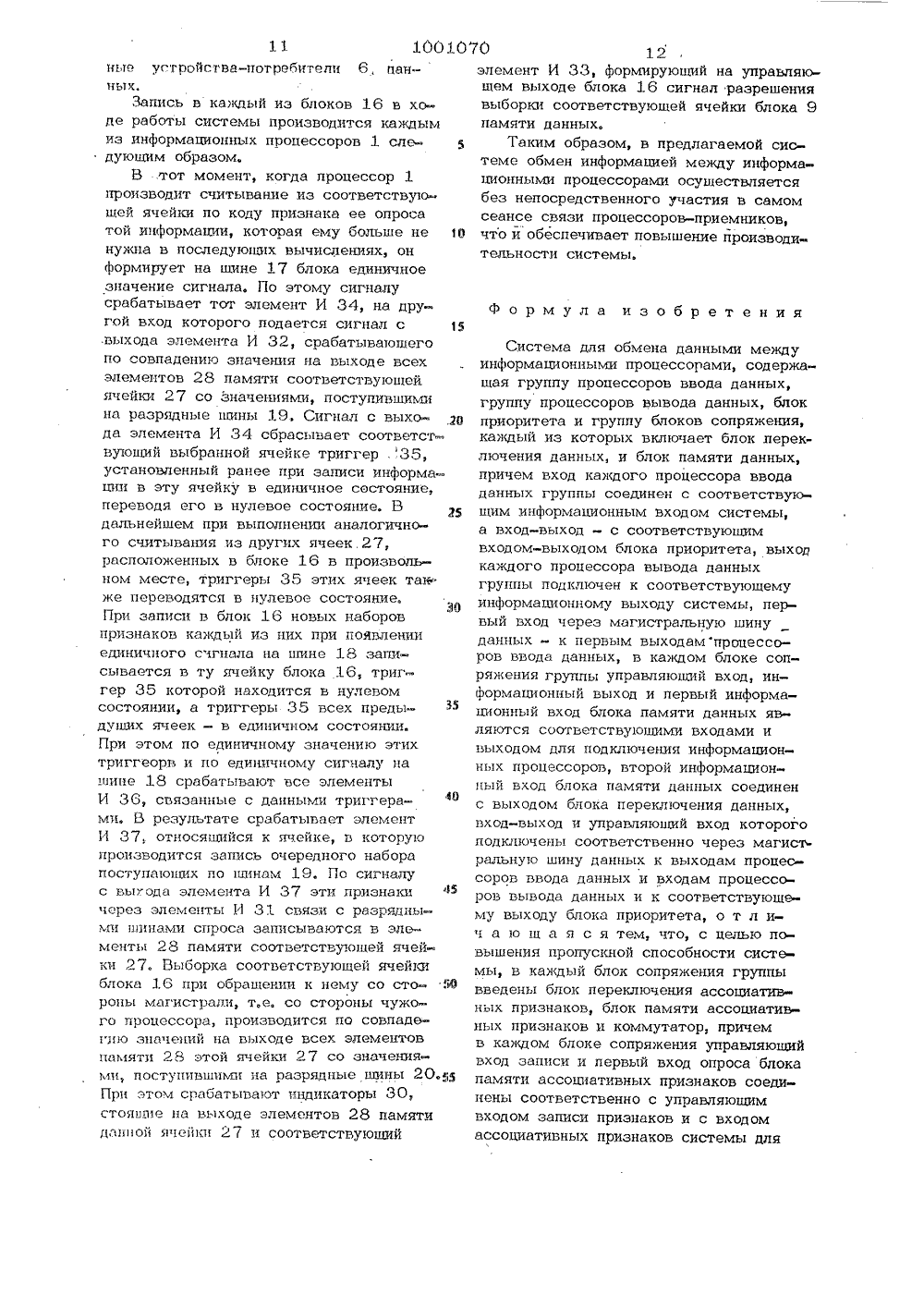

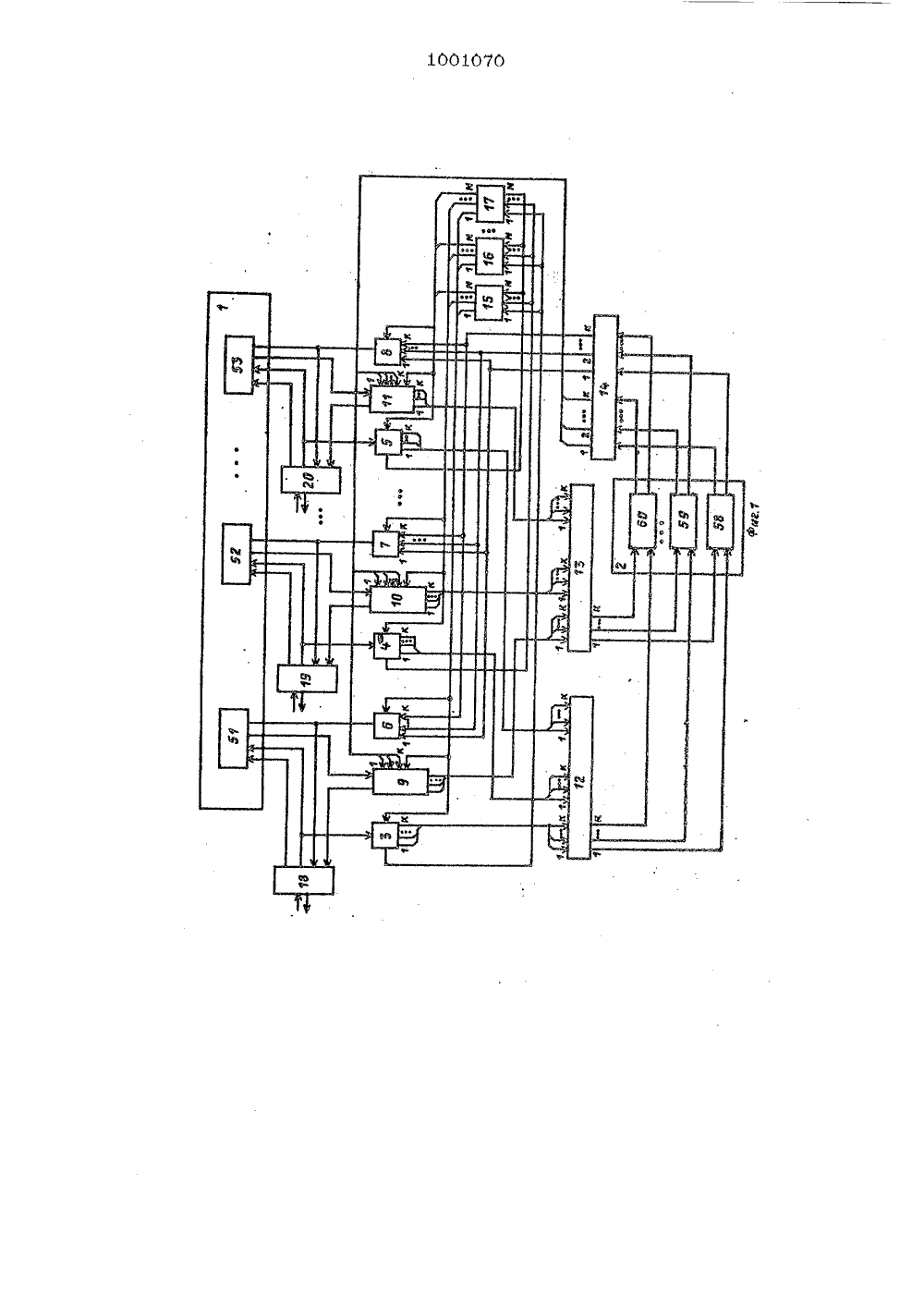

Союз Советск ихСоциалистическихРеспублик Оп ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(54) СИСТЕМА ДЛЯ ОБМЕНА ДАННЫМИ МЕЖДУ ИНФОРМАЦИОННЫМИ ПРОЦЕССОРАМИ 1Изобретение относится к вычислительной технике и может быть использованов многопроцессорных системах для обменаданными между процессорами.Известна система для обмена данны-ми между процессорами, содержащая5множество процессоров, блоки местнойпамяти по числу процессоров, множестводешифраторов адреса, связывающих каж-дый из процессоров с определеннымвходом соответствующего общего ЗУ,и множество блоков управления, обеспечивающих запрет обращения к общимЗУ одних из процессоров, когда аналогичные обращения к этим ЗУ выпопняютдругие процессоры-1,Недостаток системы состоит в ниэкой пропускной способности и повышенных затратах оборудования.Наиболее близкой к предлагаемой поФтехнической сущности является система,содержащая магистральные адресныешины и магистральные шины данных,соединенные с процессорами ввода и 2вывода данных, магистральные блоки переключения адреса и данных по чиспу информационных процессоров, соединенные с магистральными винами, блок поочередного подключения процессоров к магистрали, выходы которого подклучены к управляющим входам соответствующих процессоров ввода данных и ма . гистральных блоков переключения, бди ки местной памяти данных с произвольной выборкой по числу информационных процессоров, первые разрядные шины записи и считывания и первые адресные шины которых соединены с соответствую- шими информационными процессорами, а вторые разрядные шины записи - с выходами соответствующих магистральных блоков переключения данных, и блоки памяти параллельно пересылаемых информационных слов (потоков сообшений), включенные между соответствующими информационными процессорами и магистральными блоками переключения адреса и данных и связанные с вторыми раэ 1001070рядными шинами считывания ч вторыми адресными шинами соответствуюших местных блоков памяти 2 .Недостатки этой системы состоят в низкой пропускной способности, больших затратах оборудования и сложности системы.Цель изобретения - повышение пропускной способности и упрошение системы. 1 ОПоставленная цель достигается тем, что в систему, содержащую группу процессоров ввода данных, группу процессоров вывода данных, блок приоритета и группу блоков сопряжения, каждый из которых включает блок переключения данных и блок памяти данных, причем вход каждого процессора ввода данных группы соединен с соответствуюшим информационным входом системы, а вход -выход - с соответствующим входом-выходом блока приоритета, выход каждого процессора вывода данных группы подключен к соответствуюшему информационному выходу системы, первый вход через магистральную шину данныхк первым выходам процессоров ввода данных, в каждом блоке сопряжения группы управляющий вход, информационный выход и первый информационныйЗО вход блока памяти данных являются соответствуюшими входами и выходом для подключеыи информационных процессоров, второй информационный вход блока памяти данных соединен с выходом блока переключения данных, вход-выход З , и управляюший вход которого подключены соответственно через магистральную шину данных к выходам процессоров ввода данных и входам процессоров вывода данных и к соответствующему выходу блока приоритета, в каждый блок сопряжения группы введены бпок переключения ассоциативных признаков, блок памяти ассоциативных признаков и коммутатор, ричем в каждом блоке сопряжения управ-ф 1 ф пяюший вход записи и первый вход опро:а блока памяти ассоциативных признаков соеФшены соответственно с управ ляющим входом записи признаков и с входом ассоциативных признаков систе- ф мы для подключения информационного процессора и информационным входом коммутатора, управляюший вход которогоподключен к дополнительному управляющему входу системы для подключения Ыинформационного процессора, а выходкоммутатора - к информационному входублока переключения ассоциативных признаков управляощий Вход и Выход соответственно с управляющим входом блокапереключения данных и вторым входомопроса блока памяти ассоциативных призиаков того же блока сопряжения группы,выходы процессоров ввода данных и входы процессоров вывода данных соединены через магистральную шину ассоциативных признаков с входами-выходамиблоков переключения ассоциативных признаков.На фиг. 1 представлена структурнаясхема системы; на фиг. 2 - функциональные схемы блока памяти ассоциативныхпризнаков и блока памяти данных; нафиг. 3 - блок-схема информационногопроцессора; на Фиг, 4 и 5 - блок-схемыпроцессоров ввода и вывода данных;на фиг. 6 - функциональные схемы блька приоритета, блоков переключенияданных и ассоциативных признаков; нафиг, 7 - функциональная схема блокауправления выводом данных,Система содержит (фиг. 1) информационные процессоры 1, магистраль-ные шины 2 данных, процессоры 3 ввода данных, периферийные устройства- источники данных 4, процессоры 5 вывода данных, периферийные устройства- потребители данных 6, блоки 7 переключения данных, блок 8 приоритета, блоки 9 памяти данных, разрядные шины 10 считывания данных, первые разрядные шины 11 записи данных, шины 12 управления записью данных, вторые разрядные шины 13 записи данных, магистральные шины 14 ассоциативных признаков, блоки 15 переключения ассоциативных признаков, блоки 16 памяти ассоциативных признаков, первые шины 17 управленйя записью признаков, вто- . рые шины 18 управления записью признаков, первые шины 19 опроса, вторые разрядные шины 20 опроса и коммутаторы .21.Каждый блок 9 памяти данных соде жит (фиг. 2) ячейки 22 памяти для хранения данных, элементы памяти 23 ячеек 22, элементы И 24 связи с разрядными шинами 10, элементы И 25 связи с разрядными шинами 11 и элементы И 26 связи с разрядными шинами 13, Каждый блок 16 памяти ассоциа тивных признаков (фиг. 2) содержит ячейки 27 памяти для хранения ассоциативных признаков, элементы памяти 28 ячеек 27, первые индикаторы 29 совпадения, вторые индикаторы 30 совпадения, элементы И 31 связи с первыми разряд101001ными шинами 19 опроса, первую группуэлементов И 32, вторую группу элементов И 33, третью группу элементовИ 34, триггеры 35, четвертую группуэлементов И 36 и пятую группу элементов И 37.Информационный процессор 1 содержит (фиг, 3) регистр 38 команд, состоящий из регистра 39 кода операции ирегистра 40 признака опроса, генера тор 41 синхронизируюших импульсов,вход 42 фазирования генератора синхронизируюшнх импульсов от задающегогенератора синхронизирующих импульсовсистемы, счетчик 43 тактов, микропрограммную память 44, регистр 45 микрокоманд, коммутатор 46, состоящий изэлементов И 47, счетчик 48 команд,элемент И 49, коммутатор 50, состоящий из элементов И 51 - 53 и элементов ИЛИ 54, блок 55 постоянной памяти, регистр 56 числа, арифметико-логическое устройство 57, вход 58 передачисигнала требования с блока 8 и дополнительный управляющий .выход 59 информационного процессора. Каждая очередная команда программы, выполняемойинформационным процессором, считывается из блока 9 в регистр 38. Одна частькомандного слова является кодом выпол- ЗОняемой процессором операции, а другаячасть - признаком опроса, по которому1в зависимости от кода операции производится или считывание данных из памяти, или запись данных в память, или припереходе на другую ветку программы35считывание соответствующей этой веткепрограммы команды.Счетчйк 48 команд обеспечивает ходвыполнения программы, Счетчик 43производит постоянный счет импульсов,40поступающих с выхода генератора 41.По окончании каждой операции (по сигналу с выхода регистра 45) счетчик 43обнуляется, По коду операции и номерутакта операции из микропрограммной45памяти 44 в регистр 45 считываетсясоответствующая микрокоманда, по которой в арифметико логическом устройстве57 выполняются соответствующие микрооперации. С помощью определенныхмикрокоманд из блока 55 обеспечиваетсяпередача ассоциативных признаков вблок 16,Коммутатор 21 (фиг. 3) состоит изэлементов И 60, 55На фиг. 4 представлена функциональная схема процессора 3 ввода данных ипоказаны связи его с магистральными 070 4шинами 2 и 14 и с периферийными устройствами - источниками данных 4 и блоком 8, Процессор 3 ввода данных содержит генератор 61 синхронизирующих импульсов, счетчик 62 тактов, р. гистр 63 приема входных сигналов, регистр 64 текущего адреса, микропрограммную память 65, регистр 66 микрокс. манд, арифметико-логическое устройство 67, регистр 68 данных, регистр 69 ассоциативных признаков, элемент 70 задержки, вход 71 обнуления регистра 69, управляющий вход 72 регистра 69 (или счетчика тактов), синхронизирующий вход 73 регистра 69 (или счетчика тактов), коммутатор 74, элементы И 75, коммутатор 76, элементы И 77, вход 78 фазирования генератора 61 синхроимпульсов и управляющий выход 79. В каждом такте работы процессора 3 по синхроимпульсу с генератора 61 в регистр 63 записывается определенный код входных сигналов. По этому коду, по номеру такта, сформированному на выходе счетчика тактов, и по значению текущего адреса в регистре 64 из микропрограммной памяти 65 в регистр 66 считывается микрокомандное слово, определенные разряды котор го передаются обратно в регистр .текущего адреса. Определенная последовательность считываемых микрокомандных слов (микропрограмма) обеспечивает обработку входных сигналов в арифметико ногическом устройстве 67 и передачу данных и сопровождающих их ассоциативных признаков в регистры 68 и 69. По приходу с блока 8 сигнала подключьния данного процессора к магистрали очередное слово данных и сопровождающий его ассоциативный признак передаются с помощью коммутаторов 74 и 76 в магистраль (шины 2 и 14).Далее сигнал подключения процессора к магистрали, пройдя через элемент 70 задержки, обнуляет регистры 68 .и 69. Очередное требование на передачу данных через магистраль формируется в процессоре 3 на управляющем выходе 79,Процессор 5 вывода данных содержит (фиг. 5) генератор 80 синхроимпульсов, счетчик 81 тактов, регистр 82 текущего адреса, регистр 83 приема управляющего слова, микропрограммную память 84, регистр 85 микрокоманд, дешифратор 86, накопитель 87 оперативной информацки, блок 88 управления выводом данных и вход 89 фазирования генерато.ра 80 синхроимпульсов. Организация70 8ферийного устройства-потребителя 6 данных, например устройства вывода на перфоленту с числом дорожек, равным числу разрядов передаваемых на это устройство блоком 88 кодов.Система работает следующим образом.В исходном состоянии все ячейки 27 блоков 16 находятся в обнуленном состоянии, Перед началом работы системы каждый из информационных проц ссоров 1 производит запись нужных наборов признаков в ячейки своего блока 16. Эти наборы признаков с выходом ассоциативных признаков процессора поступают на разряпные шины 1 9, а управляющие сигналы процессора поступают на шины 17 и 18 управления записью признаков. Указанные наборы признаков после записи их в ячейки блоЪка 16 становятся указателями местоположения (адресами) ячеек блока 9 при их выборке. При формировании на выходах процессора 1 соответствующего набора признаков этот набор сравнивается со всеми записанными в ячейки бло- ка 16 наборами признаков, По совпадению с одним из этих наборов признаков на соответствующем управляющем выходе этого блока формируется управляющий сигнал, по которому в одноименном блоке 9 производится выборка соответствующей ячейки. При этом по сигналу разрешения записи данных, поступающему на шину 12 блока 9 памяти данных, данные с выхода процессора 1, йоступившие на разрядные шины 11, записываются в выбранную ячейку блока 9.После записи в блоки 9 и 16 необ ходимых для работы системы наборов признаков и исходных данных, в том числе и команд выполняемых программ, информационные процессоры переходят к решению возложенных на них задач.При этом процессоры 3 ввода данных принимают поступаюшую в них с периферийных устройств-источников данных информацию, производят предварительную ее обработку, например сортировку и накопление, и формируют на своих выходах по сигналам с блока 8, разрешающего доступ данного процессора к магИсч. рали, входные слова данных, одна часть которых выступает в качестве признака данных, а другая часть - в виде собственно данных. Признаки данных поступают на магистральные шины 14 ассоциативных признаков, а собственно данные - на магистральные шины 2. С магистраль 7 10010выполнения микропрограммы в процессоре 5 обеспечивается таким же образом,как и в процессоре 3 ввода данных, Спомощьюдешифратора 86 управляющиеслова записываются в регистр 83, а5собственно данные - в накопитель 87, Вдальнейшем с помощью блока 88 данные вопределенной последовательности по времении определенными частями передаются навход периферийного устройства - потребителя данных 6.Блок 8 приоритета (фиг. 6) содержитзадающий генератор 90 синхронизируюшихиспульсов систем и -разрядный регистр гкаждый разряд которого, кроме первогои последнего, содержит триггер 91,первый элемент И 92 и второй элементИ 93 (в первом и последнем разрядахустройства второй элемент И 93 отсутствует)Блоки 7 переключения данныхи 15 переключенияассоциативных признаков содержат регистр, состоящий изтриггеров 94, магистральные передающие ключевые элементы 95 и 96, элемент задержки 97 и элемент НЕ 98. 25В блоках 7 в состав регистра входяттакже элементы И 99. Выход 100 задающего генератора 90 синхронизирующих импульсов соединен с входами 42,78 и89 соответствующих процессов,при этомс помощью сигналов фазирования передаваемых на эти входы, обеспечивается синхронная работа (работа на частоте задающего генератора 90) всех процессоров системы. После передачи че 35рез магистраль очередного слова данныхи его ассоциативного признака в блоке 8 сбрасывается триггер, соответствующий тому процессору, который выдалэто слово на магистраль. Получив сигнал .о нулевом значении триггера, процессорпереходит в режим готовности выдачина магистраль следующего слова дан ных и процессор передачи данных через магистраль вновь повторяется.45Б(ок 88 управления выводом данныхпроцессора 5 содержит (фиг, 7) элементы И 101, элементы ИЛИ 102, буферные элементы 103 согласования, дешифратор 104, приемный регистр 105, состоящий из триггеров 106.56Накопитель 87 оперативной информации содержит (фиг. 7) элементы 107памяти и элементы И 108 и 109. Входе работы блока 88 считанные из. ячеек накопителя 87 на приемный регистр 55105 слова передаются отдельными частями с определенным интервалом времени кежду этими частями на вход пери01070 30на его вход от нескольких процессоров одновременно, то в соответствии с заданным приоритетом блок 8 производит поочередное подключение указанных зо 35 4 О 45 9 10 ных шин.входные слова данных, пройдя через блоки 7 и 15, находящиеся в открытом по отношению к сигналам с магистральных шин состоянии (единичные значения на их управляющие входы с блока 8 в этот момент не, подаются), поступают на разрядные шины 13 и 20 каждого из блоков 9 и 16, Все блоки 16 производят сравнение записанных в них признаков с признаками передаваемых с процессора 3 данных и по совпадению формируют на своих выходах управляющие сигналы, по которым в соответствующие ячейки связанных с этими блоками блоков 9 производится запись поступивших на их входы кодов. В блоках 16, связанных с теми процессорами, в функцию которых обработка данных, передаваемых процессорами ввода данных, не входит, совпадение поступившего из магистрали признака ни с одним из записанных в них признаков не происходит, вследствие чего информация в одноименных блоках 9 не изменяетсяПромежуточные результаты задач, решаемых информационными процесс рами, передаются ими друг другу аналогичным образом. При этом те из них, которые после их получения нужны данному процессору в дальнейшем, передаются им как в собственный блок 9, так и через магистральные шины 2 в блок 9 памяти данных других процессоров. Для этого информационный процессор формирует на своих шинах 19 код признака отправляемого в память результата. Причем запись результата в собственный блок 9 осуществляется по сигналу управления записью данных, поступающему с процессора по шине 12, а запись результата в блоки 9 других процессоров - по сигналу разрешения записи данных через магистраль, поступающему на управляющий вход связанного с данным процессором коммутатора 21, на вход блока 7 и на вход блока 8. По этому сигналу код признака и код результата записываются в регистры соответствующих блоков 15 и, 7 и хранйтся в них до тех пор, пока с выхода блока 8 не поступит сигнал подключения данного процессора к магистрали. Этот сигнал формируется на выходе блока 8 сразу в том случае, когда на его вход в оч редный момент времени сигнал разр щения записи данных через магистраль поступает только от одного из процеосоров. Если указанные сигналы поступают процессоров к магистрали. В процессепоочередного подключения информационных процессоров к магистрали каждыйиз них в определенные моменты времениобращается в блок 9, записывая или считывая соответствующую информацию,а после подключения указанного процессора к магистрали на соответствующемвыходе блока 8 формируется сигнал,по которому этот процессор 1 при подготовке им очередного результата, необходимого другим процессорам, отправляет его через магистраль в их чамяти аналогичным описанному выше способом. При этом по сигналу подключения процессора к магистрали, поступающему на управляющие входы соответствующих блоков 7 и 15, информация, записанная в регистры этих блоков, выдается в магистраль, а все остальные процессоры принимают поступающую с магистрали информацию и передают ее на выходы своих волоков 7 и 15. Так как блоки 9 каждого из процессоров 1 имеют два тракта записи информации, а блоки 16 памяти ассоциативных признаков имеют две группы шин опроса 19 и 20 то каждый из информационных процессоров 1 в вот момент, когда в его блок 9 записывает свой очередной результат какой-либо другой процессор 1, может одновременно записать в этот блок в соответствуюшую ячейку свой промежуточный результат или списать из нужиой ячейки требуемую для его вычислений информацию.При этом все записываемые в блоки 9 системы данные сопровождаются при их записи такими кодами признаков, которые соответствуют функциональной роли этих данных в алгоритме решаемых системой задач, а именно тем участкам программы и, соответственно процессорам 1, находящимся на этих участках, на которых эти данные отправляются в блок 9 на хранение. Окончательные результаты решаемых системой задач передаются соответствующими информационными процессорами 1 в процессоры 5 вывода данных. Передача этих данных осуществляется аналогично передаче данных между информационными процессорами 1. Процессоры 5 вывода данных реагируют на поступление сост ветствующих им кодов признаков данных и направляют эти данные на периферий1003 0 ные устройства-потребители 6, данных.Запись в каждый из блоков 16 в ходе работы системы производится каждымиз информационных процессоров 1 следующим образом,В тот момент, когда процессор 1производит считывание из соответствующей ячейки по коду признака ее опросатой информации, которая ему больше не 1 Онужна в последующих вычислениях, онформирует на шине 17 блока единичноезначение сигнала, По этому сигналусрабатывает тот элемент И 34, на другой вход которого подается сигнал с 1.выхода элемента И 32, срабатывающегопо совпадению значения на выходе всехэлементов 28 памяти соответствуюцейячейки 27 со значениями, поступившимина разрядные шины 19, Сигнал с выхо- щда элемента И 34 сбрасывает соответст=вующий выбранной ячейке триггер 35,установленный ранее при записи информации в зту ячейку в единичное состояние,переводя его в нулевое состояние. Вдальнейшем при выполнении аналогичного считывания из других ячеек.27,расположенных в блоке 16 в произвольном месте, триггеры 35 этих ячеек танже переводятся в нулевое состоякие.При записи в блок 16 новых наборовпризнаков каждый из них при появленииединичного сигнала на шине 18 записывается в ту ячейку блока 16, триггер 35 которой находится в нулевомсостоянии, а триггеры 35 всех предыдуших ячеек - в единичном состоянии.При этом по единичному значению этихтриггеорв и по единичному сигчалу нашине 18 срабатывают все элементыИ 36, связанные с данными триггера Оми. В результате срабатывает элементИ 37, относящийся к ячейке, в которуюпроизводится запись очередного наборапоступающих по шинам 19. По сигналус выода элемента И 37 зти признакичерез элементы И 31 связи с разрядными шинами спроса записываются в элементы 28 памяти соответствующей ячейки 27, Выборка соответствующей ячейкиблока 16 при обращении к нему со сто- Ироны магистрали, т.е. со стороны чужого процессора, производится по совпадению значений па выходе всех элементовпамяти 28 этой ячейки 27 со значениялж, поступившими па разрядные шины 20,ю;5При этом срабатывают индикаторы 30,стоящие на выходе элементов 28 памятиданной ячейки 27 и соответствующий 70 12 элемент И 33, формирующий на управляю шем выходе блока 16 сигнал разрешения выборки соответствуюшей ячейки блока 9 памяти данных.Таким образом, в предлагаемой системе обмен информацией между информационными процессорами осуществляется без непосредственного участия в самом сеансе связи процессоров-приемников, что и обеспечивает повышение йроизводительности системы. Формула изобретения Система для обмена данными между информационными процессорами, содержащая группу процессоров ввода данных, группу процессоров вывода данных, блок приоритета и группу блоков сопряжения, каждый из которых включает блок переключения данных, и блок памяти данных, причем вход каждого процессора ввода данных группы соединен с соответствук- шим информационным входом системы, а вход-выход - с соответствующим входом-выходом блока приоритета, выход каждого процессора вывода данных группы подключен к соответствующему информационному выходу системы, первый вход через магистральную шину данных - к первым выходампроцессоров ввода данных, в каждом блоке сопряжения группы управляющий вход, информационный выход и первый информационный вход блока памяти данных являются соответствующими входами и выходом для подключения информационных процессоров, второй информационный вход блока памяти данных соединен с выходом блока переключения данных, вход-выход и управдяюший вход которого подключены соответственно через магистральную шину данных к выходам процессоров ввода данных и входам процессоров вывода данных и к соответствуюшему выходу блока приоритета, о т л ич а ю ш а я с я тем, что, с целью повышения пропускной способности сист мы, в каждый блок сопряжения группы введены блок переключения ассоциативных признаков, блок памяти ассоциативных признаков и коммутатор, причем в каждом блоке сопряжения управляющий вход записи и первый вход опроса блока памяти ассоциативных признаков соединены соответственно с управляющим входом записи признаков и с входом ассоциативных признаков системы для13 1001 подключения информационного процессора и информационным входом коммутатора, управляющий вход которого подключен к дополнительному входу системы для подключения информационного 5 процессора, а выход коммутатора - к информационному входу блока переключения ассоциативных признаков, управляю- ший вход и выход соединены соответственно с управляюшим входом блока перек- О лючения данных и вторым входом опроса блока памяти ассоциативных признаков 07014того же блока сопряжения группы, выходы)процессоров. ввода данных и входы процессоров вывода данных соединены чьрез магистральную шину ассоциативныхпризнаков с входами- выходами фоковпереключения ассоциативных признаков,Источники информации,принятые во внимание при экспертизе1. Патент США Ъ 4065809,кл. 364-200 опублик, 1977.2. Патент США И. 4172283,кл. 364-200, опублик. 1979 (прототип).

СмотретьЗаявка

3262230, 25.12.1980

ПРЕДПРИЯТИЕ ПЯ В-2969

КИРПИЧЕВ ВЛАДИМИР ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 3/04

Метки: данными, информационными, между, обмена, процессорами

Опубликовано: 28.02.1983

Код ссылки

<a href="https://patents.su/14-1001070-sistema-dlya-obmena-dannymi-mezhdu-informacionnymi-processorami.html" target="_blank" rel="follow" title="База патентов СССР">Система для обмена данными между информационными процессорами</a>

Предыдущий патент: Цифровой генератор гармонических функций

Следующий патент: Устройство для обмена информацией

Случайный патент: Способ построения коммутаторов, использующих вращающееся магнитное поле