Система передачи цифровых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1548849

Автор: Сафаров

Текст

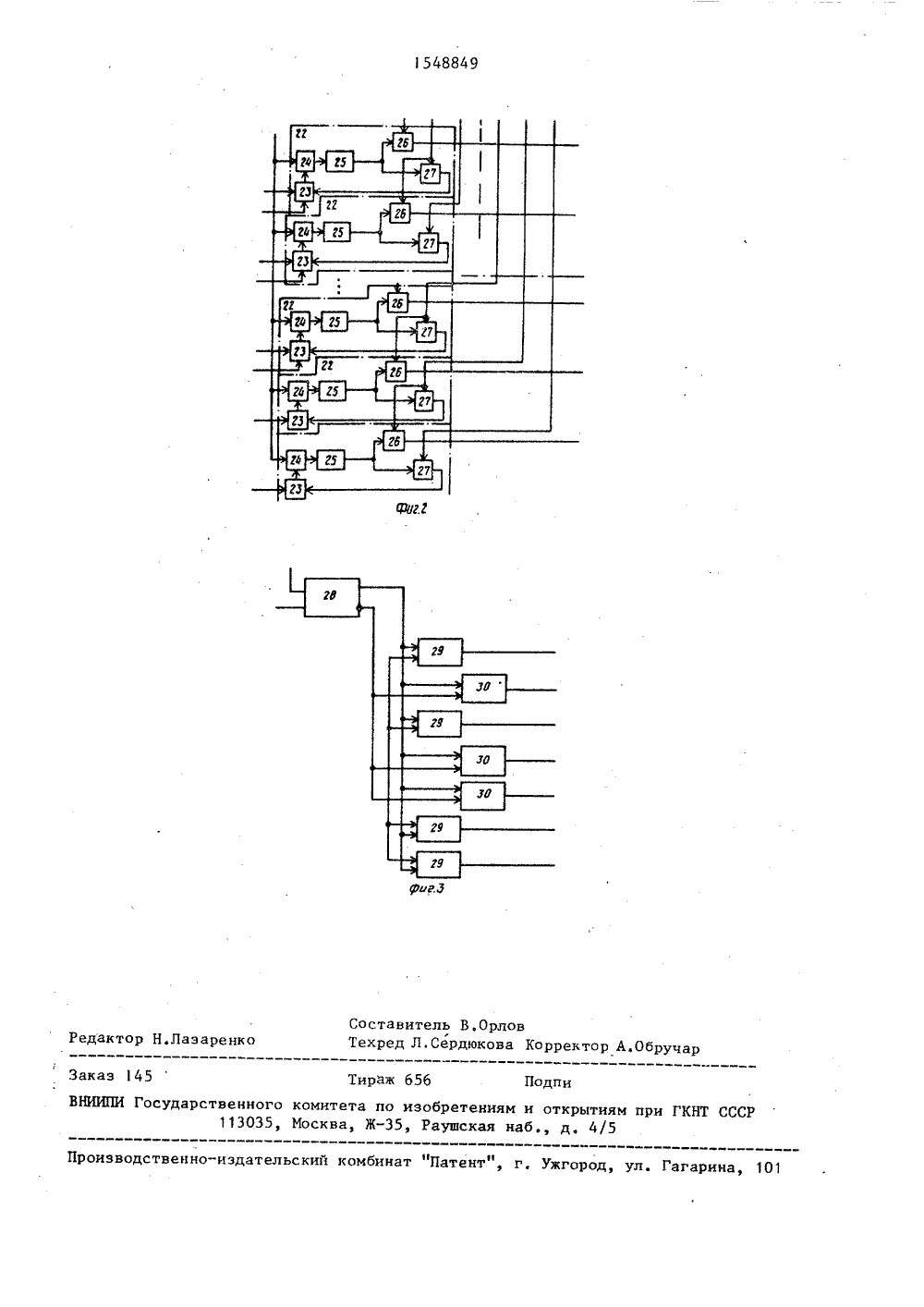

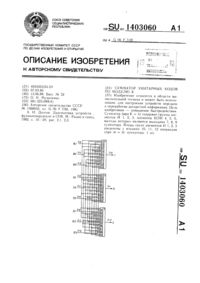

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 1) Н 03 М 13/О ПИСАНИЕ ИЗОБРЕТЕНИЯА ВТОРИЧНОМУ САЙИДЕПЛЬСТВУ ехничес,М.Ь,Бончвы техн щений, -СССР 1982. относится к электроетения - повышение ГОСУДАРСТНЕНН 11 й КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОЖРЬГГИЯМПРИ ГКНТ СССР(71) Ленинградский электрокий институт связи им. проБруевича(56) Шпяпоберский В.И. Оснки передачи дискретных сооМ.: Связь, 1973, с.329.Авторское свидетельство1 091359, кл. Н 04 Ь 1/1 0(54) СИСТЕМА ПЕРЕДАЧИ ЦИФРОВЫХ СИГНАЛОВ,ЯО 1548849 достоверности принимаемых сообщений.Система передачи цифровых сигналов содержит на передающей стороне блок 1 кодирования, преобразователь 2 кода,распределитель 3 импульсов, блок 4 эл-тов ИЛИ-И, блок 5 сумматоров по моду-лю два, г-р 6 эталонного кода, эл-т ИЛИ 7, модулятор 8 и синхронизатор 9, а на приемной стороне - демодулятор 10, регистр 11 сдвига, декодер 12, коррелятор 13, г-р 14 эталонного кода и синхронизатор 15, Цель достигается за счет обнаружения всех ошибок до четвертой кратности и частично ошибой пятой кратностиСистема по пп.2 и 3 и 3 ф-лы отличается .выполнением блока сумматоров 5 и г-ра 6, 2 з,п. ф-лы, 3 ил,Изобретение относится к электросвязи и может быть использовано дляпередачи цифровых сигналовЦелью изобретения является повышение достоверности принимаемыхсообщений за счет обнаружения всехошибок до четвертой кратности и частично ошибок пятой кратности,На Фиг.1 представлена структурнаяэлектрическая схема системы передачицифровых сигналов; на Фиг.2 и 3соответственно структурные электрические схемы блока сумматоров по мо-.дулю два и генератора эталонного кода передающей стороныСистема передачи цифровых сигналов содержит на передающей сторонеблок 1 кодирования, преобразователь2 кода, распределитель 3 импульсов,блок элементов ИЛИ-И 4, блок сумматоров 5 по модулю два, генератор 6эталонного кода, элемент ИЛИ 7, модулятор 8, синхронизатор 9, на приемной стороне демодулятор 10, регистр . 2511 сдвига, декодер 12, коррелятор 3,генератор 14 эталонного кода исинхронизатор 15.Декодер 12 содержит первый 16 ивторой 17 блоки сумматоров, блок30элементов И 18, элемент ИЛИ 19,элемент И 20, инвертор 21,Блок. сумматоров 5 по модулю двасодержит сумматоры 22 по модулю два,которые содержат элемент ИЛИ 23,элемент И 24, счетный триггер 25,второй 26 и третий 27 элементы И.Генератор 6 эталонного кода содержит Б 5-триггер 28, первые элементы И 29 и вторые элементы И 30.Система передачи цифровых сигналовработает следующим образом.Блок 1 кодирования (фиг.1) преобразует дискретные входные сообщенияв К-значные кодовые слова двоичного 45кода. Если входными сообщениями являются последовательности выборок непрерывных сообщений, то блок 1 кодирования выполняет Функции аналогоцифрового преобразователя, На еговыход в первом и втором случаях выдаются К-значные кодовые слова. Дляуправления работой блока 1 кодирования на его вторые входы из синхронизатора подаются синхроимпульсы счастотой слов (1) и с частотой символов (К )Преобразователь 2 преобразует кодовые слова из параллельной формы в последовательную, Он состоит из К элементов И, через которые проходят на выход последовательно все К элементов кодового слова, Сигналы управления в преобразователь 2 поступают из распределителя 3, который состоит из 1 = Е 1 оя и + 1 триггерных ячцк, где Е - целая часть логарифма; тТ - число разрядов кодового слова, включая проверочные элементы, Для рассматриваемого кода (18,9, 5) и=18 и 1=5.Сигналы с первых выходов распределителя 4 поступают на входы блокаэлементов ИЛИ-И 4. Число элементовИЛИ-И равно (и-К+1) = 1 О, где Кчисло необнаруживаемых ошибок, В соответствии с алгоритмом формированияитеративного кода (18, 9, 5) соответствующие входы блока элементов ИЛИ-И4 соединены с соответствующими пер -выми выходами распределителя 3.Информационные элементы кода, число которых К = 9, представлены в виде матрицы.а, а 2 а с,а а а 6 02а., аз азР 2 ЗТам же показаны проверочные элементы0,Мг О в Р ф 121 1Они образуются как суммы по модулю два соответствующих информационных элементовС = а + а 2 + а ,= а + а + а 7- а + а + а 6 ,= а 2 + а + аа + ав + а 9 Р = аЗ + а 6 + а 7- а, + а + + а9Кроме того, вводятся новые диагональные независимые проверкиЯ, = а, + а + аЕ 2. а 2 + а 6+ а 7аз + а.+ авпозволяющие увеличить кодовое расстояние до 5,При введении проверочных элемен- тововф 2 вЗв ;ю /Э 2 ф ф С 1 в С 2 вкодовое расстояние кода становится равным 5, т.е. имеется возможность обнаруживать все 4-кратные ошибки и абсолютное большинство ошибок 5-й кратности. Число необнаруживаемых ошибок 5-й кратности составляет 11 нб = С = К (не обнаруживают" ся ошибки вида 1 о,1,с т.е. При искажениях такого вида ошибка не обнаруживается),1548 1 О Кроме информационных элементов на соответствующий вход каждого сумматора 22 подается один элемент синхрослова из генератора 6. В результате состояние триггера 25 определяет сумму по модулю два укаэанных входных 20 символовГенератор 6 формирует 7-разрядное синхрослово Ь, Ъг, Ьэ, Ь 1, Ь, Ъ Ь Сигналы Ь 1 ЬТ подаются на входы соответствующих сумматоров 22 25 с = аг+ а+ аб+ Ь с =а,+ аб+ач+Ьб с=а+а+а +Ь 7 а, + аг + а + Ь, а + аз + аь + Ьг с а +а +а +Ь с а, +а+а 7+Ь с 4 Ег - ад + а + а 7 С =а+а+а а, агааааа,авас, ссссрссЯ , если= О, а,ааа+ааатавас,сгсссссстЯ: э если=первого блока сумматоров 16. Навход первого сумматора первого блокасумматоров 16 поступают сигналы с 50 выходов 1-й, 2-й, 3-й и 10-й ячеек(при правильной фазировке это будутпосылки а, аг, а и с). Входы второго сумматора первого блока сумматоров 16 соединены с выходами ячеекрегистра 11 с номерами 4, 5, б и11 и т.д а входы десятого сумматора первого блока сумматоров 16 связаны с выходами ячеек регистра 11 с номерами 19. В блоке элементов ИЛИ-И 4 выходы элементов ИЛИ подключены к входам соответствующих элементов И, на вторые входы которых с выхода преобразователя 2 подаются К информационных ПОСЫЛОКИнформационные посылки с выходов блока элементов ИЛИ-И 4 подаются на соответствующие входы блока сумматоров 5 (фиг.2), который содержит одинаковые сумматоры 22, число которых равно (п-К+1) = 1 О. которые образуются на выходе блокасумматоров 5 также поступают посылЭто слово (сигнал) поступает через модулятор 8 в линию связивГенератор 6 выдает кодовое слово 1010011если= 1и 0101100, если= О.На информационный вход демодулятора 10 поступают цифровые радиосигналы. С выхода демодулятора 10 последовательность видеопосылок поступает на вход регистра 11, содержащего и = 18 ячеек. Сигналы с выходов соответствующих ячеек регистра 11 поступают на соответствующие входы 849 6блока сумматоров 5. Так как число проВерочных симВОлОВ и К+11 Оу чис ло сумматоров 22 блока сумматоров 5 также равно 10, то на последние три сумматора 22 подаются только информационные символы.Сигналы о состоянии счетных триггеров 25 ("0" или "1"), соответствующие суммам по модулю два входныхэлементов, считываются импульсами, вырабатываемыми распределителем 3, и поступают на выходы сумматоров 22Выходы девяти сум 49 торов 22 подаются на соответствующие входы элемента ИЛИ 7, а сигнал сумматора 22 поступает на второй дополнительный вход генератора 6. Если этот сигнала+ а г + + а= О, то генератор 7 выдает кодовую комбинацию прямого кода ЬЬЬЬ,1 ЬЬЬ. Если- 1то выдается инвертированная комбинация Ь 1 ЬгЬЪЬЬЬт.На вход линейного сумматора кроме. проверочных символов ки а, ага 9 с выхода преобразователя 2.В результате образуется словоВыходы семи сумматоров первогоблока сумматоров 16 присоединены ксоответствующим вторым входам коррелятора 13 и второго блока сумматоров17, На первые входы коррелятора 13с выхода генератора 14 подается кодовое слово прямого кода Ь, Ъ. ,Ь 7,если на третьем выходе первого блокасумматоров 16 сигнал= О, и кодовое 10слово обратного кода Ь, ЬЬ 7,если= 1Сигналы с двух выходовконтрольных сигналов (первые выходы)первого блока сумматоров 16 поступают на перве входы элемента ИЛИ 19. 15В корреляторе 13 производится вычисление функции взаимной корреляциикодовых слов, вырабатываемых генератором 14, и кодовых слов, получаемыхна вторых выходах первого блока сумматоров 16.11 ри правильной фазе сигнала 1,элемент аразмещен в 1-й ячейкерегистра 11, элемент а - во второй. ячейке и т.д.) выходной сигнал каррелятора 13 имеет максимальное значение.Этот сигнал соответствует главномупику функции взаимной корреляциидвух кодовых сигналов и служит дляобозначения границ слов. Сигнал, 30определяющий момент принятия решенияо правильности поступившего кодовогослова, подается на второй вход элемент И 20. На первый вход элемента.И 20 поступают сигналы с выходаэлемента ИЛИ 16, вторые входы которого соединеНы с соответствующими выходами второго блока сумматоров 17,в котором сравниваются символы синхрокода Ь Ъ,Ь. генератора 14 и 40символы Ь Ь 1,,Ь восстановленного синхрокода,Действительно, элементы восстановленного кодового слова определяютсяследующим образом: 45Ь =а+а +а +са з1 4 4Ъ =а +аз+а+сЬ, =а, +а+а 9+с 74 1Если хотя бы одна.из сумм по моду1 1лю два (,Ь 1 + Ь), (Ь + Ь)(Ь + Ь ) не равна нулю, а такжеХг,1контрольные символы Я = а + аб + а+г.4 Х ( 1 1 4и Я - - а + а + а + ЕЗ такжене равны нулю, то прйнятое кодовоеслово считается ошибочным.На выходе элемента И 20 при этомформируется сигнал запрета, а на блок элементов И 18 не поступает сигнал,который разрешает подать на его выходы информационную часть а аа 9 принятого кодового слова,формула изобретения1,Система передачи цифровых сигналов, содержащая на передающей стороне последовательно соединенные синхронизатор, блок кодирования и преобразователь кода, последовательно соединенные генератор эталонного кода и блок сумматоров по модулю два, а также модулятор, опорный вход которого подключен к второму выходу синхронизатора, а вход генератора эталонного кода подключен к первому выходу синхронизатора, на приемной стороне последовательно соединенные демодулятор, синхронизатор, генератор эталонного кода и коррелятор, выход которого подсоединен к второму входу синх- ронизатора, последовательно соединенные регистр сдвига и декодер, первые выходы которого подсоединены к соответствующим вторым входам коррелятора, выход синхронизатора подсоединен к опорному входу демодулятора и тактовым входам декодера, и регистр сдвига, информационный вход которого подключен к выходу демодулятора, причем входы блока кодирования и вторые выходы декодера являются информационными входом и выходами системы, а выход демодулятора и вход демодулятора являются соответственно канальными выходом и входом системы, о т - л и ч а ю щ а я с я тем, что, с целью повышения достоверности принимаемых сообщений за счет обнаружения всех ошибок до четвертой кратности и частично ошибок пятой кратности, введены на передающей стороне последовательно соединенные распределитель импульсов и блок элементов ИЛИ-И, а также элемент ИЛИ, при этом первый и второй выходы синхронизатора подсоединены соответственно к первому и второму входам распределителя импульсов, вторые выходы которого подсоединены к соответствующим вторым входам преобразователя кода, третьи выходы распределителя импульсов подсоединены к соответствующим вторым входам блока сумматоров по модулю два, третьи входы которо 1 о подключены к соответствующим выходам9 15 блока элементов ИЛИ-И, выходы блока1 сумматоров по модулю два подсоединены через элемент ИЛИ к информационному входу модулятора, объединенные дополнительные входы блока кодирова-ния и блока сумматоров по модулю два и объединенные дополнительные входы блока элементов ИЛИ-И и элемента ИЛИ подключены соответственно к второму выходу синхронизатора и выходу преобразователя кода, первый и второй дополнительные входы генератора эталон.ного кода подключены соответственно к дополнительным выходам распределителя импульсов и блока сумматоров по модулю два, на приемной стороне - дополнительные информационные входы декодера подключены к соответствующим выходам генератора эталонного кода, дополнительный вход которого подключен к первому дополнительному выходу декодера, причем второй дополнительный выход декодера является дополнительным выходом системы, при этом декодер содержит последовательно соединенные первый блок сумматоров по модулю два, элемент ИЛИ, элемент И, инвертор и блок элементов И, другие входы которого подключены к соответствующим входам первого блока сумматоров по модулю два, а также второй блок сумматоров по модулю два, первые входы которого подключены к соответствующим вторым выходам первого блока сумматоров по модулю два, выходы второго блока сумматоров по модулю два подсоединены к соответствующим вторым входам элемента ИЛИ, причем входы первого блока сумматоров по модулю два и вторые входы второго блока сумматоров по модулю два, вторые выходы первого блока сумматоров по модулю два, выходы блока элементов И, третий выход первого блока сумматоров по модулю два и выход элемента И являются соответственно информационными входами, дополнитель 48849 10ными информационными входами, первыми и вторыми выходами и первым и вторым дополнительными выходами декодера,.У2.Система по п,1, о т л и ч а ю -щ а я с я тем, что на передающейстороне блок сумматоров по модулю двасодержит сумматоры по модулю два,причем первые, вторые, третьи входы,объединенные четвертые входы и выходысумматоров по модулю два являютсясоответственно первыми, вторыми итретьими входами, дополнительнымвходом и выходами блока сумматоров помодулю два, а каждый из сумматоров .-по модулю два состоит из последовательно соединенных элемента ИЛИ, первого элемента И, счетного триггера20 и второго элемента И, а также третьего элемента И, первый вход и выходкоторого подключены соответственнок прямому выходу счетного триггераи первому входу элемента ИЛИ, при25 этом второй вход элемента ИЛИ, вторые входы второго и третьего элементов И, третий вход элемента ИЛИ ивторой вход первого элемента И ивыход второго элемента И являютсясоответственно первым, вторым,третьим и четвертым входами и выходомсумматора по модулю два,З.Система по п,1, о т л и ч а ющ а я с я тем, что на передающейстороне генератор эталонного кода со 35держит КБ-триггер и первые и вторыеэлементы И, первые объединенные входыпервых элементов И и первые объединенные входы вторых элементов И под 40 ключены соответственно к прямому иинверсному выходам КБ-триггера, причем Б-вход и К-вход КБ-триггера,объединенные вторые входы первых ивторых элементов И, а также выходыпервых и вторых элементов И являютсясоответственно входом, первым и вторым дополнительными входами.и выходами генератора эталонного кода.1548849 Составитель В,ОрловТехред Л.Сердюкова К Лазаренк едак ор А,Обруча аказ 145 ираж 65 б одпи НИИПИ суд обретен а Производственно-издательский комбинат "Патент", г, Ужгород, ул, Г твенного к 113035, М итета по ква, Жм и открытиям при ГКНТ СССРнаб., д. 4/5

СмотретьЗаявка

4285101, 17.07.1987

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

САФАРОВ РИЗА ТАДЖИЕВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: передачи, сигналов, цифровых

Опубликовано: 07.03.1990

Код ссылки

<a href="https://patents.su/6-1548849-sistema-peredachi-cifrovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи цифровых сигналов</a>

Предыдущий патент: Устройство нисневича для контроля двоичной информации

Следующий патент: Компенсатор помех

Случайный патент: Газоочиститель