Параллельный сумматор на феррит-транзисторных модулях

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 277409

Автор: Болдырев

Текст

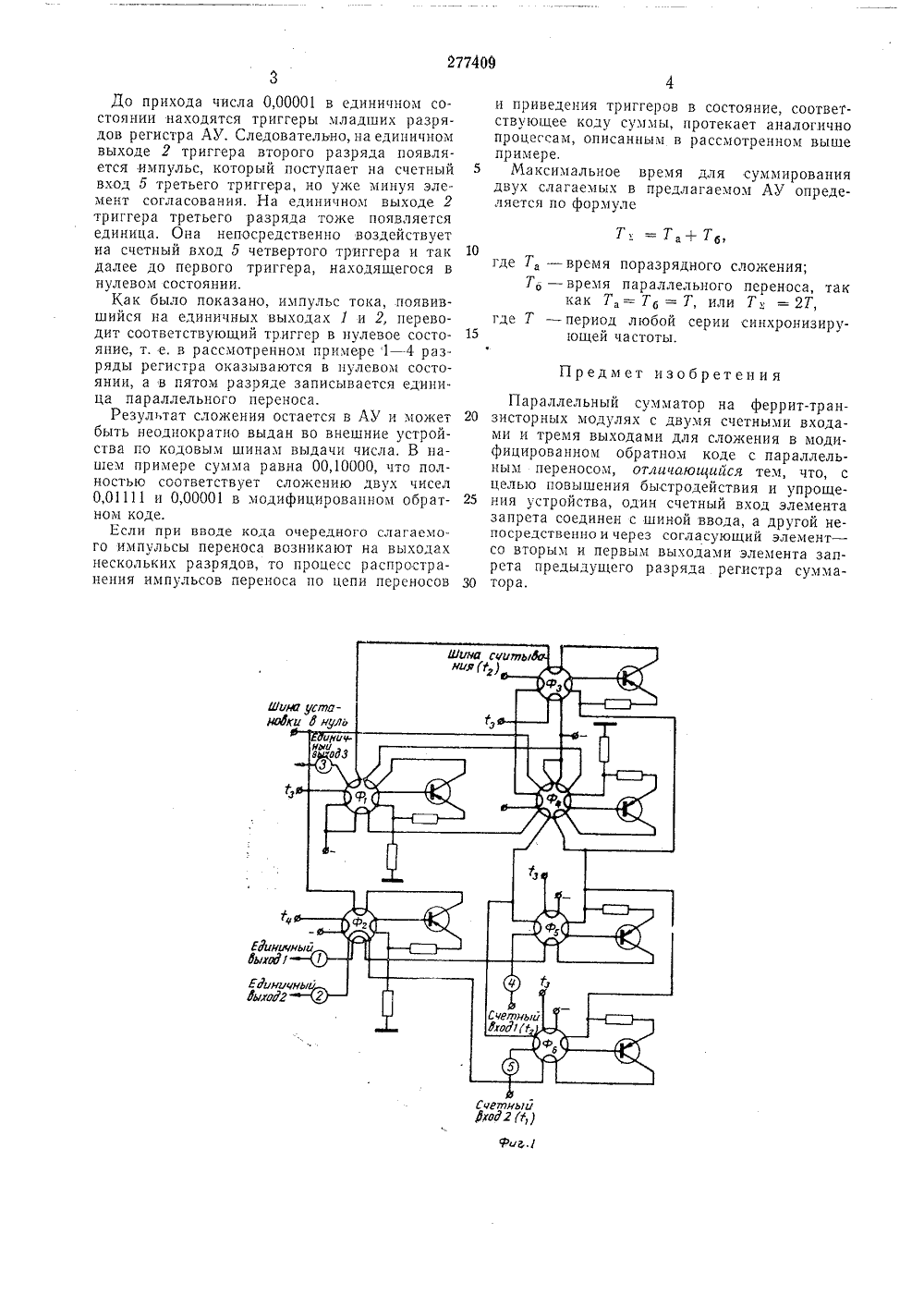

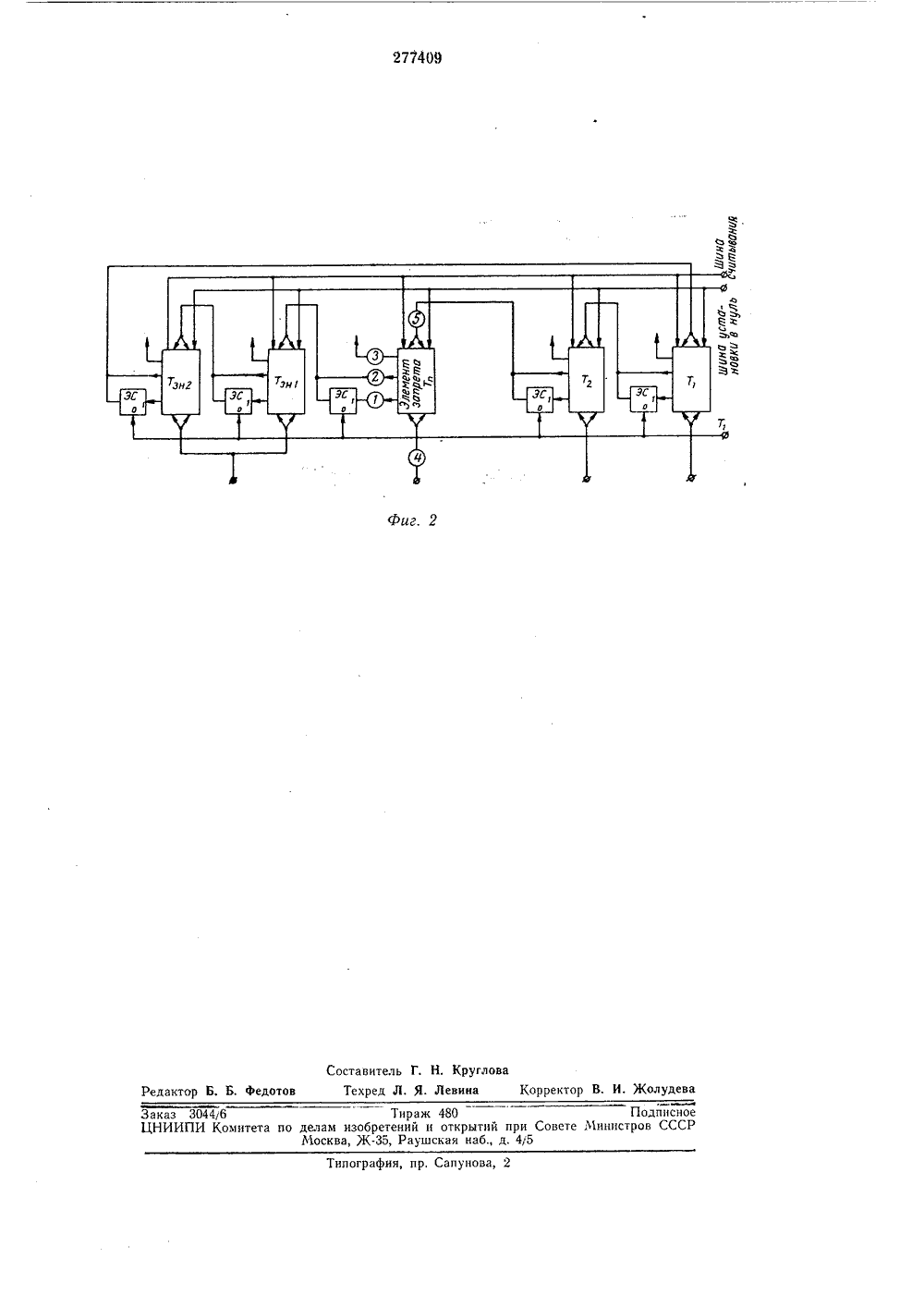

ОП САНИ Е 222409ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Республик Зависимое от авт. свидетельства04,1 Ч.1969 (М 1317437118 Заявлен л. 42 тп, 7 гнением заявкис прис омитет по делам МПК 6 061 г/50УДК 681.325,54(088,8 Приори етеиий и открытийСовете Министров Опублик ано 22.Ч 1.1970. Бюллетеньликования описания З.Х 1.1970 Дат Авторизобретения И, Бо,пдыр витель ПАРАЛЛЕЛЬНЪЙ СУММНА ФЕРРИТ-ТРАНЗИСТОРНЫХ ЛЯХ записано число 0,01111, к котоимо прибавить число 0,00001. агаемое подается синхронно с и поступлении числа 0,00001 на ввода слагаемых триггер млад- регистра АУ переключается, и ном выходе 1 появляется сигнал.на элементе согласования до диого такта, этот сигнал постуараллсльцого переноса, т. е. на 5 триггера второго разряда. При ается схема совпадения на мое этого триггера. Пусть в АУ рому необход д Очередное сл тактом 1 в. Пр кодовые шинь шего разряда на его единич 5 Задержавшись прихода очере пает в цепь п счетный вход этом опрашив О дулях Ф 4 и Фия Данное устроиство относится к вычислительной технике.Известны параллельные сумматоры на феррит-транзисторных модулях, содержащие регистры суммы, схемы переноса, вентили. В этих устройствах сигнал с выхода каждого разряда регистра суммы подается в последующий разряд через вентиль на счетный вход триггера, куда подсоединена и шина ввода.Описываемый сумматор отличается тем, что в нем один счетный вход элемента запрета соединен с шиной ввода, другой непосредственно и через согласующий элемент - со вторым и первым выходами элемента запрета предыдущего разряда регистра сумматора, Это позволяет повысить быстродействие и упростить устройство.На фиг. 1 приведена принципиальная схема триггера; на фиг. 2 - блок-схема сумматора,В схеме на фиг, 1 триггер содержит шесть феррит-транзисторных модулей (ФТМ), Модули Ф, и Фв являются согласующими. На модулях Фв - Фв выполнен элемент запрета с тремя выходами, в состав которого входят три логические схемы И, имеющие общий ФТМ (Ф 4) с обмоткой запрета.Единичный выход 1 используется для реализации функции Р=АВ, где А и В - одноименные разряды слагаемых, Р - импульс переноса; единичный выход 2 - для построен цепи параллельного переноса, единичный выход т - для выдачи результата сложения,Работа триггера синхронцзируется четырьмя последовательными тактами 1, - 14.5 Арифметическое устройство (АУ) ца фиг, 2,состоящее из и + 2 статических триггеров, содержит цепь циклического переноса, шинуустановки в нуль, шину считывания, и + 1шину ввода слагаемых ц и+ 1 шину выдачиО результатов сложения. На схеме изображены: Тт - Тзн - триггеры - элементы запрета; ЭС - элемент согласования; 1 - 3 - единичные выходы элемента запрета; 4,5 - счетные входы элемента запрета,5 Рассмотрим работу АУ на примере сложенцядвух чис 1= Т,+ Т Шина ноФк б 3 и йи Единцц ЬаЫг Счетныи Додг 9,Уцг. До прихода числа 0,00001 в единичном состоянии находятся триггеры младших разрядов регистра АУ. Следовательно, на единичном выходе 2 триггера второго разряда появляется импульс, который поступает на счетный вход 5 третьего триггера, но уже минуя элемент согласования. На единичном выходе 2 триггера третьего разряда тоже появляется единица. Она непосредственно воздействует на счетный вход 5 четвертого триггера и так далее до первого триггера, находящегося в нулевом состоянии.Как было показано, импульс тока, появившийся на единичных выходах 1 и 2, переводит соответствующий триггер в нулевое состояние, т. е. в рассмотренном примере 1 - 4 разряды регистра оказываются в нулевом состоянии, а в пятом разряде записывается единица параллельного переноса.Результат сложения остается в АУ и может быть неоднократно выдан во внешние устройства по кодовым шинам выдачи числа. В нашем примере сумма равна 00,10000, что полностью соответствует сложению двух чисел 0,01111 и 0,00001 в модифицированном обратном коде.Если при вводе кода очередного слагаемого импульсы переноса возникают на выходах нескольких разрядов, то процесс распространения импульсов переноса по цепи переносов и приведения триггеров в состояние, соответствующее коду суммы, протекает аналогично процессам, описанным в рассмотренном выше примере.5 Максимальное время для суммированиядвух слагаемых в предлагаемом АУ определяется по формуле 10 где Т, - время поразрядного сложения; Т, - время параллельного переноса, так как Т,= Тб = Т, или Т. =2 Т,где Т - период любой серии синхронизиру 15 ющей частоты, Предмет изобретения Параллельный сумматор на феррит-тран зисторных модулях с двумя счетными входами и тремя выходами для сложения в модифицированном обратном коде с параллельным переносом, отличающийся тем, что, с целью повышения быстродействия и упроще ния устройства, один счетный вход элементазапрета соединен с шиной ввода, а другой непосредственно и через согласующий элемент - со вторым и первым выходами элемента запрета предыдущего разряда. регистра сумма тора.277409Фиг. 2Составитель Г. Н. Круглова Редактор Б, Б. федотов Техред Л, Я. Левина Корректор В. И Жолудева Заказ 3044(6 Тираж 480 ПодписноеЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССРМосква, Ж, Раушская иаб., д. 4/5Типография, пр. Сапунова, 2

СмотретьЗаявка

1317437

А. И. Болдырев

МПК / Метки

МПК: G06F 7/50

Метки: модулях, параллельный, сумматор, феррит-транзисторных

Опубликовано: 01.01.1970

Код ссылки

<a href="https://patents.su/3-277409-parallelnyjj-summator-na-ferrit-tranzistornykh-modulyakh.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный сумматор на феррит-транзисторных модулях</a>

Предыдущий патент: Устройство для вычисления среднего арифметического

Следующий патент: Устройство для отладки программ

Случайный патент: Устройство для количественного учета посетителей музеев, выставок и т. п.