Устройство для сопряжения процессоров через общую память в многопроцессорной системе

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

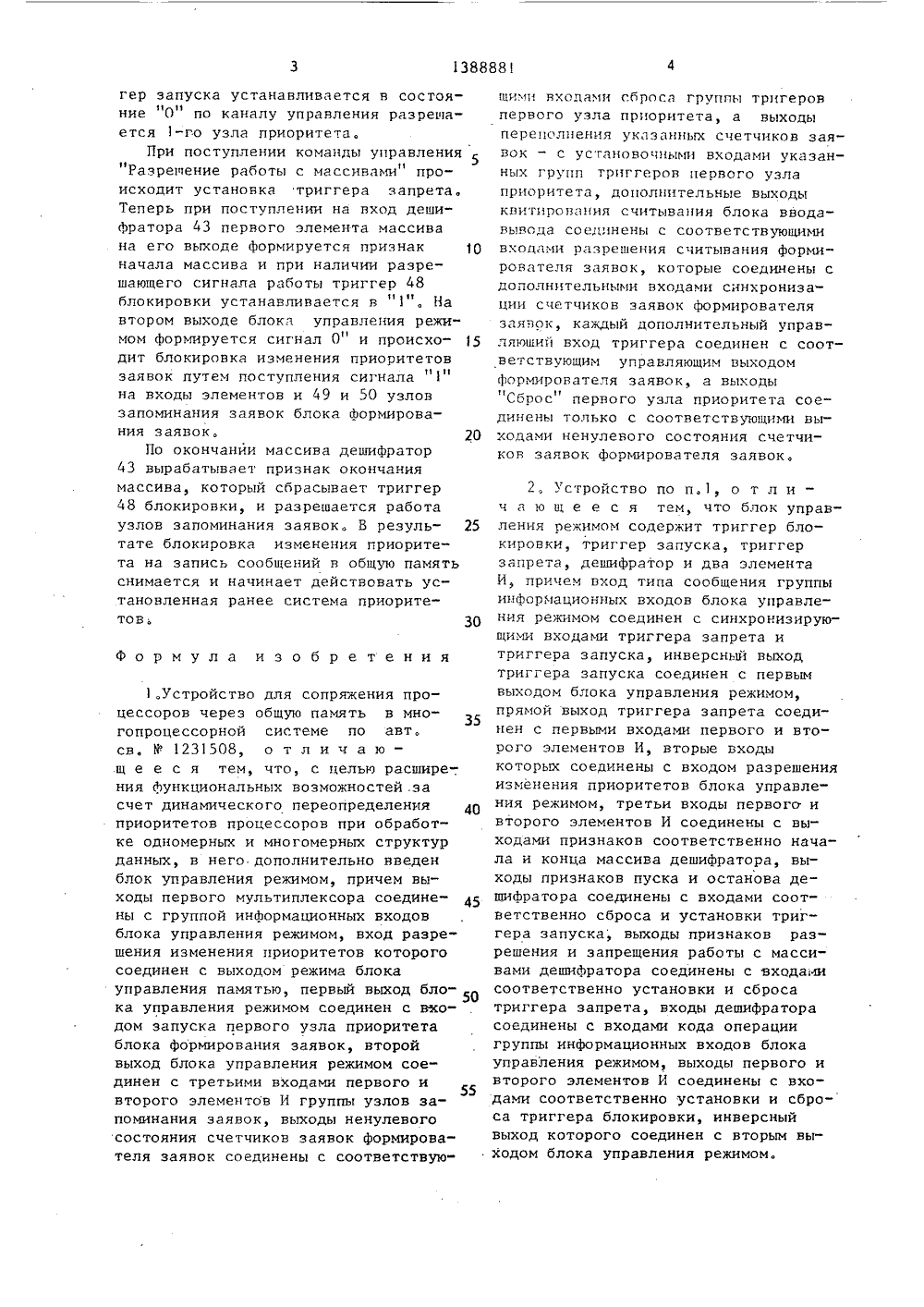

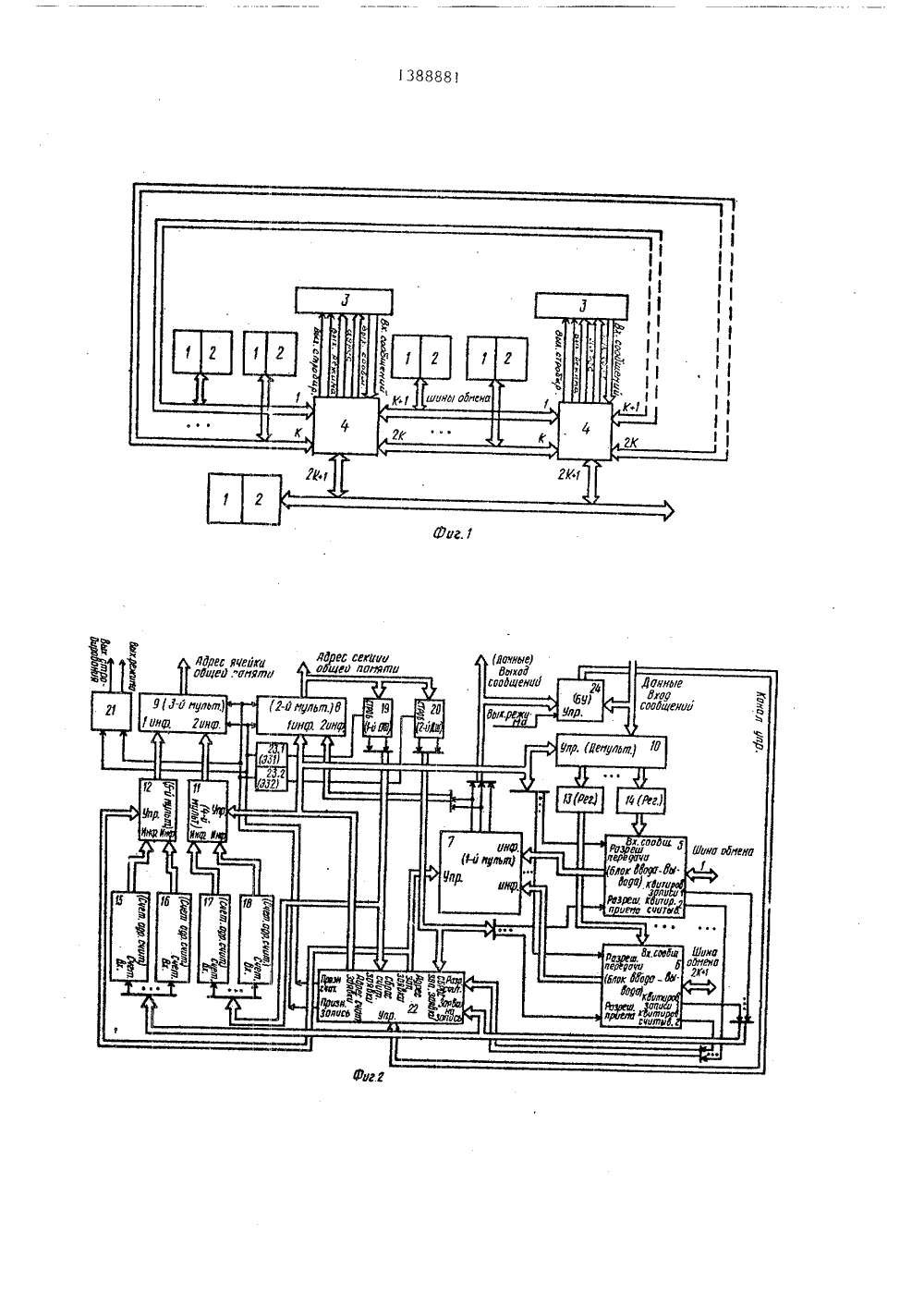

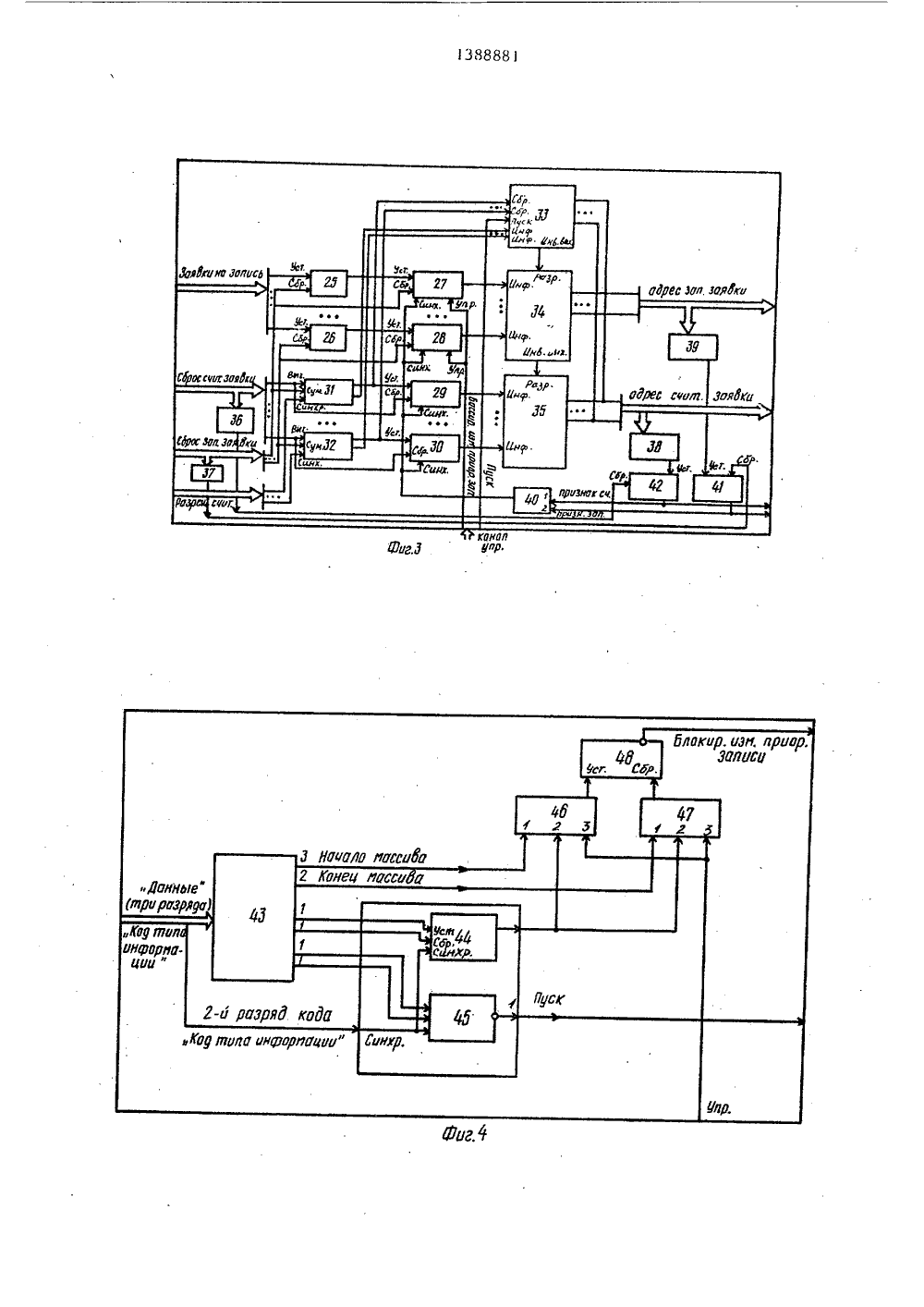

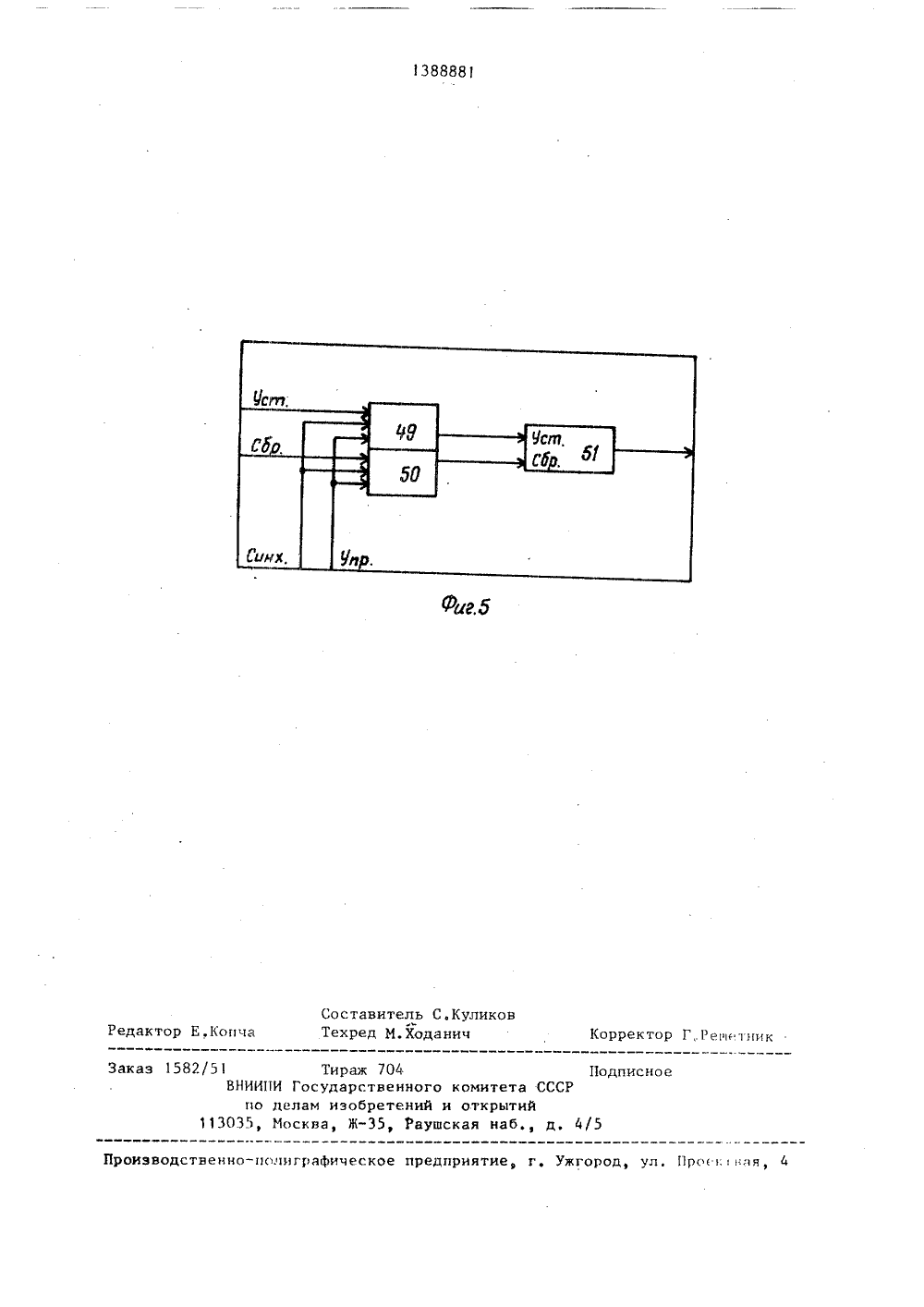

(19) А 2 51) 4 С 06 Г 15/1 ОПИСАНИЕ ИЗОБРЕТЕН У СВИДЕТЕЛЬСТВУ АВТОРС ельство СССР 15/16, 1986, ОПРЯЖЕНИЯ ПРОПАМЯТЬ В ИНОГО лас бытьых модуУДАРСТВЕННЫЙ НОМИТЕТ ССДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ(54) УСТРОЙСТВО ДЛЯ СЦЕССОРОВ ЧЕРЕЗ ОБ 01 У 10ПРОЦЕССОРНОЙ СИСТЕМЕ(57) Изобретение относится к овычислительной техники и можЕтиспользовано в автоматизировансистемах управления в качествеля обработки информации. Целью ретения является расширение функциональных возможностей за счет динамического переопределения приоритетовпроцессоров при обработке одномерныхи многомерных структур данных. Дляэтого в микропроцессорную систему,содержащую микропроцессоры, оперативные запоминающие устройства, общие оперативные запоминающие устройства, устройства для сопряженияпроцессоров через общую память, дополнительно введен блок управлениярежимом, состоящий из дешифратора,триггера запрета, триггера запускапервого и второго элементов И итриггера блокировки. 1 з.п. ф-лы,5 ил138888 Номер получателя сообщений (Р процессора, ЭВМ) - 8 бит Код типа Данныеинформа- (8 бит)ции(3 бита) Номер отправителя сообщения (9 процессора, ЭВМ) - 5 бит Изобретение относится к вычислительной технике, может быть использовано в автоматизированных системах управления в качестве модуля обработки информации и является дополнительным к авт.св, У 1231508.Целью изобретения является расширение функциональных возможностей за счет динамического переопределения приоритетов процессоров при обработке одномерных и многомерных структур данных,На фиг, изображена блок-схема многопроцессорной системы с использованием устройства для сопряжения процессоров; на фиг,2 - структурная схема устройства для сопряжения процессоров через общую память; на фиг.З - функциональная схема блока формирования заявок; на фиг, 4 - функциональная схема блока управлейия режимом; на фиг,5 - функциональная схема узла запоминания заявок.Предлагаемое устройство содержит микропроцессоры 1, один из которых центральный, местные оперативные запоминающие устройства, (ОЗУ) 2, общие оперативные запоминающие устройства 3, устройство 4 для со- пряжения процессоров через общую йамять, содержащее первый блок 5 ввода-вьвода, (2 К+1)-й блок 6 ввода-вьвода, первый 7, второй 8 и третий 9 мультиплексоры, демультиплексор О, четвертый 11 и памяти 12 мультиплексоры, первый регистр 13, (2 К+1)-й регистр 14, первый счетчик 15 адреса считьвания (2 К+1)-й счетСамостоятельно блок управления режимом не может обеспечить непрерывное считывание сообщений из общей памяти, так как это осуществляется автоматически под управлением блока формирования заявок, Задача блока управления режимом состоит в том, чтобы принять адресуемое ему сообщение (признаки код тяпа информации и данные") и проанализировать коды, содержащиеся в них, Факт необходимости анализа признака данные определяется приемом кодов 010, 011,110,5 1 О 15 20 25 30 35 чик 16 адреса считывания, первыйсчетчик 17 адреса записи, (2 К+1)-йсчетчик 18 адреса записи, первый 19и второй 20 дешифраторы, блок 21управления памятью, блок 22 формирования заявок, первый 23,1 и второй23,2 элементы задержки, блок 24управления режимом.Блок формирования заявок содержитпервый триггер 25 первой группы,(2 К+1)-й триггер 30 второй группы,первый счетчик 31 заявок, (2 К+1)-йсчетчик 32 заявок, первый 33, второй34 и третий 35 узлы приоритета, первый 36, второй 37, третий 38, четвертый 39 и пятый 40 элементы ИЛИ,триггеры 41 и 42.Блок управления режимом содержитдешифратор 43, триггер 44 запрета,триггер 45 запуска, первый 46 и второй 47 элементы И, триггер 48 блокировки,Узел запоминания заявок содержит первый 49 и второй 50 элементыИ, триггер 51.Устройство функционирует следующим образом.Функционирование блока управленияфрежимом происходит под действием сигналов, сформированных в управляющейчасти форматов сообщений, передаваемых по выходу "Выход сообщений" устройства в общую память. Формат этихсообщений следующий: 111 в признаке "код типа информации",Команда управления Начало масива в виде кода 111 ХХХХХ содержится в трехпервых разрядах признака Данные1 команда управления "Конец массива в виде кода ОООХХХХХ, команда управления "Пуск" - в виде кода 110 ХХХ,а команда управления Стоп - в виде кода 101 ХХХХ с запоминанием в триггере запуска.Устройство начинает работать после того, как на блок управления режи мом поступает команда Пуск . Триг 138888гер запуска устанавливается в состояние 0 по каналу управления разрешается 1-го узла приоритета.При поступлении команды управления 5 "Разрешение работы с массивами" происходит установка триггера запрета. Теперь при поступлении на вход дешифратора 43 первого элемента массива на его выходе формируется признак 10 начала массива и при наличии разрешающего сигнала работы триггер 48 блокировки устанавливается в "1", На втором выходе блока управления режимом формируется сигнал 0 и происхо дит блокировка изменения приоритетов заявок путем поступления сигнала 1на входы элементов и 49 и 50 узлов запоминания заявок блока формирования заявок,По окончании массива дешифратор 43 вырабатывает признак окончания массива, который сбрасывает триггер 48 блокировки, и разрешается работа узлов запоминания заявок. В резуль тате блокировка изменения приоритета на запись сообщений в общую память снимается и начинает действовать установленная ранее система приоритетов, 30 20 Формула изобретения 1,устройство для сопряжения процессоров через общую память в многопроцессорной системе по авт. св. 9 1231508, о т л и ч а ю - .щ е е с я тем, что, с целью расширения функциональных возможностей .эа счет динамического переопределения 40 приоритетов процессоров при обработке одномерных и многомерных структур данных, в него дополнительно введен блок управления режимом, причем выходы первого мультиплексора соединены с группой информационных входов блока управления режимом, вход разрешения изменения приоритетов которого соединен с выходом режима блока управления памятью, первый выход блока управления режимом соединен с входом запуска первого узла приоритета блока формирования заявок, второй выход блока управления режимом соединен с третьими входами первого и второго элементов И группы узлов запоминания заявок, выходы ненулевого состояния счетчиков заявок формирователя заявок соединены с соответствуюшими входами сброса группы тригеров первого узла приоритета, а выходы переполнения указанных счетчиков заявок - с установочными входами указанных групп триггеров первого узла приоритета, дополнительные выходы квитирования считывания блока ввода- вывода соединены с соответствующими входами разрешения считывания формирователя заявок, которые соединены с дополнительными входами синхронизации счетчиков заявок формирователя заявок, каждый дополнительный управляющий вход триггера соединен с соответствующим управляющим выходом формирователя заявок, а выходы Сброс первого узла приоритета соединены только с соответствующими выходами ненулевого состояния счетчиков заявок формирователя заявок. 2, Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок управления режимом содержит триггер блокировки, триггер запуска, триггер запрета, дешифратор и два элемента И, причем вход типа сообщения группы информационных входов блока управления режимом соединен с синхронизирующими входами триггера запрета и триггера запуска, инверсный выход триггера запуска соединен с первым выходом блока управления режимом, прямой выход триггера запрета соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с входом разрешения изменения приоритетов блока управления режимом, третьи входы первого и второго элементов И соединены с выходами признаков соответственно начала и конца массива дешифратора, выходы признаков пуска и останова дешифратора соединены с входами соответственно сброса и установки триггера запуска, выходы признаков разрешения и запрещения работы с массивами дешифратора соединены с входами соответственно установки и сброса триггера запрета, входы дешифратора соединены с входами кода операции группы информационных входов блока управления режимом, выходы первого и второго элементов И соединены с входами соответственно установки и сброса триггера блокировки, инверсныйвыход которого соединен с вторым выходом блока управления режимом.

СмотретьЗаявка

4070680, 04.03.1986

ПРЕДПРИЯТИЕ ПЯ Г-4746

ЕРЗАКОВ ЕВГЕНИЙ МИХАЙЛОВИЧ, ГОЛОВИН ВИКТОР ИВАНОВИЧ, ДЕНИЩЕНКО ИГОРЬ ЯКОВЛЕВИЧ, КРАВЧЕНКО ТАТЬЯНА ИВАНОВНА

МПК / Метки

МПК: G06F 15/167

Метки: многопроцессорной, общую, память, процессоров, системе, сопряжения

Опубликовано: 15.04.1988

Код ссылки

<a href="https://patents.su/6-1388881-ustrojjstvo-dlya-sopryazheniya-processorov-cherez-obshhuyu-pamyat-v-mnogoprocessornojj-sisteme.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сопряжения процессоров через общую память в многопроцессорной системе</a>

Предыдущий патент: Устройство для сопряжения электронно-вычислительной машины с внешним устройством

Следующий патент: Устройство для сопряжения

Случайный патент: Гвоздь для остеосинтеза