Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1367156

Авторы: Абложавичюс, Березовский, Валах, Григорьев, Данилевич

Текст

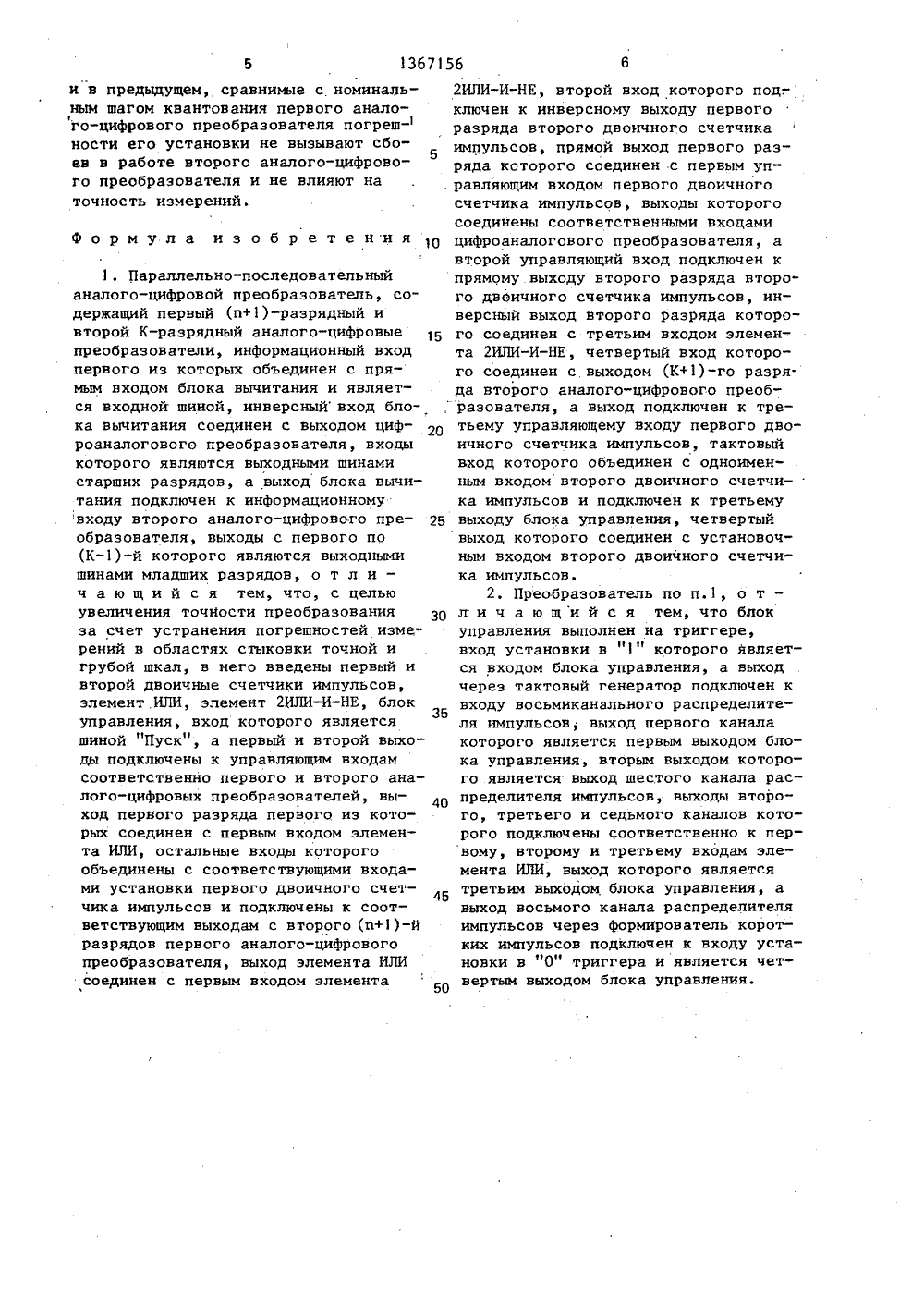

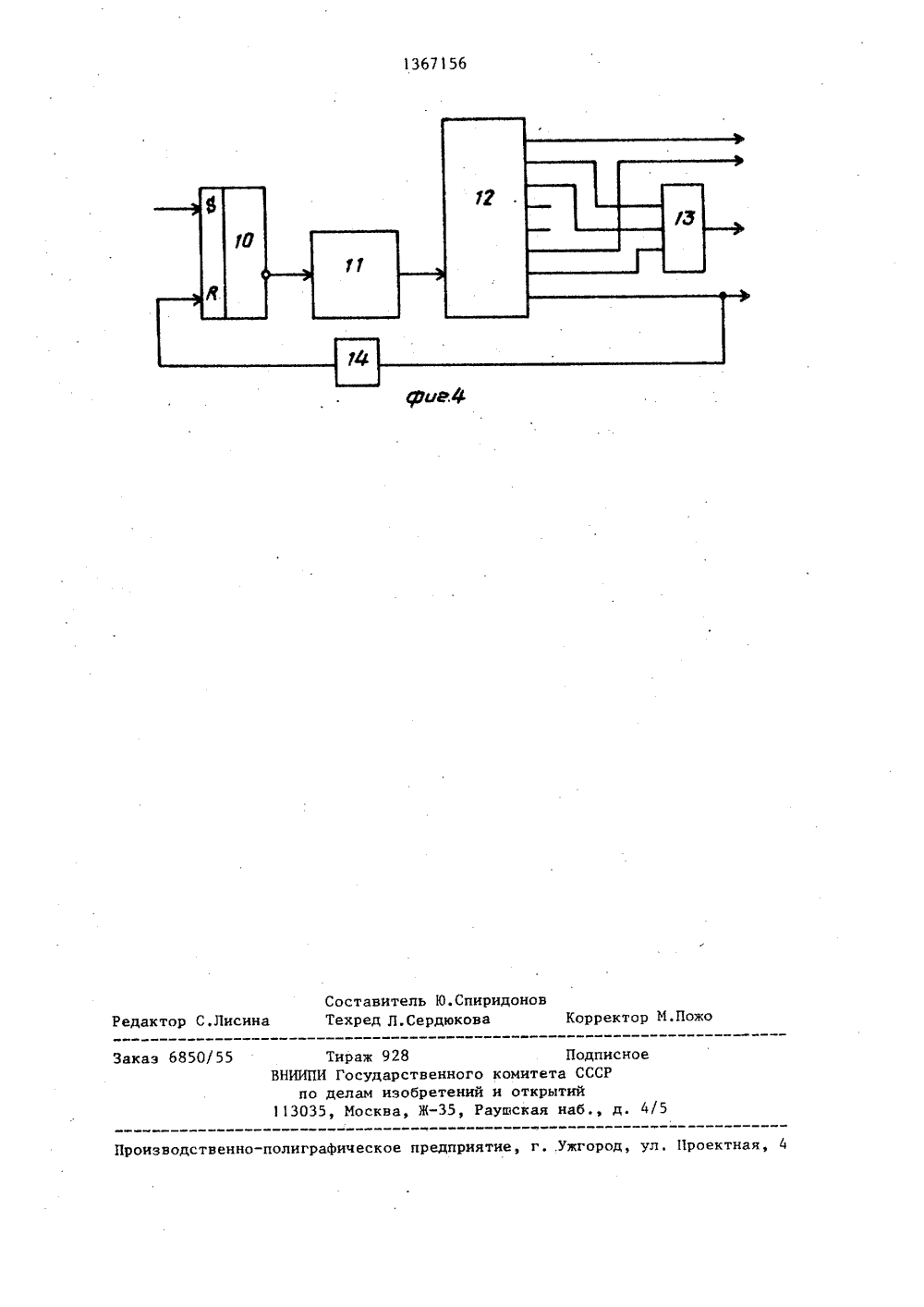

(46) 15.01.88. Бю71 На но-иссле тию" ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ОПИСАНИЕ ИЗО ВТОРСНОМУ СВИДЕТЕЛЬСТВ л.92( ) уч довательский инс тут прикладных физических проблем А.Н.Севченко и Вильнюсский завод электроизмерительной техники(56) Гольденберг Л.М., Бутыньский Н.Т Поляк. М.Н. Цифровые устройства на ин тегральных схемах в технике связи. М.: Связь, 1979, с. 96, рис. 4.11;Бахтиаров Г,Д Малинин В.В., Школин В.П. Аналого-цифровые преобра зователи. М.: Сов. радио, 1980, с. 31.(57) Изобретение относится к информационно-измерительной технике и может использоваться в радиолокации,экспериментальной физике, автоматикеи телемеханике. В устройство, содержащее первый и второй аналого-цифровые преобразователи 1 и 2, цифроаналоговый преобразователь 3 и блок 4вычитания, с целью устранения грубыхпогрешностей измерений в областяхстыковки точной и грубой шкал двухшкального аналого-цифрового преобразователя при одновременном снижениитребований к точности первого аналого-цифрового преобразователя, введены первый и второй двоичные счетчики1367156 5 и 8 импульсов, элемент ИЛИ 6, элемент 2 ИЛИ-И-НЕ 7 и блок 9 управления.Введение в параллельно-последовательный аналого-цифровой преобразовательперечисленных выше узлов с соответствующими связями обеспечивает такоефункционирование устройства, при коИзобретение относится к контроль-но-измерительной технике и может ис-.пользоваться в радиолокации, телевидении, экспериментальной физике, автоматике и телемеханике.Цель изобретения - устранение грубых погрешностей измерений в областях стыковки точной и грубой шкалдвухшкального аналого-цифрового преобразователя при одновременном снижении требований к точности первогоаналого-цифрового преобразователя,На фиг,1 изображена структурнаясхема двухшкального аналого-цифрово-,го преобразователя; на фиг.2 и 3диаграммы, поясняющие работу устройства; на фиг.4 - структурная схемаблока управления,Преобразователь содержит первый ивторой аналого-цифровые преобразователи 1 и 2, цифроаналоговый преобразователь 3, блок 4 вычитания, первый двоичный счетчик 5, логическийэлемент ИЛИ 6, логический элемент2 ИЛИ-И-НЕ 7, второй двоичный счетчик8, блок 9 управления. Блок управления выполнен на триггере 10, тактовом генераторе 11, восьмиканальномраспределителе 12 импульсов, элементе ИЛИ 13, формирователе 14 короткихимпульсов.Процесс кодирования входного напряжения начинается по сигналу "Пуск"10, поступающему на вход блока 9 уп- .равления. По этому сигналу блок управления вырабатывает серию управляющих сигналов 11-14. Сигналом 11 сего первого выхода осуществляетсястробирование первого аналого-цифрового преобразователя 1, и на выходепоследнего появляется пропорциональный входному напряжению двоичный код,все разряды которого, кроме младшегб,тором сигнал с вычитающего устройства не выходит за пределы рабочего .диапазона второго аналого-цифровогопреобразователя, что позволяет полностью исключить грубые ошибки измерений на участках стыковки грубой иточной шкал, 1 з.п. ф-лы, 4 ил,подаются на информационные входы двоичного счетчика 5. По окончании цикла работы первого аналого-цифровогопреобразователя первым сигналом 12с третьего выхода блока 9 управленияпроисходит занесение полученного кода в счетчик 5 и переключение в единичное состояние двухразрядного дво ичного счетчика 8, который прямымвыходом первого разряда переводитпервый двоичный счетчик 5 в режимвычитания, а инверсным выходом первого разряда разблокирует первую по ловину логического элемента 7. Есливыходной сигнал элемента 6 имеет низкий уровень, что соответствует нулевому коду первого аналого-цифровогопреобразователя, сигнал высокого 20 уровня с элемента 7 блокирует операцию счета в счетчике 5, Если код аналого-цифрового преобразователя 1 ненулевой, вторым сигналом 12 с третьего выхода блока управления из ко да, записанного в счетчик 5, вычитается единица, Этим же сигналом всчетчик 8 добавляется единица и онустанавливает код, равный двум. Врезультате на управляющих входах 30 счетчика 5 устанавливаются потенциалы, соответствующие режиму сложения(нуль - на первом управляющем входеи единица - на втором). Через определенное время, необходимое для завершения переходных процессов, в цифроаналоговом преобразователе 3 и блоке 4 вычитания по сигналу 13 с второго выхода блока управфо ления осуществляется запуск второгоаналого-цифрового преобразователя 2, на выходе которого появляется код, представляющий собой точные разряды выходного кода устройства. Если ре1367156 зультат преобразования аналого-цифрового преобразователя 2 содержит в старшем"(К+1)-м разряде единицу, элемент 7 переводит счетчик 5 в режим сложения и третьим сигналом 12 с третьего выхода блока 9 управления осуществляется операция добавления единицы в грубый код, записанный ранее в счетчик 5. При нулевом состоянии 10 старшего разряда аналого-цифрового преобразователя 2 сигналом высокого уровня с выхода элемента 7 эта операция по первому управляющему входу счетчика 5 блокируется. Указанный ал горитм фактически осуществляет операцию суммирования содержимого старшего разряда второго аналого-цифрового преобразователя с грубым кодом, полученным на первом этапе измерений. 20Введение в двухшкальный аналогоцифровой преобразователь перечисленных узлов с соответствующими связями позволяет исключить грубые ошибки измерений на участках стыковки грубой 25 и точной шкал и значительно снизить требования к точности первого из входящих в него одношкальных аналогоцифровых преобразователей. С их помощью обеспечивается такое функциони- ЭО рование устройства, при котором уровень сигнала вычитающего устройства не выходит за пределы рабочего диапазона второго аналого-цифрового преобразователя, соответствующего двум единицам младшего разряда грубой шкалы, даже при больших отклонениях от номинальных параметров основных узлов устройства. Предположим, что цифроаналоговый 40 преобразователь, вычитающее устройство и второй аналого-цифровой преобразователь являются идеальными и не вносят погрешностей. Пусть (2 д+1)-й нечетный уровень квантования первого 45 аналого-цифрового преобразователя установлен с отрицательной погрешностью д 11 +1 (фиг.4), а измеряемый уровень напряжения Б лежит между его (2 д+1)-й и (2 д+2)-м уровнями 50 квантования. Тогда в соответствии с рассмотренным алгоритмом работы устройства в результате отбрасывания младшего разряда в выходном коде первого аналого-цифрового преобразовате ля на вход вычитающего устройства поступает разностный сигнал д Б = . = 08 - П;, где П; - уровень напряжения цифроаналогового преобразователя, соответствующий идеальному положению 2-го узла шкалы первого аналого-цифрового преобразователя. Очевидно Ь Б в этом случае может обратиться в нуль только тогда, когдаЦ 7 = П 2 т.е. абсолютная погрешность установки шага квантования первого аналого-цифрового преобразователя в пределе может быть сравнима сего номинальным значением или с половиной грубого шага квантования всего устройства. Очевидно также, что это условие легко может быть удовлетворено практически, в отличие от требования к абсолютной погрешности первогоаналого-цифрового преобразователя в прототипе, где она должна быть меньше шага квантования по точной шкале.Аналогично укаэанному малые откло.нения от номинала положений узлов шкалы цифроаналогового преобразователя, а также небольшие систематические погрешности обоих знаков устройства вычитания и второго аналого-цифрового преобразователя не нарушают нормальной работы предлагаемого устройства и не вызывают грубых погрешностей в результате измерений. Наличие систематических адцитивных погрешностей в цифроаналоговом преобразователе и суммирующем устройстве проявляется в смещении порога суммарной функции преобразования, которое может быть легко скорректировано известными методами.Рассмотрим вторую крайнюю ситуацию, в которой в известном устройстве возможно нарушение нормального функционирования второго аналого-цифрового преобразователя и появление грубых погрешностей. Для нее 2-й уровень квантования первого аналогоцифрового преобразователя имеет положительное смещение, а Плежит между 21-м и (2 д)-м уровнями. Пусть при этом выходной код первого аналого-цифрового преобразователя превышает единицу, Тогда в соответствии с алгоритмом работы устройства содержимое счетчика по сигналу блока уиравления уменьшается на единицу и разностный сигнал на входе вычитаю- щего устройства равен д " = Бд П,. Абсолютная величина д 11 при этом не превосходит двух квантов грубой шкалы даже при совпадении уровня дискретизации Би П Таким образом в рассматриваемом случае, как1367156 и в предыдущем, сравнимые с номинальным шагом квантования первого анало 1,го-цифрового преобразователя погреш-ности его установки не вызывают сбоев в работе второго аналого-цифрового преобразователя и не влияют наточность измерений. Формула 1. Параллельно-последовательный аналого-цифровой преобразователь, содержащий первый (и+1)-разрядный и второй К-разрядный аналого-цифровые преобразователи, информационный вход первого из которых объединен с прямым входом блока вычитания и является входной шиной, инверсный вход блока вычитания соединен с выходом цифроаналогового преобразователя, входы которого являются выходными шинами старших разрядов, а выход блока вычитания подключен к информационному входу второго аналого-цифрового преобразователя, выходы с первого по (К)-й которого являются выходными шинами младших разрядов, о т л и - ч а ю щ и й с я тем, что, с целью увеличения точности преобразования за счет устранения погрешностей изме" рений в областях стыковки точной и грубой шкал, в него введены первый и второй двоичные счетчики импульсов, элемент ИЛИ, элемент 2 ИЛИ-И-НЕ, блок управления, вход которого является шиной "Пуск", а первый и второй выходы подключены к управляющим входам соответственно первого и второго аналого-цифровых преобразователей, выход первого разряда первого из которых соединен с первым входом элемента ИЛИ, остальные входы которого объединены с соответствующими входами установки первого двоичного счетчика импульсов и подключены к соответствующим выходам с второго (и+1)-й разрядов первого аналого-цифрового преобразователя, выход элемента ИЛИ соединен с первым входом элемента 2 ИЛИ-И-НЕ, второй вход которого под-.ключен к инверсному выходу первогоразряда второго двоичного счетчикаимпульсов, прямой выход первого разряда которого соединен с первым уп. равляющим входом первого двоичногосчетчика импульсов, выходы которогосоединены соответственными входами и з о б р е т е н и я 10 цифроаналогового преобразователя, авторой управляющий вход подключен кпрямому выходу второго разряда второго двоичного счетчика импульсов, инверсный выход второго разряда которо 15 го соединен с третьим входом элемента 2 ИЛИ-И-НЕ, четвертый вход которого соединен с выходом (К+1)-го разря.да второго аналого-цифрового преоб, разователя, а выход подключен к третьему управляющему входу первого двоичного счетчика импульсов, тактовыйвход которого объединен с одноименным входом второго двоичного счетчи- .ка импульсов и подключен к третьему25 выходу блока управления, четвертыйвыход которого соединен с установочным входом второго двоичного счетчика импульсов.2. Преобразователь по п.1, о т -ЗО л и ч а ю щ и й с я тем, что блокуправления выполнен на триггере,вход установки в "1" которого является входом блока управления, а выходчерез тактовый генератор подключен к35входу восьмиканального распределителя импульсов, выход первого каналакоторого является первым выходом блока управления, вторым выходом которого является выход шестого канала распределителя импульсов, выходы второго, третьего и седьмого каналов которого подключены соответственно к первому, второму и третьему входам элемента ИЛИ, выход которого является4 третьим выходом блока управления, авыход восьмого канала распределителяимпульсов через формирователь коротких импульсов подключен к входу установки в "О" триггера и является четвертым выходом блока управления.13671 5 б ийФ Составитель Ю.СпиридоновТехред Л.Сердюкова Корректор М.Пожо едактор С.Лисина Заказ 6850/5 Производственно-полиграфическое предприятие, гужгород, ул. Проектная, 4 ВНИИПИ по д 113035, Тираж 928 ПодписноеГосударственного комитета СССРелам изобретений и открытийМосква, Ж, Раушская наб., д. 4

СмотретьЗаявка

4048361, 03.04.1986

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИКЛАДНЫХ ФИЗИЧЕСКИХ ПРОБЛЕМ ИМ. А. Н. СЕВЧЕНКО, ВИЛЬНЮССКИЙ ЗАВОД ЭЛЕКТРОИЗМЕРИТЕЛЬНОЙ ТЕХНИКИ

АБЛОЖАВИЧЮС ИОНАС ПОВИЛО, БЕРЕЗОВСКИЙ МИХАИЛ КОНСТАНТИНОВИЧ, ВАЛАХ ВЛАДИМИР ВИКТОРОВИЧ, ГРИГОРЬЕВ ВЛАДИМИР ФИЛИППОВИЧ, ДАНИЛЕВИЧ ВСЕВОЛОД ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H03M 1/44

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 15.01.1988

Код ссылки

<a href="https://patents.su/6-1367156-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Аналого-цифровой преобразователь с самоконтролем

Следующий патент: Комбинированный аналого-цифровой преобразователь

Случайный патент: Способ получения фтористого винилидена пиролизом