Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

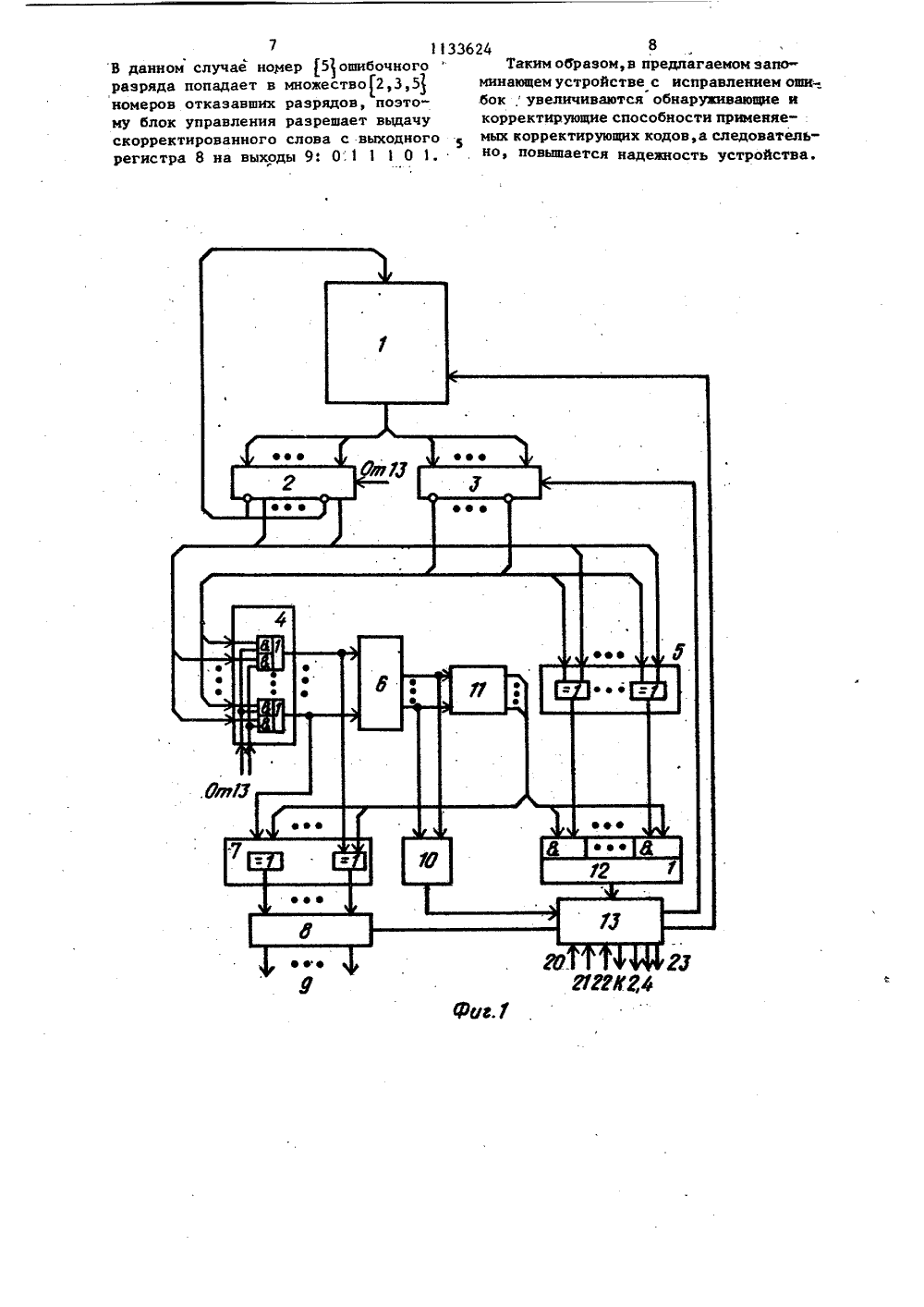

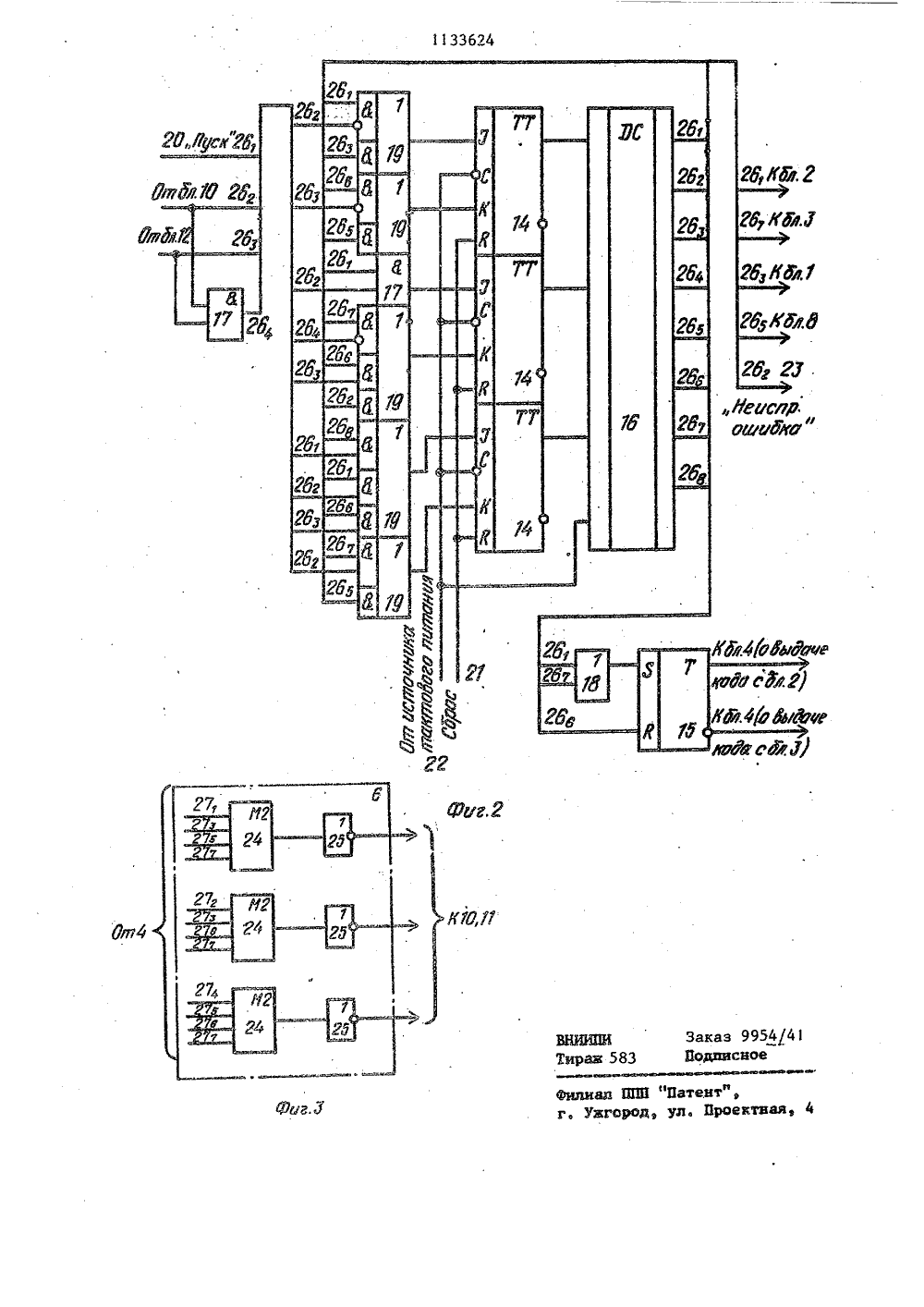

(51) ( 11 С 29/00 РЕТЕНИВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРпО ДелАм изоБРетений и ОТкРытийОПИСАНИЕ ИЗОК АВТОРСКОМУ СВИДЕТЕЛ(71) Киевский ордена Ленина политехнический институт им. 50-летия . Великой Октябрьской социалистической революции(56) 1. Авторское свидетельство СССР В 964737, кл. С 11 С 29/00, 1982.2. Авторское свидетельство СССР 9 855730, кл, С 11 С 11/00, 1981 (прототип).(54)(57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО СИСПРАВЛЕНИЕМ ОШИБОК, содержащее накопитель, первый и второй регистры,первый блок элементов ИСКЛЮЧАЮЩЕЕИЛИ, элемент И-ИЛИ, блок декодирова.ния, блок управления, причем информационный вход накопителя соединенс рдними выходами первого регистра,выходы накопителя подключены кинформационным входам первого,ивторого регистров, выходы второгорегистра и другие выходы первогорегистра соединены с входами первогоблока элементов ИСКЛОЧАЮЩЕЕ ИЛИ,выходы которого подключены к однимвходам элемента И-ИЛИ, выход которогосоединен с первым входом блока управления, второй, третий и четвертый входы которого являются управляющимивходами устройства, первый, второйи третий выходы блока управленияподключены соответственно к управляющим входам накопителя н первого,и второго регистров, четвертый выходблока управления является контрольным выходом устройства, о т л и ч аю щ е е с я тем, что, с целью повышения надежности устройства, в неговведены коммутатор, второй блокэлементов ИСКЛЮЧАКЩЕЕ ИЛИ, дешифратор, элемент ИЛИ, третий регистр,причем информационные входы коммутатора соединены с выходами второгорегистра и другими выходами первогорегистра, пятый и шестой выходыблока управления подключены к управ.ляющим входам коммутатора, выходыкоторого соединены с входами блокадекодирования, выходы которого подключены к входам дешифратора иэлемента ИЛИ, выход которого соединен с пятым входом блока управления,выходы коммутатора и дешифраторасоединены с входами второго блокаэлементов ИСКЛЮЧАКЩЕЕ ИЛИ, выходыкоторого подключены к информационным входам третьего регистра, вы"ходы которого являются информационными выходами устройства, управляющий вход третьего регистра подключенк седьмому выходу блока управления,выходы дешифратора соединены с другими входами элемента И-ИЛИ, 1133 б 24Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежныхзапоминающих устройств и систем,выполненных на функциональных узлах 5с большой степенью интеграции.Известно запоминающее устройствос самоконтролем, содержащее накопитель, регистры адреса прямого. иобратного кодов, блок кодированиядекодирования, схему сравнения,счетчик, распределитель и буферныйрегистр 11 .Недостатками данного запоминающего устройства являются большие аппаратурные затраты на реализацию счетчика и распределителя сигналов,что снижает надежность устройства,и, кроме того, для исправления обнаруженных ошибок необходимо дополни" 20тельное время на перебор всех возмож"ных комбинаций и проверку правильности каждого из наборов, что снижаетбыстродействие системы в целом.Наиболее близким по технической 25сущности к изобретению являетсязапоминающее устройство, содержащеенакопитель, подключенный к входам.регистров прямого и обратного кодов,выходы которых подключены к блокуобнаружения отказавших разрядов,корректирующее устройство, входкоторого соединен с выходом регист-.ра прямого кода, первый информационный выход - с блоком элементов И,второй информационный выход - сосхемой равенства кодов, к второмувходу которой подключен выход блокаобнаружения отказавших разрядов, иблок управления 12.Недостатком известного устройстваявляется низкая корректирующаяспособность применяемого кода.Цель изобретения " повышениенадежности запоминающего устройства.Указанная цель достигается тем,что в запоминающее устройство сисправлением ошибок, содержащее накопитель, первый и второй регистры,первый блок элементов ИСКЛЮЧАЮЩЕЕИЛИ, элемент И-ИЛИ, блок декодирования, блок управления, причем информационный вход накопителя соединен с одними выходами первого регистра, выходы накопителя подключенык информационным входам первого и 55второго регистров, выходы второгорегистра и другие выходы первогорегистра соединены с входами первого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которого подключены к однйм входам элемента И-ИЛИ, выход которо. го соединен с первым входом блока ,управления, второй, третий и четвертый входы которого являются управляющими входами устройства, первый, второй и третий выходы блока управления подключены соответственно к управляющим входам накопителя и пер" вого, и второго регистров, четвертый выход блока управления является контрольным выходом устройства, введены коммутатор, второй блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор, элемент ИЛИ, третий регистр, причем .информационные входы коммутатора соединены с выходами второго регистра и другими выходами первого регистра, пятый и шестой выходы блока управления подключены к управляющим входам коммутатора, выходы которого соедине. ны с входами блока декодирования, выходы которого подключены к входам дешифратора и элемента ИЛИ, выход которого соединен с пятым входом блока управления, выходы коммутатора и дешифратора соединены с входами второго блока элемечтов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которого подключены к информационным входам третьего регистра, выходы которого являются информационными выходами устройства, управляющий вход третьего регистра подключен к седьмому выходу блока управления, выходы дешифратора соединены с другими входами элемента ИИЛИ.На фиг. 1 приведена структурная схема предлагаемого запоминающего устройства; на фиг, 2 - пример реализации блока управления, на фиг. 3 - блок декодирования.Запоминающее устройство содержит накопитель 1, выход которого подключен к информационным входам регистров прямогоРПК)2 и обратного РОК) 3 кодов. Инверсные выходы регистра 2 связаны с информационными входами накопителя, а прямые выходы РПК 2 и инверсные выходы РОК 3 соединены с входами коммутатора 4, построенного на элементах И-ИЛИ, и с входами блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Выходы коммутатора подключены к входам блока 6 декодирования и к первым входам блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7, выходы которого соединены с информационны624 1133 3ми входами выходного регистра 8, выходы последнего являются информационными выходами 9 запоминающего устройства. Выходы блока 6 декодирования связаны с. входами элемента 5 ИЛИ 10 и входами дешифратора 11, выходы которого подключены к вторым входам блока 7 и к первым входам элемента И-ИЛИ 12, с вторыми входами которого соединены выходы 0 блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.Выходы элементов ИЛИ 1 О и И-ИЛИ 12 связаны с входами блока 13 управ. ления, выходы которого подклюЧены к управляющим входам регистровпрямого 2, обратного З.кодов, выходного регистра 8, а также к управляющим входам накопителя 1 и коммутатора 4.Каждый из регистров устройства представляет собой группу П -триггеров. Например, в регистре 2 входыП всех триггеров соединены с выходами накепителя 1, прямые выходы триггеров подведены к входам блока 4, а инверсные - к входам накопителя 1.Синхровходы С всех триггеров соедине. ны межцу собой и подключены к одному из выходов блока управления.Пример реализации блока 13 управления приведен на фиг. 2. В его состав входят 21 -триггеры 14,11 б - триггер 15, дешифратор 16, элементы И 17, ИЛИ 18, а также И-ИЛИ 19.После подачи питания исходное состоя. ние блока управления устанавливается по сигналу "Сброс", устанавливающему все 3 К -триггеры в нулевое состояние, а работа блока управления начинается подачей сигнала "Пуск", посту. пающего по входу 20, Блок управления имеет вход 21 сигнала "Сброс" и вход 22, по которому поступают сигналы от источника тактового питания. По выходу 23 блока управления выдается сигнал "Неисправимая ошибка".Реализация блока декодирования зависит от корректирующего кода, применяемого в запоминающем устройст ве. Для использования кода Хэмминга блок декодирования легко построить с цомощью сумматоров по модулю два, иа входы которых поступают значения разрядов кодового слова, входящих в данную контролируемую группу. Блок декодирования(фиг. 3) содержит три 4-входовых сумматора 24 по модулю два, входы которых соединены с выходами коммутатора 4, а выходы связаны 25 30 35 40 45 50 55 с входами соответствующих элементовНЕ 25, выходы которых подключены квходам схемы ИЛИ 10 и дешифратора11, разряды 26 контрольного кода, иразряды 27 считываемого слова.Запоминающее устройство работаетследующим образом.В накопителе хранится слово,закодированное применяемым помехоустойчивым кодом. При считывании извыбранной ячейки накопителя блокуправления вырабатывает управляющийсигнал, разрешающий прием кодовогослова на РПК 2. Затем блок 13 управления вырабатывает сигнал, по кото"рому содержимое регистра 2 передается через коммутатор 4 в блок б деко.дирования, в котором вычисляютсязначения проверочных соотношений.Если все проверочные соотношенияравны нулю(значит считанное изнакопителя слово не содержит ошибок),то по сигналу с выхода элемента ИЛИ10 блок управления разрешает приемслова на выходной регистр 8. Одновременно этот разрешающий сигналвыдается потребителю и разрешаетсчитывание информации с выходов9 регистра 8. Если хотя бы однопроверочное соотношение отлично отнуля(т.е. декодируемое слово содержит ошибку, то сигнал на выходеэлемена ИЛИ 10 приводит к выдачеблоком управления последовательностиуправляющих сигналов.на выполнениеследующих действий. Блок управлениявырабатывает сигнал, поступающийна управляющий вход накопителя 1,по которому содержимое регистрапрямого кода через инверсные выходызаписывается в ту же ячейку накопителя, а затем считывается и принимается на РОК 3.Таким образом, в этих двух регистрах находятся прямой и обратныйкоды считываемого слова. Эти коды спрямых выходов регистра 2 и инверсных выходов регистра 3 поступаютв блок 5, состоящий из элементовИСКЛЮЧАЮЩЕЕ ИЛИ, в котором по несовпадению разрядов поступивших кодовопределяется множество номеровотказавших разрядов. На выходахблока 5 присутствуют "1" на техпозициях, которые соответствуют номерам отказавших разрядов ячейки накопителя,Одновременно с этим производитсядешифрирование вычисленных для со 1133624держимого регистра прямого кода проверочных соотношений,Единичные сигналы на выходах дешифратора 11 соответствуют номерам предполагаемых ошибочных разрядов. 5 Информация с выходов коммутатора 4 передается в блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7, в котором предполагае мые ошибочные разряды исправляются инвертируются те разряды, для кото О рых на соответствующих выходах дешифратора присутствуют ), и слово поступает на информационные входы выходного регистра 8, Одновременно с этим одноименные разряды 5 кодов с выходов дешифратора и блока обнаружения отказавших разрядов поступают на соответствующие входы элемента И-ИЛИ 2. На выходе элемента И-ИЛИ появляется единичный сигнал 20 только в том случае, если хотя бы в одной паре одноименных разрядов кодов, поступающих с дешифратора 11 и блока 5, содержатся единицы. Появление на выходе элемента 12 единичного сигнала означает, что множество номеров подлежащих коррекции разрядов попадает в множество номеров отказавших разрядов. При этом блок управления вырабатывает сигнал, разрешающий прием исправленного слова на регистр 8 и считывание с его выходов 9.Если на выходе элемента И-ИЛИ 12 появигся нулевой сигнал, значит множество номеров подлежащих коррекции35 разрядов, определенных при декодировании прямого кода не попадает в множество отказавших разрядов. В этом случае блок управления вырабаты 40 вает сигнал, поступающий на управляющие входы коммутатора 4 и разрешающий передачу через него инверсного содержимого РОК 3 т.е. прямой код). Это кодовое слово поступает в блок декодирования и на одни из входов блока45 7. В блоке б декодирования производится декодирование аналогично первому случаю. Если все вычисленные проверочные соотношения равны нулю это возможно в случае, если Г кратный отказ вызвал г -кратную ошибку), то блок управления разрешает прием слова в регистр 8 и считывание с его выходов 9. В противном случае в блоке 7 производится кор рекция предполагаемых ошибочных разрядов номера которых определил)дешифратор 1, и слово поступает на информационные входы регистра 8, а также проверяется попадание множества подлежащих коррекции разрядов, определенных при декодировании инверсного содержимого регистра. 3 в множество отказавших разрядов. В случае появления единичного сигнала на выходе элемента И-ИЛИ 12 что свидетельствует о наличии такого попада" ния), блок 13 управления разрешает запись слова в регистр 8 и считывание из него. При наличии нулевого сигнала на выходе элемента 2 блок управления сигнализирует о том, что обнаруженные ошибки исправить нельзя, формируя на выходе 23 сигнал "11 еисправимая ошибка".Рассмотрим работу предлагаемого запоминающего устройства при использовании кода Хэмминга, исправляющего одну ошибку. Пусть в некоторую ячейку было записано слово0 1 1 1 1 О 11 2 3 4 5 6 7.На позициях 1,2 и 4 - значения контрольных разрядов. Пусть разряды 2,3 и 5 отказали, причем 2 и 3 разряды дают постоянно "0", а 5 разряд ииТогда при чтении слова на РПК получим0001101,т.е, слово содержит 2 ошибки. Приего декодировании определяют, чтоошибка находится в первом разряде(О О 1), =(1)После записи обратного кода содержимого ПРК считывания на регистреобратного кода получим код1000110.Содержимое РПК и РОК поступает вблок 5, который определит, чтопрямой и обратный коды совпадают вразрядах 2,3 и 5. Эти разряды образуют множество номеров отказавшихразрядов.ЭлементИ-ИЛИ 12 определяет,что номер 1"ошибочного разряда",определенный при декодировании содержимого РПК, не совпадает ни содним из элементов множества номеровотказавших разрядов. Поэтому производится декодирование инверсногозначения содержимого РОК, т.е,0111001,поступающего в блок декодирования.При декодировании слова определяют, что ошибка находится в 5 разряде11336 В данном случае номер 5 ошибочного раерада попадает а пеоаеотео 2,3,51 номеров отказавших разрядов, поэтому блок управления разрешает выдачу скорректированного слова с выходного регистра 8 на выходы 9 е О; 1 1 О 1. 24 8Таким образом, в предлагаемом запоминающемустройстве с исправлением ошибок : увеличиваются обнаруаивающие и корректирующие способности применяемых корректирующих кодов,а следовательно, повышается надезность устройства.

СмотретьЗаявка

3662564, 16.11.1983

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ДИЧКА ИВАН АНДРЕЕВИЧ, ДРОБЯЗКО ИРИНА ПАВЛОВНА, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, ОРЛОВА МАРИЯ НИКОЛАЕВНА, ЮРЧИШИН ВАСИЛИЙ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 07.01.1985

Код ссылки

<a href="https://patents.su/6-1133624-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Запоминающее устройство с самоконтролем

Следующий патент: Динамическое запоминающее устройство с коррекцией ошибок

Случайный патент: Устройство для исследования чувствительностик вибрации