Цифровая система передачи и приема информации с обнаружением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

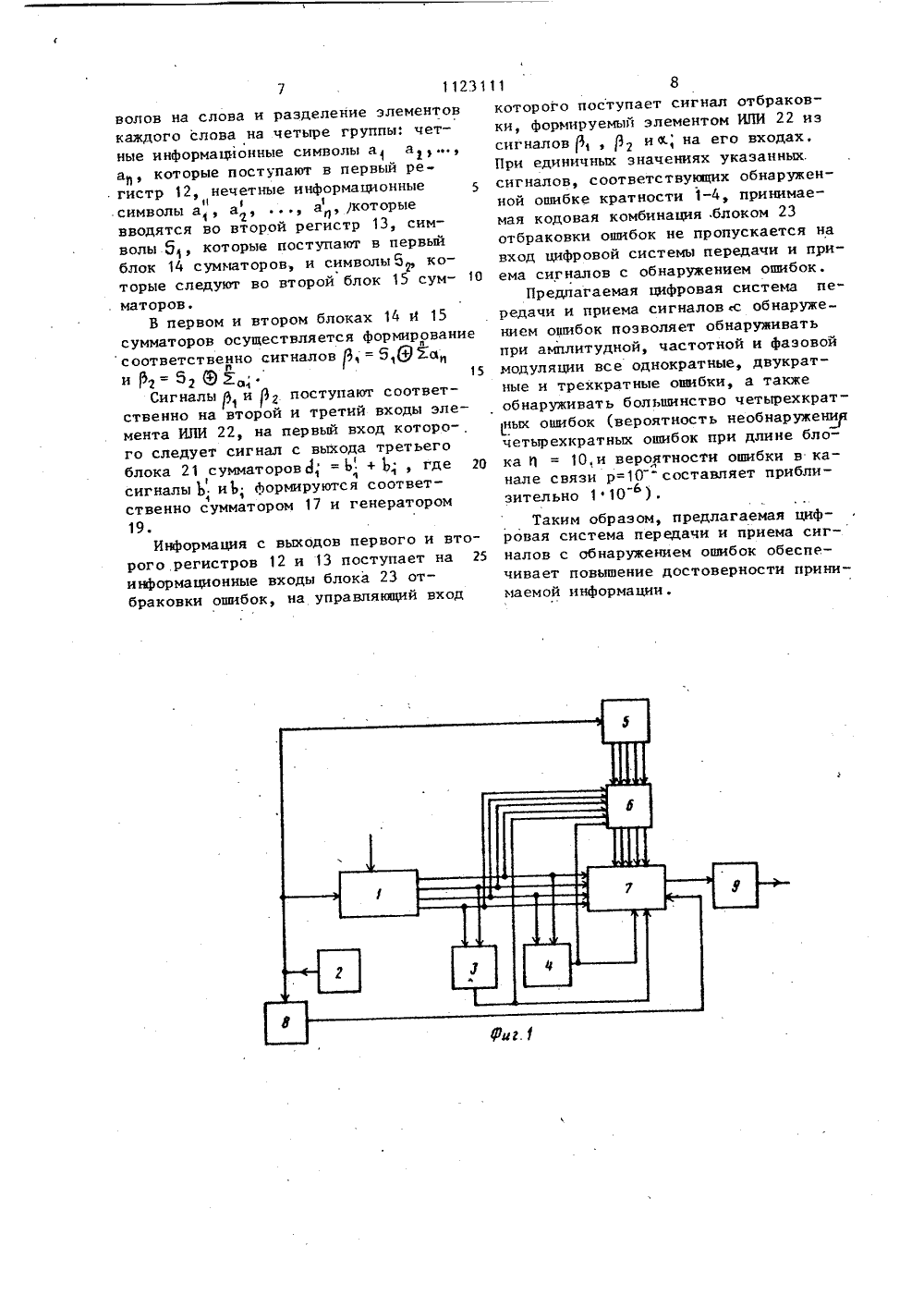

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК аэг ггг Згбгг Н 04 Е 1/10 ИСА 15/18-09сумматоры по моду ходы блока кодиро к соответствующим ра, входы первог два подключены к четным выходам б о СССР8.СССР1 роиос по ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ВТОРСНОМУ СВИДЕТЕЛЬСТВ(72) Р.Т.Сафаров и Я.Ю.Гладыш (7 1) Ленинградский электротехнический институт связи им. проф.М.А.Бонч- Бруевича(54) (57) ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОШИБОК, содержащая на передающей стороне последовательно соединенные генератор эталонного кода, блок сумматоров по модулю два, регистр и модулятор, последовательно соединенные синхронизатор и блок считывания, а также блок кодирования, при этом выход синхронизатора подсоединен к объединенным тактовым входам блока кодирования и генератора эталонного кода, выход блока считывания подсоединен к тактовому входу регистра, а вторьм входы блока сумматоров по модулю два подключены к соответствующим вторым входам регистра, на приемной стороне - последовательно соединенные демодулятор, блок задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, причем вход блока кодирования является входом цифровой системы, о т л и ч а ю щ а я с я тем, что, с целью повышения достоверности принимаемой информации, на передающей стороне введены первый и второй лю два, при этом вывания подсоединены вторым входам регистсумматора по модулю соответствующим неока кодирования,четные выходы которого подсодинены к соответствующим- входам второго сумматора по модулю два, выходы первого сумматора по модулю два подсоединены к объединенным первым дополнительным входам блока сумматоров по модулю два и регистра, объединенные вторые дополнительные входы которых подключены к выходу второго сумматора по модулю два, на приемной стороне вве- Е дены последовательно соединенные блог разделения посылок, первый регистр и. первый блок сумматоров по модулю два, последовательно соединенные второй регистр и вто блок сумматоров по а модулю два, п ледовательно соединенные третий блок сумматоров по модулюдва, элемент ИЛИ и блок отбраковкиошибок, при этом выход демодулятораи выход "Задержка 2 " блока задержкиподсоединены соответственно к второму и третьему входам сумматора помодулю два, выход которого подсоединен к первому входу третьего блокасумматоров по модулю два, прямой иййверсный выходы генератора эталон- .ного кода подсоединены соответствея -,но к вторым входам коррелятора итретьего блока сумматоров по модулюдва, вьсод нечетных посылок блокаразделения посыпок подсоединен кинформационному входу второго регистра, а выходы сигнала суммы четных посыпок и сигнала суммы нечетныхпосылок блока разделения посыпок д1123111 51 соединены соответственно к вторым входам первого и второго блока сумматоров по модулю два, выходы которых подключены соответственно к второму и третьему входам элемента ИЛИ, информационные входы блока отбраковки ошибок подключены соответственно к выходам первого и второго регистров, выход демодулятора подсоединен Изобретение относится к электросвязи и может быть использовано в телеметрии и при передаче данных.Известна цифровая система передачи и приема информации с обнаруже нием ошибок, содержащая на передающей стороне последовательно соединенные синхронизатор, генератор эталонного кода, блок сумматоров по модулю два и регистр, а также модулятор сигналов ФРМ, на приемной стороне - демодулятор и объединенные по входу сумматор по модулю два и элемент задержки, выход которого подключен к второму входу сумматора по модулю два, выход которого подключен к первому входу коррелятора, к второму входу которого подключен выход генератора эталонного кода, к второму входу которого подключен выход син хронизатора 13 Недостатком такой цифровой системы передачи и приема информации с обнаружением ошибок является низкая цостоверность принимаемой информации .Наиболее близкой к изобретению является цифровая система передачи и приема информации с обнаружением оши бок, содержащая на передающей стороне последовательно соединенные генератор эталонного кода, блок сумматоров по модулю два, регистр и модулятор, последовательно соединенные синхронизатор и блок считывания, а также блок кодирования, при этом вы- З 5 ход синхронизатора подсоединен к объединенным тактовым входам блока кодирования и генератора эталонного кода, вьмод блока считывания подсое- . динен к тактовому входу регистра, а 4 О вторые входы блока сумматоров по к информационному входу блока разделения посылок, а выход синхронизатораподсоединен к объединенным тактовымвходам блока разделения посылок,первого и второго регистров, блокаотбраковки ошибок и демодулятора,причем выходы блока отбраковкиЬшибок являются выходами цифровойсистемы. модулю два подключены к соответствующим вторым входам регистра, на приемной стороне - последовательно соединенные демодулятор, блок задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, причем вход блока кодирования является входом цифровой системы, на передающей стороне выходы блока кодирования через преобразователь кода подсоединены к соответствующим вторым входам регистра, а выход синхронизатора подсоединен к тактовому входу преобразователя кода, а на приемной стороне выход демодулятора подсоединен к объединенным входам блока задержки и второго корректора ошибок и к объединенным вторым входам,синхронизатора и сумматора по модулю два, выход которого через первый корректор ошибок подсоединен к входу второго корректора ошибок, выход генератора эталонного кода подсоединен к второму информационному входу первого корректора ошибок, а тактовые входы первого и второго корректоров ошибок подключены к выходу синхронизатора 2 .Недостатком известной цифровой системы передачи и приема информации с обнаружением ошибок является низкая достоверность принимаемой информации.Цель изобретения - повышение достоверности принимаемой информации .Для достижения поставленной цели в цифровую систему передачи и приема информации с обнаружением ошибок, содержащую на передающей стороне последовательно соединенные генератор эталонного кода, блок сумматоров по модулю два, регистр и модулятор, последовательно соединенные синхронизатор и блок считывания,а также блоккодирования, при этом выход синхрони. затора подсоединен к объединенным так товым:входа блока кодирования и гене.ратора эталонного кода, выход блокасчитывания подсоединен к тактовомувходу регистра, а вторые входы блокасумматоров по модулю два подключены 1 рк соответствующим вторым входам регистра, на приемной стороне - после-довательно соединенные демодулятор,блок задержки, сумматор по модулюдва, коррелятор,. синхронизатор игенератор эталонного кода, причемвход блока кодирования являетсявходом цифровой системы, на передающей стороне введены первый и второйсумматоры по модулю два, при этом щвыходы блока кодирования подсоединены к соответствующим вторым входамрегистра, входы первого сумматора помодулю два подключены к соответствующим нечетным выходам блока кодирования, четные выходы которого подсоединены к соответствующим входамвторого сумматора по модулю два,. выходы первого сумматора по модулю дваподсоединены к объединенным первымдополнительным входам блока сумматоров по модулю два и регистра, объединенные вторые дополнительные входыкоторых подключены к выходу второгосумматора по модулю два, на прием 35ной стороне введены последовательносоединенные блок разделения посылок,первый регистр и первый блок сумматоров по модулю два, последователь. но соединенные второй регистр и второй блок сумматоров по модулю два,последовательно соединенные третийблок сумматоров по модулю два,элемент ИЛИ и блок отбраковки ошибок, при этом выход демодулятора ивыход "Задержка 2" блока задержкиподсоединены соответственно к второму и третьему входам сумматора по1модулю два, выход которого подсоединен к первому входу третьего блокасумматоров по модулю два, прямойи инверсный выходы генератора-эталонного кода подсоединены соответственно к вторым входам коррелято ра и третьего блока сумматоров по Модулю два, выход нечетных посыпок бло-ка;разделения посылок подсоединен кинформационному входу второго регистра, а выходы сигнала суммы четных посьщок и сигнала суммы нечетных посылок блока разделения посылок подсоединены соответственно к вторым входам первого и второго блока сумматоров по модулю два, выходы которых подключены соответственно к второму и третьему входам элемента ИЛИ, информационные входы блока отбраковки ошибок подключены соответственно к выВодам первого и второго регистров, выход демодулятора подсоединен к информационному входу блока разделения посылок, а выход синхронизатора подсоединен к объединенным тактовым входам блока разделения,поСылок,первого и Второго регисГров, блока отбраковки ошибок и демодулятора,причем выходы блока отбраковки ошибокявляются выходами цифровой системы.На фиг. 1 приведена структурнаяэлектрическая схема предлагаемойцифровой системы передачи и приемаинформации с обнаружением ошибок, передающая часть; на фиг. 2 - то же,приемная часть.Передающая часть цифровой системыпередачи и приема информации с обнаружением ошибок содержит блок 1 кодирования, синхронизатор 2, первый сумматор 3 по модулю два, второй сумматор 4 по модулю два, генератор 5эталонного кода, блок 6 сумматоровпо модулю два, регистр 7, блок 8считывания, модулятор 9,Приемная часть цифровой системыпередачи и приема информации с обнаружением ошибок содержит демодулятор 10, блок 11 разделения посылок,первый регистр 12, второй регистр13, первый блок 14 сумматоров по модулю два, второй блок 15 сумматоровпо модулю два, блок 16 задержки, сумматор 17 по модулю два, коррелятор18, генератор 19 эталонного кода, синхронизатор 20, третий блок 21 сумматоров по модулю два, элемент ИЛИ22, блок 23 отбраковки ошибок,Цифровая система передачи и приема информации с обнаружением ошибок работает следующим образом.На передающей стороне (фиг. 1)в блоке 1 кодирования 2 П-значные информационные слова преобразуются в2 й-значные кодовые слова формируемого кода 3(0+1), 2Полученные 2 п-значные кодовые слова записываются в регистр 7 и в видепараллельного кода подаются в блокволов на слова и разделение элементов каждого слова на четыре группы: четные информационные символы а 1 а 2, а 11, которые поступают в первый регистр 12, нечетные информационные символы а, а , , а, (которые вводятся во второй регйстр 13, символы 51, которые поступают в первый блок 14 сумматоров, и символы 52, которые следуют во второй блок 15 сум маторов.В первом и втором блоках 14 И 15 сумматоров осуществляется формирование соответственно сигналов , = б,о+ ,Еа и 12 2 Ва 115Сигналый 2 поступают соответственно на второй и третий входы элемента ИЛИ 22, на первый вход которо-, го следует сигнал с выхода третьего блока 21 сумматоровд; = Ь + Ь, где 201сигналы в. и формируются соответфственно сумматором 17 и генератором 19.Информация с выходов первого и второго регистров 12 и 13 поступает на 25 информационные входы блока 23 отбраковки ошибок, на управляющий вход 111 8которого поступает сигнал отбраковки, формируемый элементом ИЛИ 22 из сигналов (3 32 и К; на его д, При единичных значениях указанных. сигналов, соответствунзцих обнаруженной ошибке кратности 1-4, принимаемая кодовая комбинация блоком 23 отбраковки ошибок не пропускается на вход цифровой системы передачи и приема сигналов с обнаружением ошибок.Предлагаемая цифровая система передачи и приема сигналов с обнаружением ошибок позволяет обнаруживать при амплитудной, частотной и фаэовой модуляции все однократные, двукратные и трехкратные ошибки, а также обнаруживать большинство четырехкратных ошибок (вероятность необнаружеюу четырехкратных ошибок при длине блока О = 10,и вероятности ошибки в канале связи р=10 составляет приблизительно 1 ф 10 ).Таким образом, предлагаемая цифровая система передачи и приема сигналов с обнаружением ошибок обеспечивает повышение достоверности принимаемой информации..Лекарь Техред Л.Микеш . Корректор И.Эрдейи Редак е филиал ППП "Патент",Закаэ 8 155/44 Тираж 63 ВНИИПИ Государственно по делам иэобретени 113035, Москва, Ж, Подписноо комитета СССРи открьпийРаушская наб., д. 4/ Ужгород, ул . Проектная. 4

СмотретьЗаявка

3511815, 10.11.1982

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

САФАРОВ РИЗА ТАДЖИЕВИЧ, ГЛАДЫШ ЯРОСЛАВ ЮРКОВИЧ

МПК / Метки

МПК: H03M 13/05

Метки: информации, обнаружением, ошибок, передачи, приема, цифровая

Опубликовано: 07.11.1984

Код ссылки

<a href="https://patents.su/6-1123111-cifrovaya-sistema-peredachi-i-priema-informacii-s-obnaruzheniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Цифровая система передачи и приема информации с обнаружением ошибок</a>

Предыдущий патент: Устройство формирования сигнала стереофонического радиовещания с полярной модуляцией

Следующий патент: Устройство поиска шумоподобных сигналов

Случайный патент: Машина для покрывания бумаги эмульсией