Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

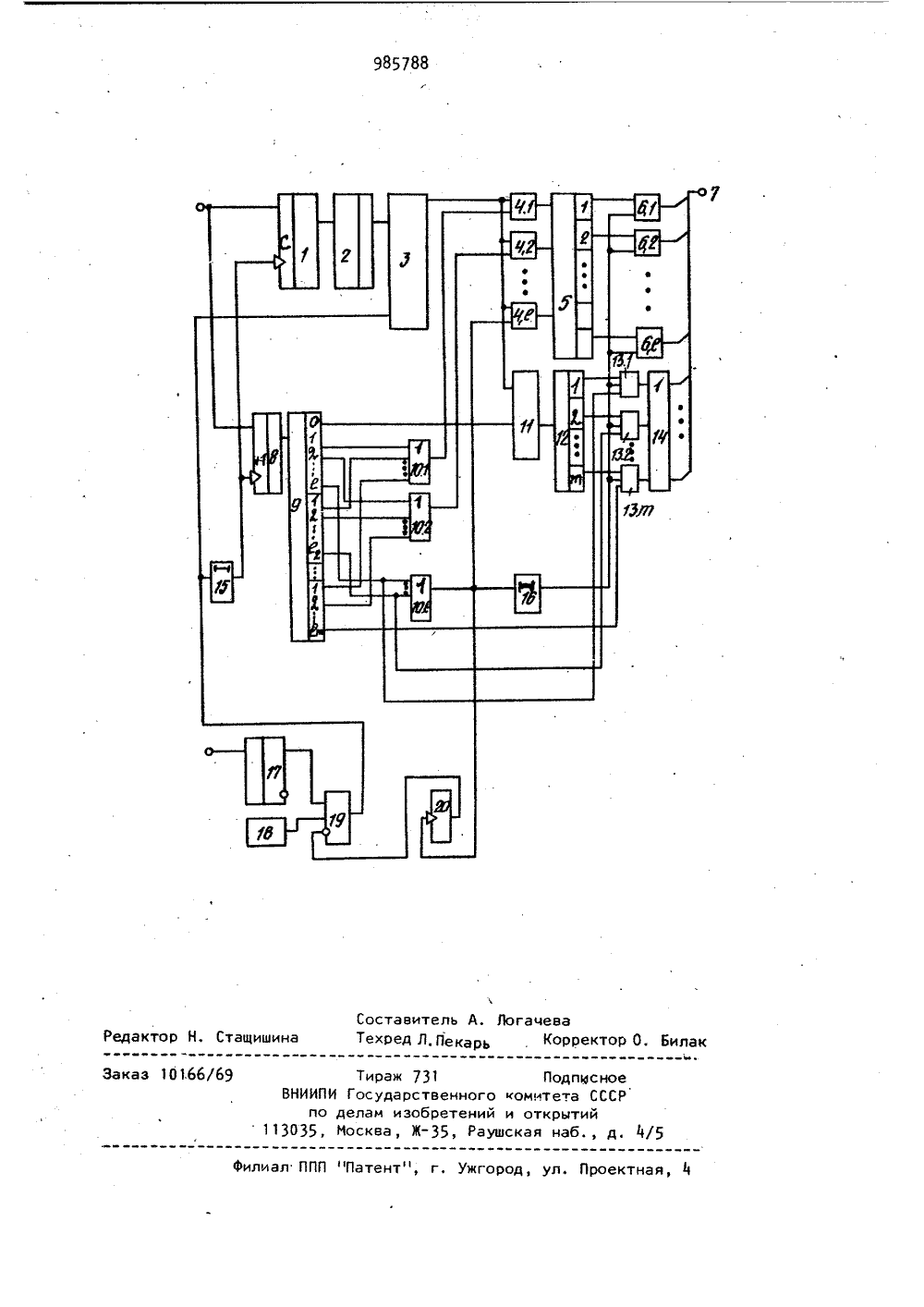

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУСоюз СоветскихСоциалистическихРеспублик(5)М. Кл,С 06 Г 9/22 3 Ьеударствошый комитет СССР по делан иэобретеиий и аткрытийВата опубликования описания 30.12.82 В.С, Харченко, Г.Н. Тимонькин, Ю.А. Матвиенко, А.П. Плахтеев и С,Н. Ткаченко(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯИзобретение относится к вычисли 1 ельной технике и может быть использовано при синтезе устройств для ЦВМ.Известно устройство микропрограммного управления, содержащее запоминающий блок, два счетчика, два дешифратора, регистр микрокоманд, генератор импульсов, группу из (К+1) блоков элементов И, блок элементов ИЛИ (,1 3.Недостатком данного устройства является низкая экономичность запомина О ющего блока, обусловленная тем, что в ячейке запоминающего блока может храниться только целое число микрокоманд.Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является устройство микропрограммного управления, содержащее блок памяти, два счетгочика, два дешифратора, регистР микРо- команд, два элемента задержки, 2 е+вн. +1 блок элементов И, блок элементов ИЛИ, группу иэ т элементов ИЛИ, эле 2мент И, одновибратор, триггер, гене-, ратор тактовых импульсов ( 2 1.Недостатком данного устройства являются низкие функциональные возможности, которые обусловлены невозможностью реализации микропрограмм, состоящих из микрокоманд, разрядность которых больше длины линеек блока памяти, причем остаток целой микрокоманды должен не превышать половину длины формата микрокоманды; невозможностью управления операционными устройствамй большой размерности, т, е. операционными устройствами, для которых в каждом такте работы необходимо фор- мировать большое число управляющих воздействий (микроопераций), в каждом такте устройство может выдавать микрокоманды, общее число разрядов которых меньше длины линейки на разрядность остатков; сложностью схем считывания, что ведет к снижению отказоустойчивости в целом и усложняет про" цесс производства таких устройств в3 985788 5 О триггер, генератор тактовых импульсов 15 30 го счетчика, выход которого соединен с входом второго дешифратора, первый выход которого соединен с вторым входе дом Я +1)-го блока элементов И, дополнительно введены буферный регистР,чика соединен с входом начального адреса устройства, 1-й выход (1=1"8)45 1-й группы выходов второго дешифратора ( =1"В) подключены к -му входу 1-го элемента ИЛИ группы, выходы которых подключены к вторым входам 1-го блока элементов И, выход которого со 50единен с входом регистра микрокоманд,0-е выходы 1-й группы выходов второго дешифратора соединены соответственно с первыми входами (21+2)-(26+пн 1)-гоблоков элементов И, выход 1-го элемента ИЛИ группы соединен через одновибратор с инверсным входом элементаИ, выход которсго соединен с управляющим входом блока памяти и через злеинтегральном исполнении; сложностьюмодификации схемы при изменении пара"метров микропрограммы.Цель изобретения - расширение Функциональных возможностей устройства.Поставленная цель достигается тем, что в устройство, содержащее блок памяти, два счетчика, два дешифратора, регистр микрокоманд, два элемента задержки, 28+пн.1 блок элементов И (п 1- Формат микрооперации, 0 - число полных линеек микрокоманды в памяти), блок элементов ИЛИ, группу из т элементов ИЛИ, элемент И, одновибратор причем информационный вход первогосчетчика подключен к входу начального адреса устройства; а выход соединен с информационным входом первогодешифратора, выход которого соединенс адресным входом блока памяти, информационный выход которого соединенс первыми входами 1 (0+1) блоков элементов И, выходы регистра микрокомандсоединены с первыми входами Я+2)1- (21+1) - го блоков элементов И, выходы(20+2)-(2 Ч+пн)-го блоков элементов Исоединены с входами первого блока элементов ИЛИ, выходы которого подключены к выходу микрооперации устройства,единичный вход триггера подключен квходу пуска устройства, единичный выход - к первому входу элемента И, второй вход которого соединен с выходомгенератора тактовых импульсов, выходэлемента И соединен через первый элемент задержки со счетным входом второ. причем установочный вход второго счет. 20 25 4мент задержки со счетным входом пер- . вого счетчика, выход 1 -го элемента ИЛИ группы соединен через элемент задержки с вторыми входами (Р+2)-(26+ +ин.1)-го блоков элементов И; выходы (Р+2)-(2 Р+1) - го блоков элементов И подключены к выходу микроопераций устройства; выход (0+1)-го блока элементов И соединен с информационным входом буферного регистра, выходы которого соединены с третьими входами (20+2)-(20+втн.1) -го блоков элементов И.Сущность изобретения состоит в повышении экономичности блока памяти устройства управления путем записи отдельных микрокоманд любого Формата в линейки памяти, в том числе и микрокоманд с форматом, превышающим размер линейки, а остатков различной длины, не вошедших в эти линейки, в отдельные ячейки.На чертеже представлена функциональная схема устройства.Устройство содержит первый счетчик 1, первый дешифратор 2, блок 3 памяти, (1-9)-й блок ч элементов И, регистр 5 микрокоманд, (7 +2)-(20+1)-й блок 6 элементов И, выход 7 микроопераций устройства, второй счетчик 8, второй дешифратор 9, группа 10 элементов ИЛИ, (6+1)-й блок элементов И 11, буферный регистр 12, (21+2)-(20+ Нп+1)-й блоки 13 элементов И, блок 11 элементов ИЛИ, первый элемент 15 задержки, второй элемент 16 задержки, триггер 17, генератор 18 тактовых импульсов, элемент И 19, одновибратор 20.В исходном состоянии оба счетчика 1 и 8 и триггер 17 находятся в нулевом состоянии, элемент И 19 закрыт, регистры микрокоманд 5 и буферный 12 свободны.Предлагаемое устройство работает следующим образом.По начальному адресу, поступающему на первый вход счетчика 1 и вход счетчика 8 на первом дешифраторе 2 возбуждается выход, соответствующий начальному адресу, а на втором .дешифраторе 9 - нулевой выход,Сигналом "Пуск" триггер 17 устанавливается в единичное состояние, разрешая прохождение импульсов с генератора 18 черезэлемент И 19 Первый импульс разрешает считывание информации с начальной ячейки блока 3 памяти, Через открытый дешифратором 9 к5+1)-й блок элементов И 11 эта инфорповышением информативности блока памяти.При этом схема считывания предлагаемого устройства по сравнению с прототипом упрощается на величину где С 1, С Сс - об оборудования регистра, дещифратора и счетчика со" ответственно. Формула изобретения 5 98578 мация записывается в буферный регистр 12. Через время, определяемое элементом 15 задержки, счетчик 8 устанавливается в состояние, которому соответствует единица, на первом выходе дешифратора 9. Вторым импульсом считывается информация из следующей линейки блока 3 памяти и через открытые элементы И (1- Р)-го блоковэлементов И записывается в первое поле регист- О ра 5 микрокоманд. Через время, определяемое элементом 15 задержки счетчик 8 устанавливается в состояние, которому соответствует единица, на втором выходе дешифратора 9, а счетчик1 з в состояние, по которому выбирается следующая .линейка блока 3 памяти. Затем импульсами с генератора 18 осуществляется сцитывание информации из . блока 3 памяти и запись ее в соответ я ствующие поля регистра 5 микрокоманд, (Р +1)-м импульсом генератора 18 осуществляется запись информации из блока 3 памяти в Р -е поле регистра 5 микрокоманд. Единичный сигнал с Р-го уз выхода дещифратора 9 поступает на первый вход (20+2)-го блока 13. элемента И. Через время, определяемое элементом 16 задержки, все Р полей ре-гистра микрокоманд будут заполнены и на вторые входы всех (6+2)-(28+он 1) блоков б и 13 элементов И поступят разрешающие считывание информации сигналы.Содержимое ( 1 Р) го полей регист 35 ра 5 микрокоманд и первого поля буферного регистра 12 поступает на выход 7.Кроме того, сигнал с выхода Р -го элемента ИЛИ группы 0 элементов ИЛИ поступит на вход одновибратора 20, коО торый Формирует сигнал нужной длительности и запрещает прохождение импульсов с генератора 18 через элемент И 19, Я +2)-й импульс в схему не пода-.ется. После истечения времени,.необ ходимого на выдачу информации на выход 7 и определяемое элементом 15 задержки, счетчики 1 и 8 Я +)-м импульсом переводятся в состояние, которым соответствуют единицы на тех выходах дешифраторов 2 и 9, по которым считывается информация из первой линейки блока памяти группы линеек, соответствующих второй микрокоманде.После окончания импульса, вырабо 55 танного одновибратором в схему снова подаются тактовые импульсы через открытый элемент И 19 и первым импульсом считывается первая линейка следующей микрокоманды. Дальше устройство работает вышеописанным образом,При считывании целых частей второй микрокоманды М= 1 М у 1 М 2 д 1 М 20 йМ 2 управление осуществляется сигналами со второй группы выходов дешифратора 9 и т, д. После считывания м-й микрокоманды в счетчик 1 записывается адрес следующей группы микрокоманд либо путем естественной адресации, либо путем принудительной записи кода адреса со входа устройства.Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями, Это подтверждается возможностью реализации микро- команд, разрядность которых превышает разрядность линеек блока памяти; упрощением схемы считывания при реализации устройства с использованием схем средней и большой степени интеграции; Устройство микропрограммного управления, содержащее блок памяти, двасчетчика, два дещифратора, регистр микрокоманд, два элемента задержки, 2+янблоков элементов И Ь- формат микрооперации, Р - число полных линеек микрокоманды в памяти), блок элементов ИЛИ, группу из щ элементов ИЛИ, элемент И, одновибратор, триггер, генератор тактовых импульсов, причем информационный вход первого счетчика подключен к входу начального адреса устройства а выход - к информационному входу первого дешифратора, выход которого соединен с адресным входом блока памяти, информационный выход которого подключен к первым входам 1-(1+1) блоков элементов И, выходы регистра микрокоманд соединены с первыми входами (Р +2)-(2 Р+1)-го блоков эле. ментов И, выходы (29+2)-(2 Р+пн 1)-го блоков элементов И соединены с входами первого блока элементов ИЛИ, выходы которого подключены к выходу мик985788 7рооперации устройства, единичный вход триггера подключен к входу пуска устройства, единичный выход - к первому входу элемента И, второй вход которого соединен с выходом генератора так" товых импульсов, выход элемента И подключен через первый элемент. задержки со счетным входом второго счетчика, выход которого соединен с входом вто. рого дешифратора, первый выход кото О рого соединен с вторым входом (Р +1)- го блока элементов И, о т л и ч а ющ е е с я тем, что, с .целью расширения функциональных возможностей путем, реализации микропрограмм, состоящих 1 З из микрокоманд с разрядностью, превышающей разрядность линеек блока памяти, дополнительно содержит буферный регистр, причем установочный вход второго счетчика соединен с входом нача льного адреса устройства, 1 -й выход (1 1- 9) -й группы выходов второго дешифратора ( 1-в). подключены к -му входу 1-го элемента ИЛИ группы, выхо 1 ды которых подключены к вторым входам В -го блока элементов И, выход которого подключен к входу регистра микро" команд, К -е выходы у-й группы выходоввторого дешифратора соединены с первыми входами (20+2)-(26+в 1)-го блоков элементов И, выход 0-го элементаИЛИ группы соединен через одновибратор с инверсным входом элемента И, выход которого соединен с управляющимвходом блока памяти и через элементзадержки со счетным входом первогосчетчика, выход-го элемента ИЛИгруппы соединен через элемент задержки с вторыми входами (6+2)-(20+лн 1)го блоков элементов И, выходы Я +2)(20+1)"го блоков элементов И подключены к выходу микроопераций устройства, выход (6+1)-го блока элементов Исоединен с информационным входом буферного регистра, выходы которого соединены с третьими входами (21+2)-(21+в 1)-го блоков элементов И.Источники информации,принятые во внимание при экспертизе1. Геолецян А.Г. ЭВМ иНаири, М"Статистика", 1979, с. 132, авторское свидетельство СССР позаявке й 2961311/18-21, кл. 0 06 Г 9/22,1980.оставитель А, Логацеваехред Л.Пекарь Корректор О. била НИИП 13035 иал ППП "Патент", г, Ужгород, ул. Проектна Редактор Н, Стащиш Заказ 10166/69 Тираж 731 Государственног елам изобретени осква, Ж, Ра Подпцс ноекомитета СССРи открытийская наб д. 4

СмотретьЗаявка

3310259, 02.07.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, МАТВИЕНКО ЮРИЙ АНДРЕЕВИЧ, ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 30.12.1982

Код ссылки

<a href="https://patents.su/5-985788-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления с контролем переходов

Следующий патент: Микропрограммное устройство управления с исправлением ошибок

Случайный патент: Устройство для герметизации газовых и нефтяных скважин