Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

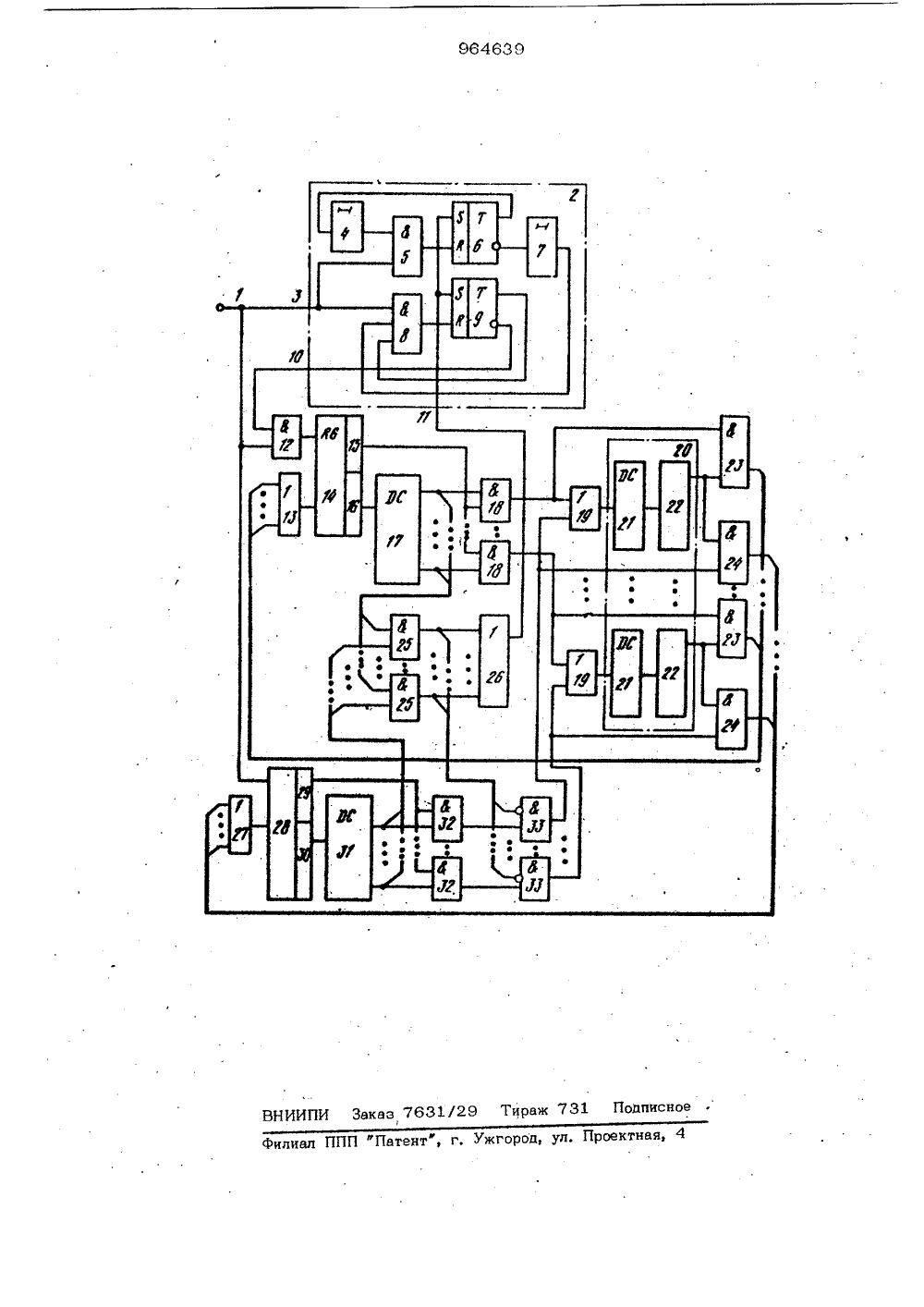

(51) М. Кл. С 06 Р 9/22с присоединением заявки М 3 ЬоудэРетикньМ квинтет ь.ь.ьР оо далем изобретений и открнтяй(53) УДК 681, 325(088 8) Дата опубликования описания 07,10,82(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ 2ра микрокоманд, первый выход которогоподключен к входу дешифратора 21Недостатком известного устройстваявляется низкая производительность, которая обусловлена невозможностью реализации параллельных микропрограмм, т,е.реализации режима мультнпрограммирования 10 Наиболее близким к изобретению по технической сущности и достигаемому положительному эффекту является микро-. программный процессор, который содержит микропрограммное управляющее устройство и операционный блок, Микропро-граммное управляющее устройствб этого20 процессора состоит из постоянной памяти, блока управления, выход которого соединен с первым входом элемента И и регист 1Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных вычислительных системах,Известен микропрограммный процессор, который содержит постоянную память, блок управления, регистр микрокоманд и дешифратор 1 Недостатком данного устройства является низкая производительность, которан обусловлена возможностью только последовательного выполнения микропрограмм,Бель изобретения состоит в повышении производительности устройства за счет организации режима мультипрограммирования для двух микропрограмм.Поставленная цель остигается тем, что микропрограммное устройство управления, содержащее блок памяти, блок управления, первый выход которого соединен с первым входом первого элемента И, первый регистр микрокоманд, первый информационный выход которого подключен к входу первого дешифратора, выход которого соединен с первыми входами элементов И первой группы, дополнительно содержит второй регистр микро3 96463 команд, второй дешифратор, пять групп элементов И, три группы элементов ИЛИ и элемент ИЛИ, причем выходы элементов ИЛИ первой группы подключены к адресным входам блока памяти, информационные выходы которого подключены К первым входам элементов И второй и третьей групп, выходы которых подклю- . чены к входам элементов: ИЛИ второй и третьей групп соответственно, выходы 1 О которых подключены к информационным входам первого и второго регистров микрокоманд соответственно, первый информационный выход второго регистра микрокоманд подключен к входу второго 15 дешифратора; выход которого подключен к первым входам элементов И четвертой группы, вторые информационные выходы первого и второго регистров микрокоманд подключены к вторым входам элементов 30 И первой и четвертой групп соответствен но, выходы первого и второго дешифраторов подключены к первым и вторым входам элементов И пятой группы, выходы которых подключены к входам элемента 25 ИЛИ и к инверсным входам соответствующих элементов И шестой группы, прямые входы которых подключены к соответствующим выходам элементов И четвертой группы, а ыоды - к соотетстующим Зо вторым входам элементов И третьей группы и к первым входам элементов ИЛИ первой группы, к соответствукицим вторым входам которых подключены выходы элементов И первой группы и вторые входы соответствующих элементов И ,второй группы, выход элемента ИЛИ подипочен к первому входу блока управления, второй вход которого является входом тактовых импульсов устройства и подключен к второму входу элемента И и к управляющему входу второго регистра микрокоманд, выход элемента И подключен к управляющему входу первого регистра микрокоманд. Блок управления содержит два элемента задержки, два элемента И и два триггера причем второй вход блока подключен к первым входам порвого и второго элементов И, выходы которых подключены соответственно к нулевым входам пер. вого и второго триггеров, единичные входы которых соединены с первым входом блока, прямой выход первого триггера через первый элемент задержки соединен с вторым входом первого элемента И, а инверсный выход через второй элемент задержки - с вторым входом второго 9 4элемента И, третий вход которого подключен к прямому выходу второго триггера, инверсный выход которого являетсявыходом блока,На чертеже приведена функциональнаясхема предлагаемого устройства,Устройство содержит вход 1 тактовыхимпульсов, блок 2 управления, содержащий первый вход 3, элемент 4 задержки,элемент И 5, триггер 6, элемент 7 за-.держки, элемент И 8, триггер 9 выход10 и второй вход 11, элемент И 12,группу элементов ИЛИ 13, регистр 14микрокоманд, содержащий поля 15 и 16,младших и старших разрядов, дешифратор17, группу элементов И 18, группу элементов ИЛИ 19, блок 20 памяти, содержащий дешифраторы 21 и большие интегральные схемы 22 .памяти, группу элементов И 23, группу элементов И 24,группу элементов И 25, элемент ИЛИ26, группу элементов ИЛИ 27, регистр28 микрокоманд, содержащий поля 29и 30, младших разрядов и старших разрядов, дешифратор 31, группу элементовИ 32, группу элементов И 33. Устройство может функционировать в двух режимах: последовательной реализациимикропрограмм и мультимикропрограммироввния,В режиме последовательной реализации в каждом рабочем такте устройствоможет реализовать только одну микрокоманду, в режиме мукьтимикропрограммирования параллельно реализуются две(в рассматриваемом случае) или болеемикрокоманды,Устройство работает следующим образом.В режиме мультимикропрограммирования происходит параллельная реализация двух микропрограмм (основной и параллельной), Адрес очередной микрокоманды основной (параллельной) микропрограммы хранится в регистре 14 (28), а триггеры 6 и 9 блока 2 управления находятся в нулевом состоянии. По очередному тактовому импульсу с входа 1 устройства срабатывает элемент И 12 и своим выходным сигналом разрешает считывание информации с регистра 14, Одновременно по этому же тактовому импульсу происходят считывание очередной микрокоманды параллельной микропрограммы с выходов регистра 28 микрокоманд. При этом с выхода операционного поля. регистра 14 (28) считыввются и. передаются на объекты управления, например, операционные5 .964блоки (не показаны), коды выполняемыхмикроопераций, с выходов поля 16 (28)считывается код номера БИС 22 памятив блоке 20 памяти, который поступает на .вход дешифратора 17 (31), Одновременнокод номера ячейки в БИС 22 памятисчитывается с выходов поля 15 (29) регистра 14 (28) и поступает на входыгруппы элементов И 18 (32),Сигналом с выхода дешифратора.17, 10соответствующего номеру БИС 22, в ко.тором хранится очередная микрокомандаосновной микропрограммы открываютсясоответствующие элементы И 1 Ы и по кодуадреса ячейки в БИС памяти через соот- Иветствующие элементы ИЛИ 19 и дешифратор 21 адреса считывается код микрок оманды очередной микропрограммы. Одновременно аналогичным образом срабатывают соответствука 1 ие элементы И 32, 20которые передают код адреса ячейки, вкоторой записан код очередной микрокоманды параллельной микропрограммы, иобращаются к разным ЬИС 22 блока 20,а сигналы с одноименных выходов деши ф.раторов 17 и 31 отсутствуют. Поэтомуни один из элементов И 25 не срабаты,вает и, следовательно, элементы И 32пропускают код адреса .ячейки с очередной микрокомандой параллельной микро- ЗОпрограммы, выбор которой происходитаналогично для основной микропрограммы.При считывании информации с выходовблока 20 открываются соответствукзциегруппы элементов И 23 и 24 и черезэлементы ИЛИ 13 и 27 осуществляетсязапись кодов микрокоманд основной и параллельной микропрограмм в регистры14 и 28 соответственно. В слуиае обращения обоих микропрограмм к одной и тойоже БИС памяти в блоке 20 срабатываетодин из элементов И 25 и запрещаетпередачу адреса очередной микрокомандыпараллельной микропрограммы через элементы И 33, а также через элемент ИЛИ26 подает сигналы на вход 11 блока 2управления, По этому сигналу триггера6 и 9 устанавливаются в одиночное состояние. ИТриггер 9 запрещает подачу, тактовых импульсов с входа 1 через элемент И 12 на вход считывания регистра 14 микро- команд. По очередному тактовому импульсу произойдет считывание микрокоманды55 параллельной микропрограммы с регистра 28 и выборка очередной микрокоманды этой же микропрограммы из блока 20, По этому тактовому изменению состояния 639 6триггеров 6 и 9 блока 2 упр. вления не происходит из-за наличия элементов 4 и 7. По следующему тактовому импульсу срабатывают элементы И 5 и 8 блока 2 управления, устанавливают триггеры 6 и 9 в нулевое состояние. Сигналом с нулевого выхода триггера 9 разрешается поступление сигнала на вход считывания ,регистра 14, и далее устройство функционирует аналогично. Ф ормула изобретения 1. Микропрограммное устройство управления, содержащее блок памяти, блок уцравления, первый выход которого соединен с первым входом первого элемента И, первый регистр микрокоманд, пер. вый информационный выход которого подключен к входу первого дешифратора, выходкоторого соединен с первыми входами .элементов И первой группы, о т л и - ч а в щ е е с я тем, что, с целью повышения производительности за счет реализации режима мультимикропрограммиро.вания, оно дополнительно содержит второй регистр микрокоманд, второй дешифратор, пять групп элементов И, три групйы элементов ИЛИ и элемент ИЛИ, причем выходы элементов ИЛИ первой группы подключены к адресным входам блока памяти, информационные выходы которого подключены к первым входам элементов И второй и третьей групп, выходы которых подвпочены к входам элементов ИЛИ второй и третьей групп соответственно, выходы которых подключены к информационным входам первого й второго регМтров микрокоманд соответственно, первый информационный выход второго регистра микрокоманд подключен к входу второго дешифратора, выход которого подключен к первым входам элементов И четвертой группы, вторые информационные выходы первого и второго регистров микрокоманд подключены к вторым вхо дам элементов И первой и четвертой групп соответственно, выходы первого и второго дешифраторов подключены к первым и вторым входам элементов И пятой группы, выходы которых подключены к входам эпемента ИЛИ и к инверсным входам соответствующих элементов И шестой группы, прямые входы которых подключены к соответствующим выходам элементов И четвертой группы, а выходык соответствующим вторым входам элементов И третьей группы и к первым7 964639 8 входам элементов ИЛИ первой группы, к ходы которых подключены соответственно соответствующим вторым входам которых к нулевым входам первого и втррого трит подключены выходы элементов И первой геров, единичные входы которых соедин группы и вторые входы соответствующих ны с первым входом блока, прямой выход элементов И второй группы, выход эле-первого триггера через первый элемент мента ИЛИ подключен к первому входу задержки соединен с вторым входом перблока управления, второй вход которого вого элемента И, а инверсный выход - является входом тактовых импульсов уст- через второй элемент задержки с вторым ройства и подключен к второму входу входом второго элемента И, третий вход элемента И и к управляющему входу вто О которого подключен к прямому выходу рого регистра микрокоманд, выход эле- второго триггера, инверсный выход которо- мента И подключен к управляющему вхо- го является выходом блока. яу первого регистра микрокоманд.2. Устройство по и. 1, о т л и ч а-Источники информации, ю щ е е с я тем, что; блок управления 1 з принятые во внимание при экспертизе содержит два элемента задеряаи, два 1, Патент Великобритании элемента И и два триггера, причем вто- М 1398367, кл. ( 4 А, о 1 тублик. 1975. рой вход блока подипочен к первым вхо. Авторское свидетельство СССР дам первого и второго элементов И, вы- Ж 71777 Якл. С 06 Р 15/00, 1977,

СмотретьЗаявка

3239803, 26.01.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ХОМЕНКО АЛЕКСАНДР ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.10.1982

Код ссылки

<a href="https://patents.su/5-964639-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Многоканальное устройство приоритета

Следующий патент: Микропрограммное устройство управления

Случайный патент: Зеркально-линзовый объектив