Устройство для обнаружения и исправления ошибок в системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 888124

Автор: Краснобаев

Текст

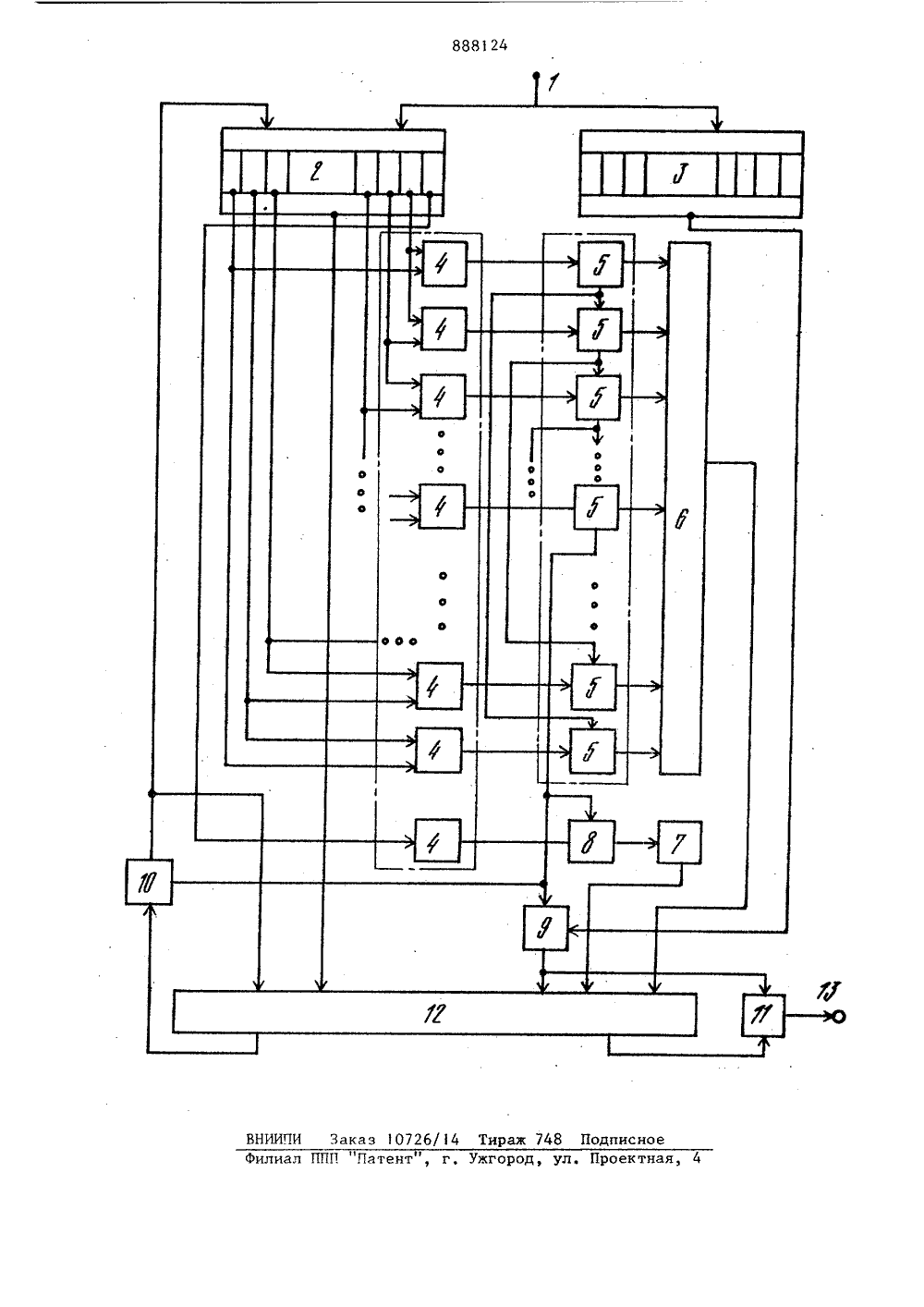

Союз Советски кСоциалнстическикРеспублик Оп ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 888124ло делам изооретеиий и открытийДата опубликования описания 07.12.81(54) УСТРОЙСТВО ДЛЯ ОБНАРЛ(ЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ Изобретение относится к областивычислительной техники и может быть использовано в вычислительных машинах и системах, работающих в непозиционной системе счисления остаточных классов (СОК),Известно устройство для обнаружения и исправления ошибок в СОК,содержащее подключенные к входнымшинам операционный и запоминающийрегистры с И выходами, дешифраторы,блоки памяти констант нулевизациии ошибок, сумматор, переключатели,вентили и ключи 11 ,Недостатком устройства являетсянизкое быстродействие.Наиболее близким к изобретениютехническим решением является устройство для обчаружения и исправления ошибок в СОК, содержащее подключенные ко входу устройства операционный и запоминающий регистрыс И выходами, дешифраторы, блоки .памяти кон таит нулевизации и ошибок, сумматор; переключатели, вентили и ключи. Причем 1 -й и (И-т++1) -й выходы операционного регистра подключены ко входам соответствующих дешифраторов, выходы которых 5через последовательно включенные переключатели соединены со входнымишинами блока памяти констант нулевизации. Выходы операционного регистра через дешифратор и подключенные к последнему переключателю вентили подсоединены к блоку памятиконстант ошибок. Выходы операционного регистра и блока памяти константнулевизации и констант ошибок непосредственно, а выходы запоминающегорегистра через присоединенныЕ к последнему переключателю входные вентили подключены ко входам сумматора, выходы которого через вентилизапрета соединены со входами операционного регистра и через выходныеключи подключены к выходным шинам устройства 21,8881 20 Недостатком устройства являетсянизкое быстродействие, так как выполнение операций сложения и выборки очередной константы нулевизацииразнесены во времени.Цель изобретения - повышение быстродействия.Поставленная цель достигаетсятем, что в устройстве, содержащемподключенные ко входу устройства первыми входами операционный и запоминающий регистры с И+ выходами,группу из И+1 дешифраторов, блокипамяти констант нулевизации и ошибок, сумматор, первую, вторую итретью группы элементов И, группувыходных ключей, подключенных выходами к выходным нинам устройства и группу из И переключателей, выходы первого и И-го разрядов операционного регистра подключены ковходам первого дешифратора группы,- выход 1,И+1)-го разряда операционного регистра, подключен ко входу (1+ +1) -го дешифратора группы, выходыкоторого подключены к первым входамэлементов и первой группы, выходами подключенных к адресным входам блока памяти констант ошибок,выход которого соединен с первымвходом сумматора . Причем информационные входы переключателей группы соединены с выходами соответствующих первых К дешифраторов группы,а первые выходы - с адресными входами блока памяти констант нулевизации, выход которого соединен.со вторым входом сумматора. Выходы запоминающего регистра подключены к первым входам элементов И второй группы, первые входы которых соединенысо вторыми входами элементов И первой группы и с первыми входами элементов И третьей группы, вторые входы которых подключены к группе первых выходов сумматора, а выходы -ко вторым входам операционного регистра, вторая группа выходов сумматора соединена с первыми входами выходных ключей группы, вторые входыкоторых подключены к выходам элементов И второй группы и к третьей группе входов сумматора. Выходы операционного регистра подключены к группе четвертых входов сумматора, вторая группа выходов 1 -го 11 =1,2, (ю 10-1, при Д четном; , И =12 (ф ф)-1 при 1 нечетном) переключателя гртппы соединена с 2 чвторой группой информационных входов ( +1 +1)-го переключателя группы, вторая группа выходов 1 -го переключателя группы соединена со второй группой информационных входов (1+1 -1 )-го переключателя группы, Вторая группа выходов И(2 - го ( при И - четном) или И)фЕ(при И - нечетном) переключателя группы подключена ко вторым входам элементов И первой группы, Входы 1 -го дешифратора (1 =23 и) подключена к 1 -му и 1,1 +1)-му выхо - дам операционного регистра. Выходы элементов И третьей группы подключены к пятой группе входов сумматора.Известен способ обнаружения и исправления ошибок в СОК.Пусть дано число А=(01 ( С 1) в СОК. Где Р 1 = Р+,1 соответственно информационные и контрольные основания. Производим нулевизацию числа А одновременно по двум информационным основаниям Р- и Р9-1+1. Под нулевизацией понимается такой способ преобразования числа А , заданного в СОК, при котором на каждом этапе преобразования число нулевых цифр в представлении числа увеличивается (в данном случае на две цифры), и при этом преобразуемое число не выходит за границу числового интервала 0 в ; Р - 1, где Р= - Р,1 Р 2, Р) В конце нулевизации получим число А = ( 00,- )Если ; =О, то считаем, что ошибки нет. Если Д0 то ошибка существует и, обращаясь по значению в блок памяти констант ошибок, выбираем соответствующую константу. Эта константа подается на сумматор и вычитается из занесенного туда ранее исходного числа А, На выходе сумматора получим исправленное число.ПустьТ- время выборки констан. ты нулевизации из накопителя, а Тс - время сложения (вычитания) чисел сумматором. Тогда общее время, необходимое для нулевизации числа, равно: Привлекая форсированный режим работы накопителя констант (Трц ТсА)получим Т риац 1 ТслИзвестный вариант выполнения операции не оптимален с точки зрения быстродействия, поскольку выполнение888124 сложения и выборка очередной константы нулевизации разнесены во времени.В изобретении в некоторых временных тактах совмещаются операции суммирования и выборки очередной константы нулевизации, а также выборка очередной константы и подготовка значений цифр, по которым в следующем этапе нулевизации будет производиться 1 выборка очередной константы. Пока производится выборка константы нулевизации для числа 30 35 40 Процесс нулевизации происходит до тех пор, пока во всех остатках по информационным основаниям Р 1, Р , .Р не окажутся нули. При этом,Ивсе переключатели группы 5 окажутся открытыми, и сигнал со второго выхода среднего оставшегося переключателя группы 5 (при четном И) или со второго выхода любого из двух остав(О,ОО,С,С О 1,С 1,0,.,0,5 и )по значениям циФР С и 0 ,могутИ+быть подготовлены значения цифр СМ+1 иС 1 1, по которым в следующем этапе нулевизации будет нроизводиться выборка очередной константы. Действительно, те значения ЬС 1+.Ь СС 1 1, которые будут вычтены соответственно из С 1+, и Сссопределяются только зиачениями ссс 1.и О И 11.1, Таким образом, в процессе выборки константы по значениям Си С 11 из накопителя могут быть выбраны значения О+1 и О И 1 . В этом случае необхо 1,димо ввести в устройство - прототип и) коммутатор-дешифратор (таблицы) в которых по значениям О и О 1+1 выбирается значение Сс1+СДля приведенного выше вида числа пРи опРеделении цифР Сс, и О необходимо иметь два коммутатора(таблицы) размером Р 1 Р 1.+, и Р Рс 1 1И+1 1-1 соответственно. В случае такой нулевизации нет необходимости иметь в накопителе констант нулевизации цифры по основаниям Р и РОбщее время нулевиэации числа в изобретении определится какТО я О, 75 .тсЬ На чертеже представлена структурная схема устройства.Оно содержит входные шины 1 устройства, операционный регистр 2, запоминающий регистр 3 группа дешифраторов 4, группу переключателей5, блок памяти констант нулевизации б, блок памяти констант ошибок 7, первую, вторую и третью группы элементов И 8, 9, 10 группу выходных ключей 11 .и сумматор 12. Устройство работает следующим образом.В начальном состоянии первый переключатель группы 5 открыт, а остальные переключатели группы закрыты.Закрыты также элементы И групп 8,9 и ключи группы 11. В регистры 2 и3 по входным шинам 1 занесено исхоДное число Ь =С 1,0 гс."с Ос 1+ )В первом такте из регистра 2 считывается значение числа А и поступает на четвертый вход сумматора 12.По значениям 01 и Счерез первыйдешифратор группы 4, определяющийадрес константы нулевизации, и открытый первый переключатель группы 5из блока памяти констант нулевизации6 выбирается константа нулевизации,Одновременно во втором и (11-2 )-м дешифраторах группы 4 соответственно по значениям С 1 С. и С 11 01,с оп1 2. Иределяются значения цифр, соответственно О 1 и Ос 1,Спо котоРым наследующем этапе нулевизации выбирается следующая константа. оВ следующем такте выбранная константа вычитается из содержимогосумматора 12 (т.е. из исходного чис.ла А). Одновременно производится обращение в блок 6 за константойнулевизации по значениям С 1 и С 1,1,1 Второй и И) - й переключатели груйпы 5 открыты второй выходной шиной переключателя группы 5.В следующем также содержимое сумматора 12 (результат операции) через элементы И третьей группы 10 поступает на регистр 2, и по шине перезаписи одновременно с константой нулевизации из блока б поступает по пятому входу вновь на сумматор 1 2, где производится очередное сложение (операция нулевизации), Одновременно в третьем и ( И)-м дешифраторах группы 4 определяются знас чения цифр соответственно Ои О 1 у. Третий и (,с 1-2 )-й переключатели группы 5 открыты второй выходной шиной переключателя группы 5.88812 Формула изобретения Устройство для обнаружения и исправления ошибок в системе остаточных классон, содержащее подключенные к его входу первыми группами входов операционный и запоминающий регистры с 1 + 1 выходами р группу из И+ 1 дешифраторов, блок памяти констант нулевизации, блок памяти констант ошибок, сумматор, первую, вторую и третью группы элементов И, группу выходных ключей, подключенных выходами к выходным шинам устройства и группу из 1 переключателей, причем выходы первого и И-го разрядов операционного регистра подключены к входам первого дешифратора группы, выход (И+1)-го разряда операционного регистра подключен к входу (И + +1)-го дешнфратора группы, выходы которого подключены к первым входам элементов И первой группы, выходами подключенных к адресным входам блока памяти констант ошибок, выход которого соединен с первым входом сумматора, первые информационные входы переключателей группы соединены с 50 7шихся средних переключателей (при нечетном И ), открывает элементы И групп 8 и 9 и закрывает элементы И группы 10. Далее содержимое регистра 3 через элементы И группы 9 за 3 носится в сумматор 12, Одновременно сигналом с выхода элементов И группы 9 открываются ключи группы 11. Если на выходе последнего дешифратора группы 4 появится ненулевой сигналто он через элементы И группы 8 поступает на блок памяти констант ошибок 7, где выбирается соответствующая константа, Эта константа подается на сумматор 12 и вычитается из занесенного туда ранее из регистра 3 числа А, Исправленное число через клячи группы 1 поступает на выход13 устройства. Если нет ошибки(Д =0), то число из сумматора 12 через клячи группы 11 поступает на выход 13,Таким образом, быстродействие предлагаемого устройства существенно повышено. выходами соответствующих первых Идешифраторов группы, а первые выходы - с адресными входами блока памяти констант нулевизации, выход которого соединен со вторым входом сумматора, выходы запоминающего регистра подключены к первым входам элементов И второй группы, первые входыкоторых соединены со вторыми входами элементов И первой группы и с первыми входами элементов И третьей груп.пы, вторые входы которых подключенык первой группе выходов сумматора,а выходы - ко второй группе входовоперационного регистра, вторая группа выходов сумматора соединена спервыми входами выходных ключей, вторые входы которых подключены к выходам элементов И второй группы и ктретьей группе входов сумматора, выходы операционного регистра подключены к четвертой группе входов сумматора, вторая группа выходов 1 -го. =1,2(И l2)-1 при р нечетномпереключателя группы соединена с второй группой информационных входов(1 + ) - го переключателя группы, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия втораягруппа выходов-го переключателягруппы соединена с второй группойинформационных входов (+1-)-гопереключателя группы, вторая группа выходов(ИЯ) -го (при И четном)или(И)-го ( принечетном ) переключателя группы подключена к вторымвходам элементов И первой группы,входы 1 -го дешифратора (=1,2И)подключены к 1 и (1 +1 ) - му выходам операционного регистра, выходы элементов И третьей группы подключены к пятой группе входов сумматора. Источники информации,принятые во внимание при экспертизе1. Анушский И.Я.,Одицкий Д.И.Машинная арифметика в остаточныхклассах, М., "Советское радио", 1968,с, 351-358.2, Авторское свидетельство СССР1 369567, кл. 0 06 Г 11/04, 1973

СмотретьЗаявка

2892052, 05.03.1980

ВОЙСКОВАЯ ЧАСТЬ 11284

КРАСНОБАЕВ ВИКТОР АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: исправления, классов, обнаружения, остаточных, ошибок, системе

Опубликовано: 07.12.1981

Код ссылки

<a href="https://patents.su/5-888124-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok-v-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок в системе остаточных классов</a>

Предыдущий патент: Устройство для контроля цифровых объектов

Следующий патент: Устройство для коррекции сбойных кодов в кольцевом распределителе

Случайный патент: Захватно-срезающее устройство лесозаготовительной машины