Устройство для обнаружения и исправления однократных ошибок оптимальных р-кодов фибоначчи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

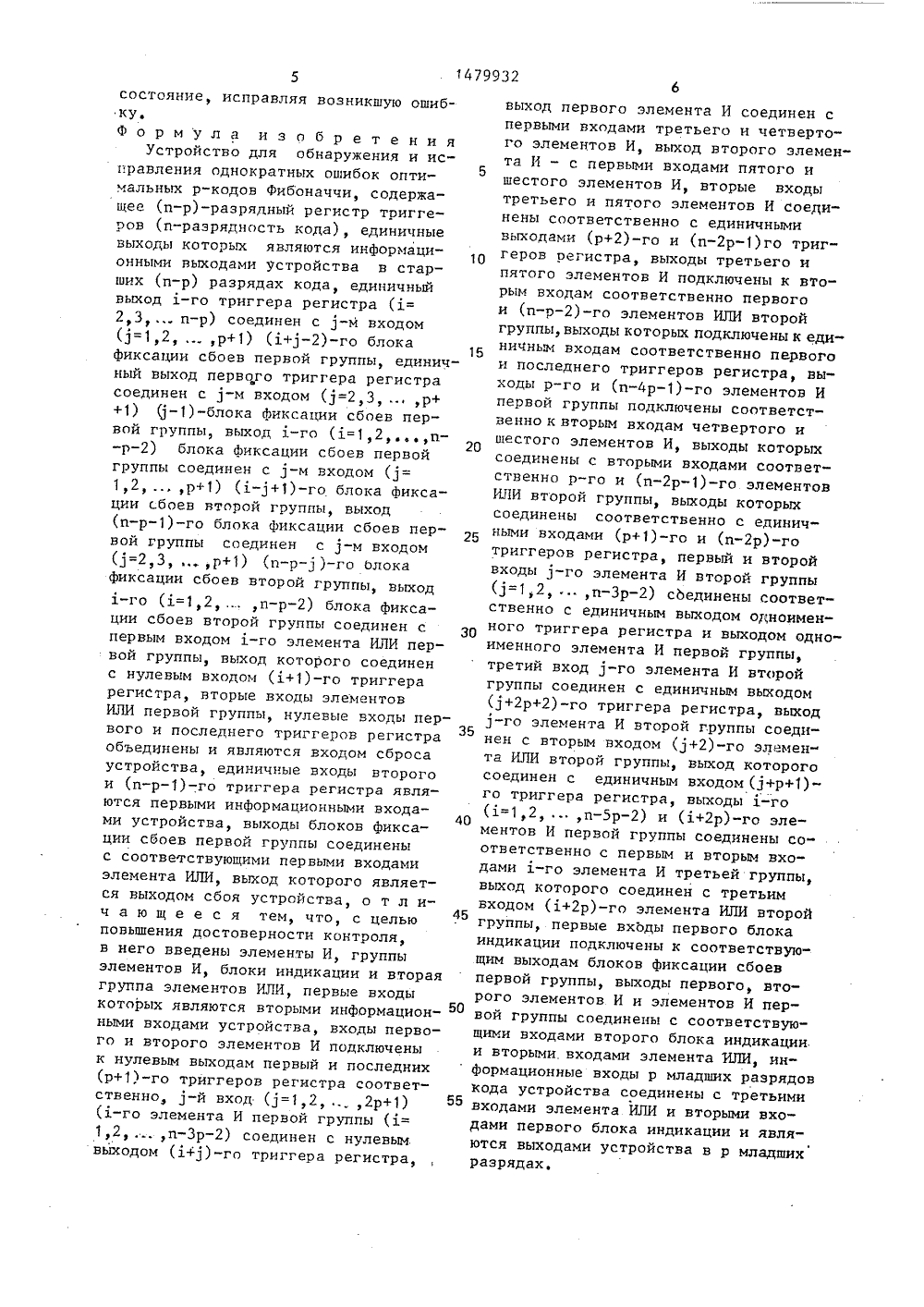

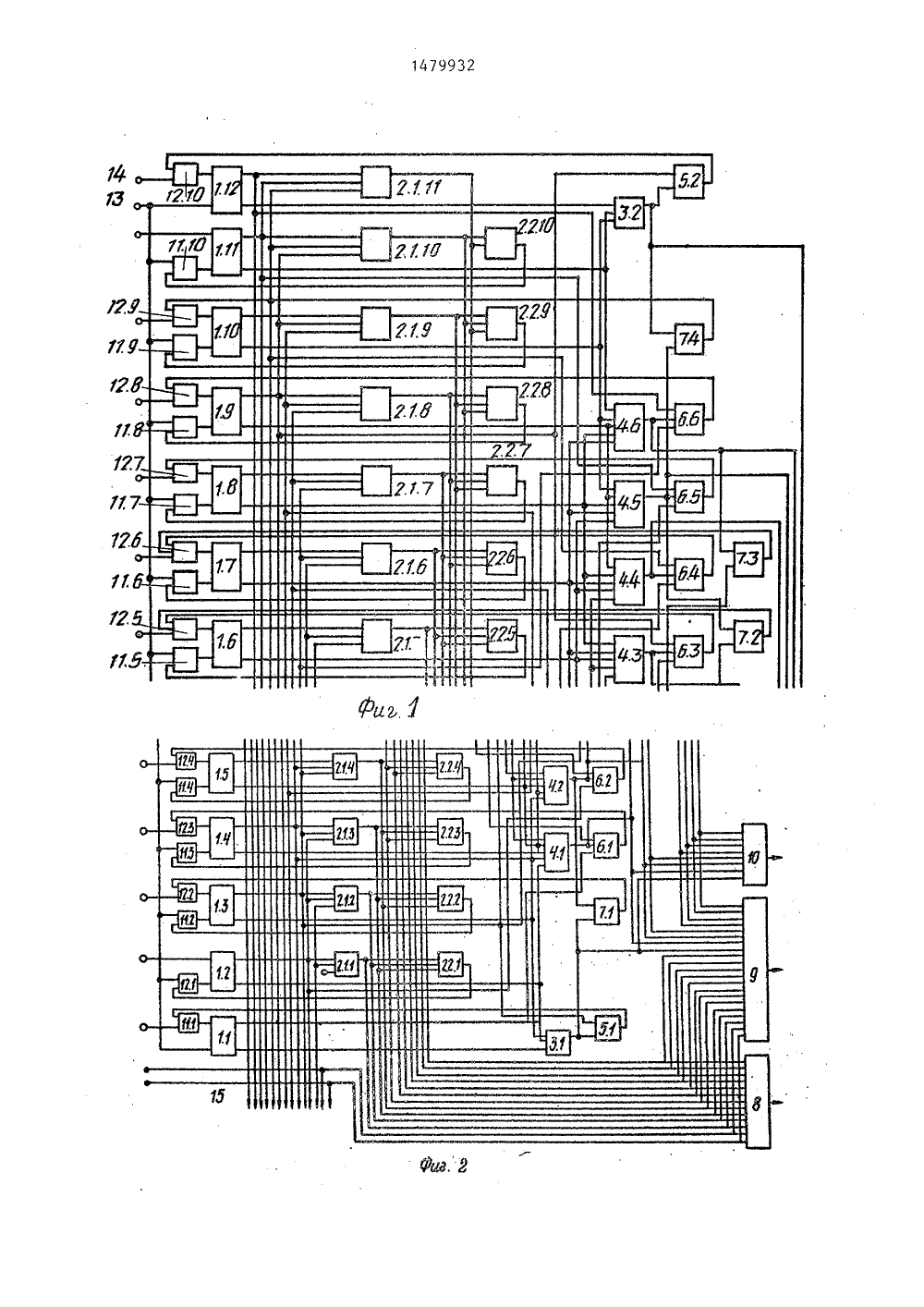

РФ1 Р(п-р-,1), при и р, Числа В(В=О 11 (и)-1) и е ставлМетод исправления ошибок в ш-м оптимальной Формой: разряде оптимального р-кода ФибоначБ = ОО О 1 ОО 01 ООО 11 ОО О 1 пи описывается булевьыи функциямицт е фш =О, р тп 1=р,2 Р (3 =1 ф к)1.О 1. О 1-0 - 1-0 1-0 бЕ = (ХХ тО р) (ХОр,у 1 Х 1 ут-йр 1 1 п.1 О) к 15 2,1.10 и 2.1.11 поступают соответственно на входы 18 и 7 блока 2,2,10и вызывают его срабатывание. Единичный сигнал с выхода блока 2,2,10через элемент ИЛИ 11.10 поступаетна нулевой .вход триггера 1.11 и об"нуляет его, исправляя таким образомошибку,где Х, - сигнал на выходе 1-гоблока фиксации сбоев;Х, - сигнал выхода (2 р+1)-входового элемента И.Сущность изобретения заключаетсяв реализации Формул, представленныхвыше,Устройство работает следующимобразом,В исходном состоянии после подачина вход 13 сброса устройства единичного сигнала триггеры 1 устанавливаются в нулевое состояние. Предположим что в регистре необходимо храв30нить код числа 27, представленногов оптимальной форме оптимального ркода Фибоначчи,в ниде 100100100100007,Этот код параллельным образом заносится в триггеры 1, Предположим, чтопод действием помехи триггер 1,11 35переходит в единичное состояние икод принимает вид 11010010010000.Единичный сигнал, поступая с единичного выхода триггера 1,1 1 на вход 18блока 2,1,10 Фиксации сбоев, вызывает срабатывание этого блока. Единичный сигнал с выхода блока 2.1.10 поступает на блок 8, сигнализируя отом, что в группе триггеров 1,9-1,11произошел сбой, т.е. переход "0" в 45"1", которая через элемент ИЛИ 9устанавливается на выходе сбоя устройства.Кроме того, единичный сигнал сединичного выхода триггера 1,.11 поступает на вход 17 блока 2,111 ивызывает его срабатывание, Единичныйсигнал с выхода блока 2,.11 1 поступает на блок 8 индикации, сигнализируя о том, что в группе триггеров1.10-1,12 произошел сбой, т,е. переход "0" в "1", Единчй сигнал поступает и на вход элемента ИЛИ 9,Единичные сигналы с, выходом блоковЕсли же под действием помехи триггер 1.2 переходит в единичное состояние, то код принимает вид 10010010011000, В этом случае срабатывает блок 2,1,2, Единичный потенциал с его выхода через элемент ИЛИ 9 устанавливается на выходе сбоя устройства, сигнализируя об искажении кода, Одновременно сигнал поступает на блок 8 индикации, Сбой обна-. руживается, но не исправляется,Устройство позволяет также обнаружить все и исправить часть однократных сбоев типа переход 1 в "0", Предположим, что под действием помехи триггер 1,12 переходит в нулевое состояние, Тогда код принимает вид 00010010010000. На нулевом выходе триггера 1.12 появляется единичный сигнал, который устанавливается на третьем входе элемента И 3,2. Элемент И 3,2 срабатывает, единичный сигнал с его выхода поступает на блок 10 индикации, указывая на то, что группе триггеров 1.10-1.12 происходит сбой типа переход "1" в "0", и через элемент ИЛИ 9 поступает на выход сбоя устройства. Кроме того, единичный сигнал с выхода элемента И 3.2 поступает на второй вход элемента И 5,2 и вызывает его срабатывание, Сигнал с выхода эле" мента И 5,2 поступает через элемент ИЛИ 1.2,10 на единичный вход триггера 1.12 и переводит его в единичное55 состояние, исправляя возникшую ошибку,Формула изобретенияУстройство для обнаружения и исправления однократных ошибок оптимальных р-кодов Фибоначчи, содержащее (и-р)-разрядный регистр триггеров (п-разрядность кода), единичныевыходы которых являются информационными выходами устройства в старших (п-р) разрядах кода, единичныйвыход -го триггера регистра (=2,3, п-р) соединен с 1-м входом(3=1,2, ,р+1) (д+1-2)-го блокафиксации сбоев первой группы, единичный выход первого триггера регистрасоединен с 1-м входом (=2,3, ,р++1) Ц)-блока фиксации сбоев первой группы, выход -го (.=1,2 п-р) блока фиксации сбоев первойгруппы соединен с 1-м входом (1=1,2р+1) (-1+1)-го блока фиксации сбоев второй группы, выход(и-р)-го блока фиксации сбоев первой группы соединен с 1-и входом(1=2,3, .,р+1) (и-р) - го блокафиксации сбоев второй группы, выходд-го (=1,2п-р) блока фиксации сбоев второй группы соединен спервым входом х-го элемента ИЛИ первой группы, выход которого соединенс нулевым входом (д+1)-го триггерарегистра, вторые входы элементовИЛИ первой группы, нулевые входы первого и последнего триггеров регистраобъединены и являются входом сбросаустройства, единичные входы второгои (и-р)-го триггера регистра являются первыми информационными входами устройства, выходы блоков фиксации сбоев первой группы соединеныс соотвегствующими первыми входамиэлемента ИЛИ, выход которого является выходом сбоя устройства, о т л ич а ю щ е е с я тем, что, с цельюповышения достоверности контроля,в него введены элементы И, группыэлементов И, блоки индикации и втораягруппа элементов ИЛИ, первые входыкоторых являются вторыми информационными входами устройства, входы первого и второго элементов И подключенык нулевым выходам первый и последних(-го элемента И первой группы (1=1,2п-Зр) соединен с нулевым.выходом (+) -го триггера регистра,5 10 15 20 25 30 35 40 45 50 выход первого элемента И соединен спервыми входами третьего и четвертого элементов И, выход второго элемента И - с первыми входами пятого ишестого элементов И, вторые входытретьего и пятого элементов И соединены соответственно с единичнымивыходами (р+2)-го и (пр)го триггеров регистра, выходы третьего ипятого элементов И подключены к вторым входам соответственно первогои (и-р) -го элементов ИЛИ второйгруппы, выходы которых подключены к единичным входам соответственно первогои последнего триггеров регистра, выходы р-го и (ир)-го элементов Ипервой группы подключены соответственно к вторым входам четвертого ишестого элементов И, выходы которыхсоединены с вторыми входами соответственно р-го и (ир)-го элементовИЛИ второй группы, выходы которыхсоединены соответственно с единичными входами (р+1)-го и (ир)-готриггеров регистра, первый и второйвходы 1-го элемента И второй группы(1=1,2",и-Зр) сдединены соответственно с единичным выходом одноименного триггера регистра и выходом одноименного элемента И первои группы,третий вход 1-го элемента И второйгруппы соединен с единичным выходом(1+2 р+2) -го триггера регистра, выход1-го элемента И второй группы соединен с вторым входом (1+2)-го элемента ИЛИ второй группы, выход которогосоединен с единичным входом (3+р+1)го триггера регистра, выходы -го(1=1,2, .- ,ир) и (+2 р)-го элементов И первой группы соединены соответственно с первым и вторым входами -го элемента И третьей группы,выход которого соединен с третьимвходом (+2 р)-го элемента ИЛИ второйгруппы, первые входы первого блокаиндикации подключены к соответствующим выходам блоков фиксации сбоевпервой группы, выходы первого, второго элементов И и элементов И первой группы соединены с соответствующими входами второго блока индикации.и вторыми входами элемента ИЛИ, информационные входы р младших разрядов Кода устройства соединены с третьими входами элемента ИЛИ и вторыми входами первого блока индикации и являются выходами устройства в р младших разрядах.1479932 Составитель О,Неплохов Техред М,Ходанич Корректор М,Васильева Редактор А.Ревин Заказ 254346 Тираж 669 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская араб., д. 4/5Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,10

СмотретьЗаявка

4186285, 23.01.1987

КРАСНОДАРСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК

ТКАЧЕНКО АЛЕКСАНДР ВАСИЛЬЕВИЧ, ГРИГОРЬЕВ НИКОЛАЙ ФЕДОРОВИЧ

МПК / Метки

МПК: H03M 13/53

Метки: исправления, обнаружения, однократных, оптимальных, ошибок, р-кодов, фибоначчи

Опубликовано: 15.05.1989

Код ссылки

<a href="https://patents.su/5-1479932-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-odnokratnykh-oshibok-optimalnykh-r-kodov-fibonachchi.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления однократных ошибок оптимальных р-кодов фибоначчи</a>

Предыдущий патент: Многоканальное устройство для подключения источников информации к общей магистрали

Следующий патент: Устройство для контроля кода

Случайный патент: Сверхскоростной фоторегистратор