Устройство для формированияиспытательного tekcta

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 803118

Авторы: Заславский, Ройзин, Трест

Текст

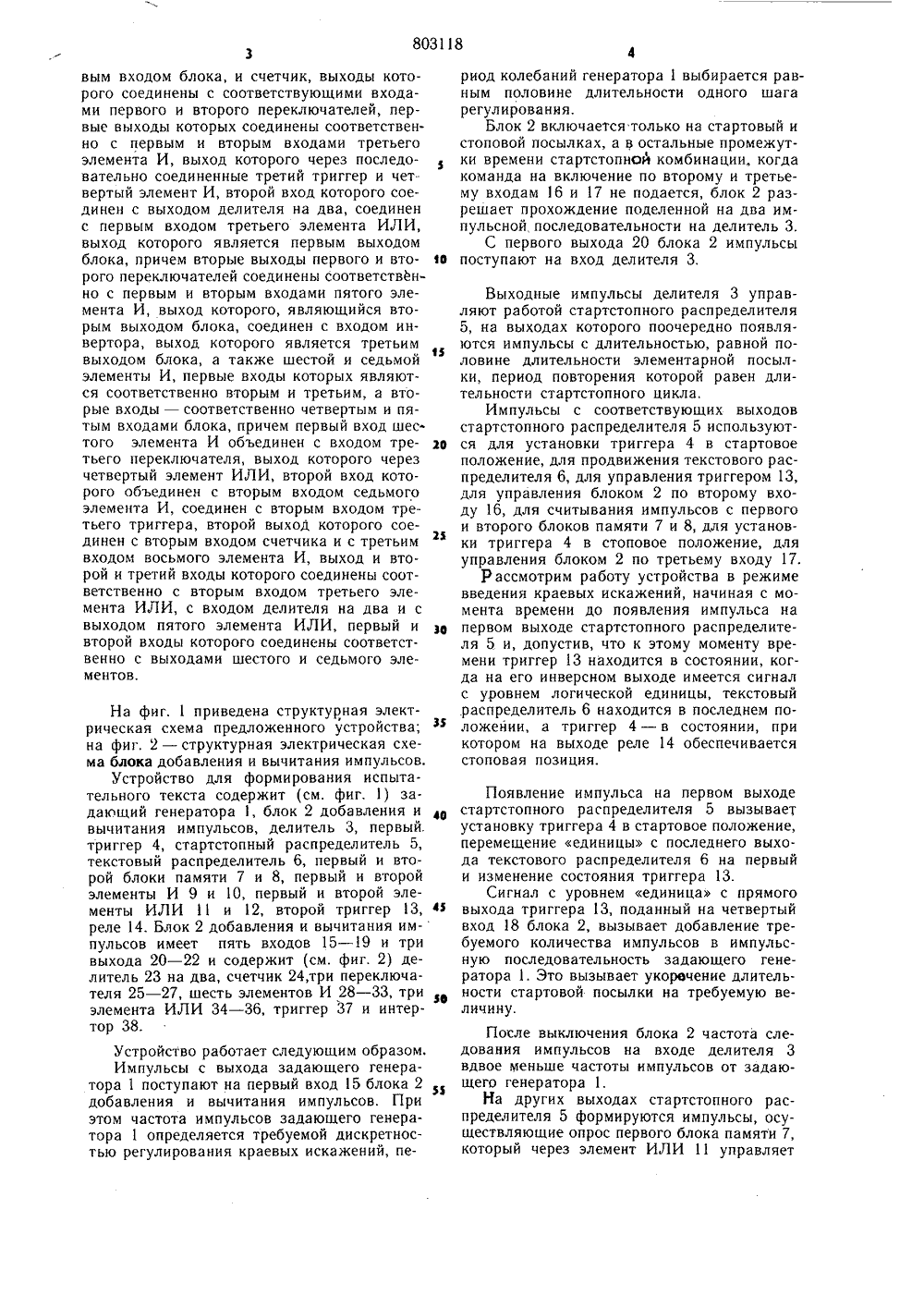

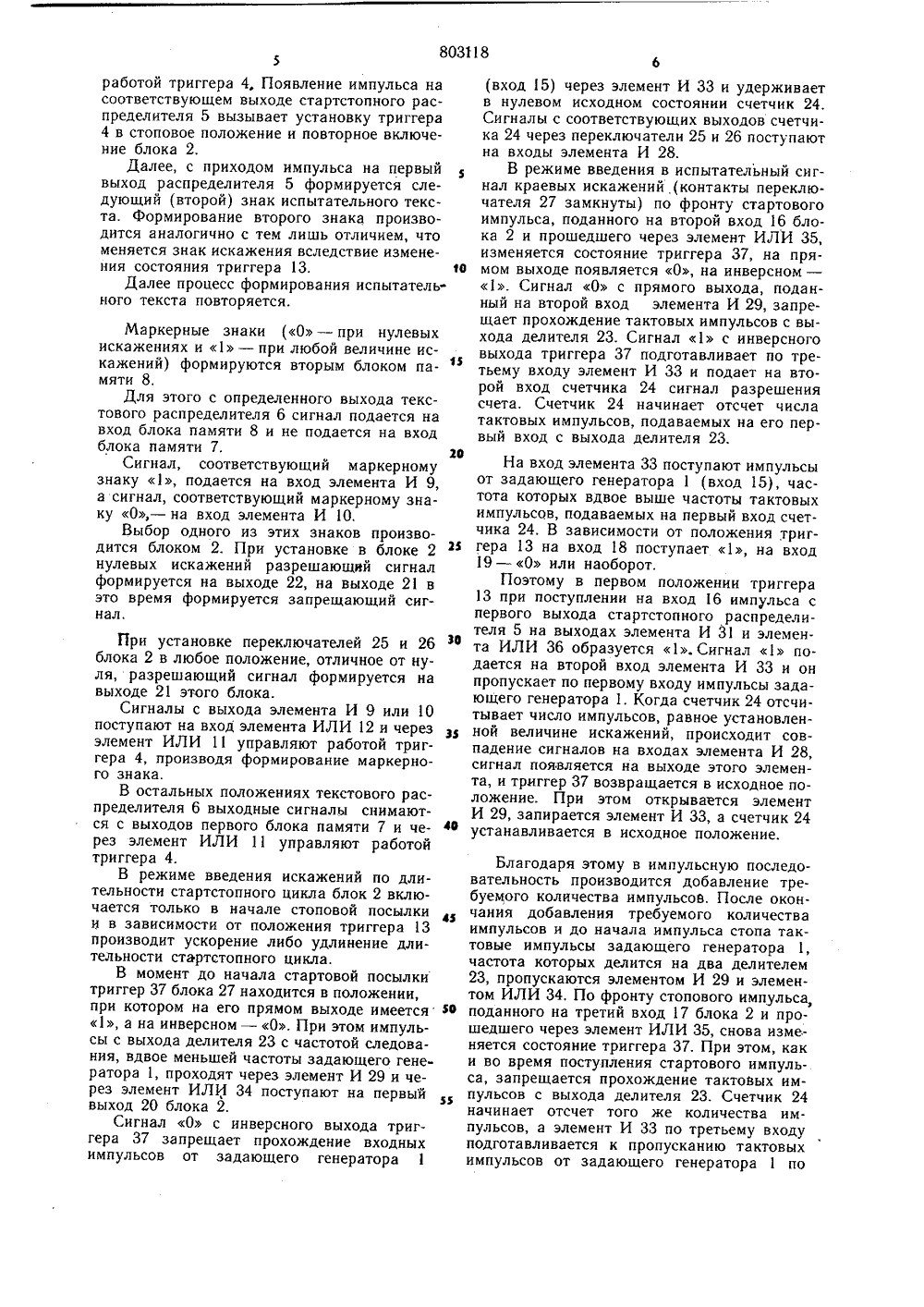

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик 11803118ло делам изобретений и открытей.(54) УСТРОЛСТВО ДЛЯ ФОРМИРОВАНИЯ ИСПЫТАТЕЛЬНОГО ТЕКСТАИзобретение относится к радиотехникеи может использоваться в телеграфии. Известно устройство для формирования испытательного текста, содержащее задающий генератор, последовательно соединенные делитель, стартстопный распределитель, первый блок памяти и второй блок памяти, первый и второй маркерные входы которого объединены, последовательно соединенные первый элемент ИЛИ, вход которого соединен с объединенными соответствующими выходами первого блока памяти, первый триггер и реле, а также первый и второй элементы И, выходы которых соединены соответственно с первым и вторым входами второго элемента ИЛИ, второй триггер и текстовый распределитель, сигнальные выходы которого соединены с соответствующими входами первого блока памяти, а вход текстового распределителя соединен с входом второго триггера, с стартовым входом первого триггера и с стартовым выходом стартстопного распределителя, стоповый выход которого соединен с стоповым входом первого триггера 11. Однако известное устройство не обеспечивает формирование теста с переменной длительностью стартстопного цикла.Целью изобретения является обеспечение формирования текста с переменной дли 5 тельностью стартстопного цикла,Для этого в известное устройство дляформирования испытательного текста введенблок добавления и вычитания импульсов,при этом первый, второй, третий, четвертыйи пятый входы и первый, второй и третий1 О выходы блока добавления и вычитания импульсов соединены соответственно с выходом Задающего генератора, с стартстопными стоповым выходами стартстопного распределителя, с первым и вторым выходами второго триггера, с входом делителя и с первыми входами первого и второго элементовИ, вторые входы которых соединены соответственно с первым и вторым выходами второго блока памяти, маркерные входы которого соединены с маркерным выходом текстово вого распределителя.Кроме того, блок добавления и вычитания содержит последовательно соединенныеделитель на два, вход которого является пер 803118вым входом блока, и счетчик, выходы которого соединены с соответствующими входами первого и второго переключателей, первые выходы которых соединены соответственно с первым и вторым входами третьего элемента И, выход которого через последовательно соединенные третий триггер и четвертый элемент И, второй вход которого соединен с выходом делителя на два, соединен с первым входом третьего элемента ИЛИ, выход которого является первым выходом блока, причем вторые выходы первого и вто ф рого переключателей соединены соответственно с первым и вторым входами пятого элемента И, выход которого, являющийся вторым выходом блока, соединен с входом инвертора, выход которого является третьим15 выходом блока, а также шестой и седьмой элементы И, первые входы которых являются соответственно вторым и третьим, а вторые входы - соответственно четвертым и пятым входами блока, причем первый вход шестого элемента И объединен с входом тре- т тьего переключателя, выход которого через четвертый элемент ИЛИ, второй вход которого объединен с вторым входом седьмого элемента И, соединен с вторым входом третьего триггера, второй выход которого соединен с вторым входом счетчика и с третьим ф входом восьмого элемента И, выход и второй и третий входы которого соединены соответственно с вторым входом третьего элемента ИЛИ, с входом делителя на два и с выходом пятого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами шестого и седьмого элементов. На фиг. 1 приведена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная электрическая схема блока добавления и вычитания импульсов.Устройство для формирования испытательного текста содержит (см. фиг. 1) задающий генератора 1, блок 2 добавления и вычитания импульсов, делитель 3, первый. триггер 4, стартстопный распределитель 5, текстовый распределитель 6, первый и второй блоки памяти 7 и 8, первый и второй элементы И 9 и 10, первый и второй элементы ИЛИ 11 и 12, второй триггер 13, 45 реле 14. Блок 2 добавления и вычитания импульсов имеет пять входов 15 - 19 и три выхода 20 - 22 и содержит (см. фиг. 2) делитель 23 на два, счетчик 24,три переключателя 25 - 27, шесть элементов И 28 - 33, три элемента ИЛИ 34 - 36, триггер 37 и интертор 38.Устройство работает следующим образом, Импульсы с выхода задающего генератора 1 поступают на первый вход 15 блока 2 добавления и вычитания импульсов. При этом частота импульсов задающего генератора 1 определяется требуемой дискретностью регулирования краевых искажений, период колебаний генератора 1 выбирается равным половине длительности одного шага регулирования.Блок 2 включается только на стартовый и стоповой посылках, а в остальные промежутки времени стартстопнои комбинации, когда команда на включение по второму и третьему входам 16 и 17 не подается, блок 2 разрешает прохождение поделенной на два импульсной последовательности на делитель 3.С первого выхода 20 блока 2 импульсы поступают на вход делителя 3.Выходные импульсы делителя 3 управляют работой стартстопного распределителя 5, на выходах которого поочередно появляются импульсы с длительностью, равной половине длительности элементарной посылки, период повторения которой равен длительности стартстопного цикла,Импульсы с соответствующих выходов стартстопного распределителя 5 используются для установки триггера 4 в стартовое положение, для продвижения текстового распределителя 6, для управления триггером 13, для управления блоком 2 по второму входу 16, для считывания импульсов с первого и второго блоков памяти 7 и 8, для установки триггера 4 в стоповое положение, для управления блоком 2 по третьему входу 17.Рассмотрим работу устройства в режиме введения краевых искажений, начиная с момента времени до появления импульса на первом выходе стартстопного распределителя 5 и, допустив, что к этому моменту времени триггер 13 находится в состоянии, когда на его инверсном выходе имеется сигнал с уровнем логической единицы, текстовый .распределитель 6 находится в последнем положении, а триггер 4 - в состоянии, при котором на выходе реле 14 обеспечивается стоповая позиция.Появление импульса на первом выходе стартстопного распределителя 5 вызывает установку триггера 4 в стартовое положение, перемещение единицы с последнего выхода текстового распределителя 6 на первый и изменение состояния триггера 13.Сигнал с уровнем единица с прямого выхода триггера 13, поданный на четвертый вход 18 блока 2, вызывает добавление требуемого количества импульсов в импульсную последовательность задающего генератора 1. Это вызывает укорвчение длительности стартовой посылки на требуемую величину.После выключения блока 2 частота следования импульсов на входе делителя 3 вдвое меньше частоты импульсов от задающего генератора 1,На других выходах стартстопного распределителя 5 формируются импульсы, осуществляющие опрос первого блока памяти 7, который через элемент ИЛИ 11 управляетработой триггера 4, Появление импульса на соответствующем выходе стартстопного распределителя 5 вызывает установку триггера 4 в стоповое положение и повторное включение блока 2.Далее, с приходом импульса на первый выход распределителя 5 формируется следующий (второй) знак испытательного текста. Формирование второго знака производится аналогично с тем лишь отличием, что меняется знак искажения вследствие изменения состояния триггера 13.Далее процесс формирования испытательного текста повторяется.Маркерные знаки (О - при нулевых искажениях и 1 - при любой величине искажений) формируются вторым блоком памяти 8,Для этого с определенного выхода текстового распределителя 6 сигнал подается на вход блока памяти 8 и не подается на вход блока памяти 7,Сигнал, соответствующий маркерному знаку 1, подается на вход элемента И 9, а сигнал, соответствующий маркерному знаку О, - на вход элемента И 10.Выбор одного из этих знаков производится блоком 2. При установке в блоке 2 нулевых искажений разрешающий сигнал формируется на выходе 22, на выходе 21 в это время формируется запрещающий сигнал.При установке переключателей 25 и 26 фф блока 2 в любое положение, отличное от нуля, разрешающий сигнал формируется на выходе 21 этого блока.Сигналы с выхода элемента И 9 или 10 поступают на вход элемента ИЛИ 12 и через элемент ИЛИ 11 управляют работой триггера 4, производя формирование маркерного знака.В остальных положениях текстового распределителя 6 выходные сигналы снимаются с выходов первого блока памяти 7 и че ф рез элемент ИЛИ 11 управляют работой триггера 4.В режиме введения искажений по длительности стартстопного цикла блок 2 включается только в начале стоповой посылки45 и в зависимости от положения триггера 13 производит ускорение либо удлинение длительности стартстопного цикла.В момент до начала стартовой посылки триггер 37 блока 27 находится в положении, при котором на его прямом выходе имеется фф 1, а на инверсном - О. При этом импульсы с выхода делителя 23 с частотой следования, вдвое меньшей частоты задающего генератора 1, проходят через элемент И 29 и через элемент ИЛИ 34 поступают на первый выход 20 блока 2.Сигнал О с инверсного выхода триггера 37 запрещает прохождение входных импульсов от задающего генератора 1(вход 15) через элемент И 33 и удерживает в нулевом исходном состоянии счетчик 24. Сигналы с соответствующих выходов счетчика 24 через переключатели 25 и 26 поступают на входы элемента И 28.В режиме введения в испытательный сигнал краевых искажений (контакты переключателя 27 замкнуты) по фронту стартового импульса, поданного на второй вход 16 блока 2 и прошедшего через элемент ИЛИ 35, изменяется состояние триггера 37, на прямом выходе появляется О, на инверсном - 1. Сигнал О с прямого выхода, поданный на второй вход элемента И 29, запрещает прохождение тактовых импульсов с выхода делителя 23. Сигнал 1 с инверсного выхода триггера 37 подготавливает по третьему входу элемент И 33 и подает на второй вход счетчика 24 сигнал разрешения счета. Счетчик 24 начинает отсчет числа тактовых импульсов, подаваемых на его первый вход с выхода делителя 23.На вход элемента 33 поступают импульсы от задающего генератора 1 (вход 15), частота которых вдвое выше частоты тактовых импульсов, подаваемых на первый вход счетчика 24, В зависимости от положения триггера 13 на вход 18 поступает 1, на вход 19 - О или наоборот.Поэтому в первом положении триггера 13 при поступлении на вход 16 импульса с первого выхода стартстопного распределителя 5 на выходах элемента И 31 и элемента ИЛИ 36 образуется 1. Сигнал 1 подается на второй вход элемента И 33 и он пропускает по первому входу импульсы задающего генератора 1. Когда счетчик 24 отсчитывает число импульсов, равное установленной величине искажений, происходит совпадение сигналов на входах элемента И 28, сигнал появляется на выходе этого элемента, и триггер 37 возвращается в исходное положение. При этом открывается элемент И 29, запирается элемент И 33, а счетчик 24 устанавливается в исходное положение. Благодаря этому в импульсную последовательность производится добавление требуемого количества импульсов, После окончания добавления требуемого количества импульсов и до начала импульса стопа тактовые импульсы задающего генератора 1, частота которых делится на два делителем 23, пропускаются элементом И 29 и элементом ИЛИ 34. По фронту стопового импульса, поданного на третий вход 17 блока 2 и прошедшего через элемент ИЛИ 35, снова изменяется состояние триггера 37. При этом, как и во время поступления стартового импульса, запрещается прохождение тактовых импульсов с выхода делителя 23. Счетчик 24 начинает отсчет того же количества импульсов, а элемент И ЗЗ по третьему входу подготавливается к пропусканию тактовых импульсов от задающего генератора 1 попервому входу элемента 33. Однако при принятом ранее положении триггера 13 (на четвертом входе 18 блока 2 сигнал 1, на пятом входе 19 - сигнал 0) на выходе элемента И 31 и элемента ИЛИ 36 имеется сигнал О, элемент И 33 закрыт, а на времяотсчета счетчиком 24 заданного количестватактовых импульсов импульсы на первомвыходе 20 блока 2 отсутствуют. После отсчета счетчиком 24 заданного количества тактовых импульсов триггер 37 возвращается висходное состояние и на первом выходе 20 1 облока 2 появляются тактовые импульсы с частотой, вдвое меньшей частоты задающегогенератора 1. Далее процесс повторяется стем отличием, что на следующем знаке триггер 13 изменяет свое положение. При этомона старте производится вычитание тактовыхимпульсов, а на стопе - добавление,В режиме внесения искажений по длительности (контакты переключателя 27 разомкнуты) на стартовой посылке добавлениеи вычитание тактовых импульсов не произ рводится. Оно производится только на стоповой посылке. Элемент И 30 обеспечиваетна втором выходе 21 блока 2 формированиесигнала 1 при установке переключателей25 и 26 в положение О. Во всех остальныхположениях переключателей 25 и 26 на втоиром выходе 21 блока 2 имеется О. Инвертор 38 на третьем выходе 22 блока 2 обеспечивает инвертирование сигналов на второмвыходе 21.Предложенное устройство вводит в ис- зопытательный сигнал как краевые искажения,так и искажения по длительности стартстопного цикла испытательных сигналов. Эторасширяет функциональные возможностиустройства и способствует повышению достоверности результатов испытания работы око- знечной и каналообразующей аппаратуры и,как следствие, этого - повышение надежности ее работы.Формула изобретенияаю1. Устройство для формирования испытательного текста, содержащее задающий генератор, последовательно соединенные делитель, стартстопный распределитель, первый блок памяти и второй блок памяти, первый и второй маркерные входы которого объединены, последовательно соединенные первый элемент ИЛИ, вход которого соединен с объединенными соответствующими выходами первого блока памяти, первый триггер и реле, а также первый и второй эле- юв менты И, выходы которых соединены соответственно с первым и вторым входами второго элемента ИЛИ, второй триггер и текстовый распределитель, сигнальные выходы которого соединены с соответствующими входами первого блока памяти, а вход тексто 55 вого распределителя соединен с входом второго триггера, с стартовым входом первого триггера и с стартовым выходом стартстопного распределителя, стоповый выход которого соединен с стоповым входом первого триггера, отличающееся тем, что, с целью обеспечения формирования текста с переменной длительностью стартстопного цикла, введен блок добавления и вычитания импульсов, при этом первый, второй, третий, четвертый и пятый входы и первый, второй и третий выходы блока добавления и вычитания импульсов соединены соответственно с выходом задающего генератора, с стартовым и стоповым выходами стартстопного распределителя, с первым и вторым выходами второго триггера, с входом делителя и с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с первым и вторым выходами второго блока памяти, маркерные входы которого соединены с маркерным выходом текстового распределителя,2. Устройство по п. 1, отличающееся тем, что блок добавления и вычитания импульсов содержит последовательно соединенные делитель на два, вход которого является первым входом блока,и счетчик, выходы которого соединены с соответствующими входами первого и второго переключателей, первые выходы которых соединены соответственно с первым и вторым входами третьего элемента И, выход которого через последовательно соединенные третий триггер и четвертый элемент И, второй вход которого соединен с выходом делителя на два, соединен с первым входом третьего элемента ИЛИ, выход которого является первым выходом блока, причем вторые выходы первого и второго переключателей соединены соответствено с первым и вторым входами пятого элемента И, выход которого, являющийся вторым выходом блока, соединен с входом инвертора, выход которого является третьим выходом блока, а также шестой и седьмой элементы И, первые входы которых являются соответственно вторым и третьим, а вторые входы - соответственно четвертым и пятым входами блока, причем первый вход шестого элемента И объединен с входом третьего переключателя, выход которого через четвертый, элемент ИЛИ, второй вход которого объединен с вторым входом седьмого элемента И, соединен с вторым входом третьего триггера, второй выход которого соединен с вторь;м входом счетчика и с третьим входом восьмого элемента И, выход и второй и третий входы которого соединены соответственно с вторым входом третьего элемента ИЛИ, с входом делителя на два и с выходом пятого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами шестого и седьмого элементов И.Источники информации,принятые во внимание при экспертизе 1. Балтер 1 О. Б. и др. Новые телеграфные измерительные приборы. М., Связь, 1972, с, 43 - 47 (прототип).

СмотретьЗаявка

2706698, 04.01.1979

ПРЕДПРИЯТИЕ ПЯ В-8791

ЗАСЛАВСКИЙ ВИКТОР ИЗРАИЛЕВИЧ, РОЙЗИН ВЛАДИМИР ЛЬВОВИЧ, ТРЕСТ АРОН ИСААКОВИЧ

МПК / Метки

МПК: H04L 11/08

Метки: tekcta, формированияиспытательного

Опубликовано: 07.02.1981

Код ссылки

<a href="https://patents.su/5-803118-ustrojjstvo-dlya-formirovaniyaispytatelnogo-tekcta.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формированияиспытательного tekcta</a>

Предыдущий патент: Устройство для измерения характеристиксистем цикловой синхронизации

Следующий патент: Устройство для приема двоичныхсигналов

Случайный патент: Устройство коррекции для канала цветности системы секам