Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 744587

Авторы: Аноприенко, Калашник, Сирота, Харитонов

Текст

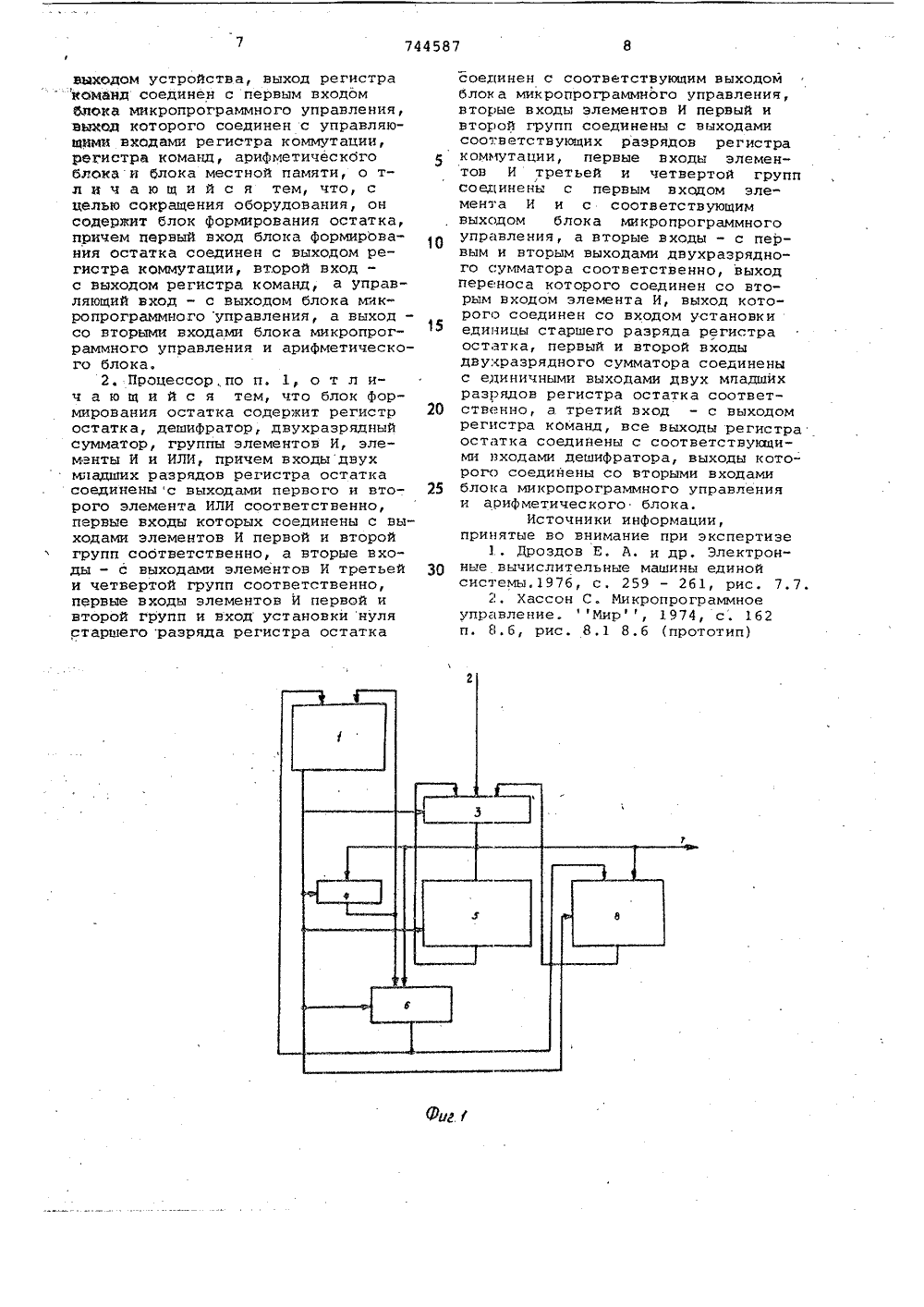

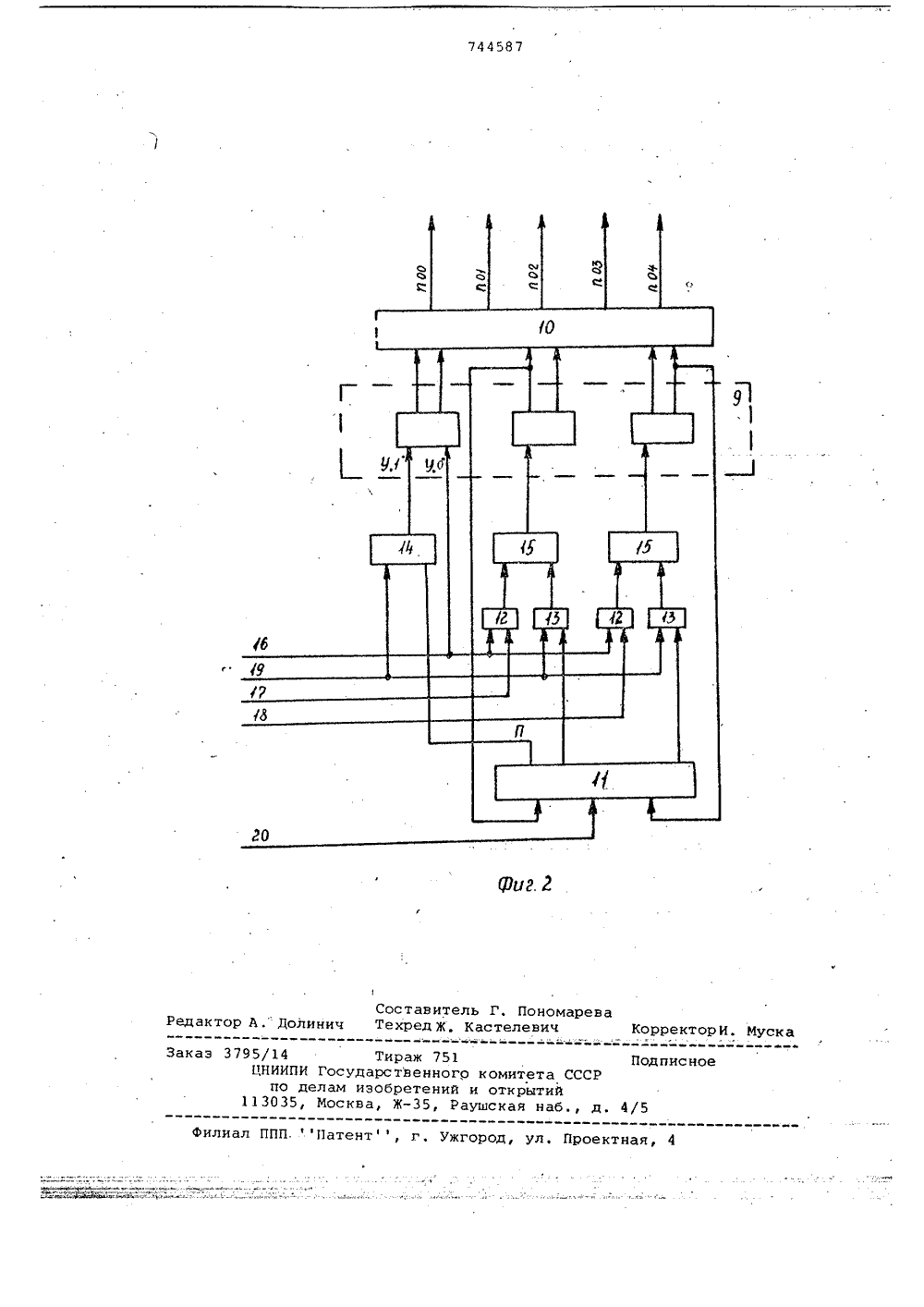

Союз Советскик Социалистическик Республик(22) Заявлено 030478 (21) 2600631/18-24с присоединением заявки Ио -(23) Приоритет -Опубликовано 300680. Бюллетень Мо 24Дата опубликования описания 300680 С 06 Г 15/00 Государственный комитет СССР по делам изобретениИ и открытийКиевский ордена Трудового Красного Знамени завод вычислительных и управляющих машин(54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР Изобретение относится к вычислительной технике и может применятьсяв цифровых вычислительных машинах спрограммным управлением,Известен процессор ЕС 1020, которыйдля подсчета текущего адреса команды использует арифметический блок,где после очередного считывания иэоперативной памяти полуслова (двабайта) происходит увеличение текущего адреса командной информации надва 1 .Текущий адрес хранится в адресномрегистре или в ячейке местной памяти. При выборе команды формата полуслова необходимо в арифметическомблоке сделать операцию два-один раэ,формата слова - два раза, формататри полуслова - три раза. Это приводит к снижению быстродействия процессора, так как арифметический блокзанят подсчетом адреса и не можетзаниматься обработкой команды в товремя, когда командная информацияуже имеется в процессоре.Наиболее близким по техническойсущности к предлагаемому являетсямикропрограммный процессор (модель50 система 360 Фирмы .ЛВМ), который 2для адресации команд содержит блок выработки адреса команды. Этот блок состоит из 24-разрядного регистра адреса команды и 24-разрядного счетчика адреса команды, которые соединены между собой, а также с выходными шинами суммаТора, регистром адреса оперативной памяти и регистром данных оперативной памяти Г 2).Командная информация читается из оперативной памяти по словам (4-е байта) по адресу, определяемому регистром адреса команды, и затем, в счетчике происходит увеличение адреса на число байтов, содержащихся в текущей команде, методом прибавления двойки и (или) четверки к текущему значению счетчика. Затем, в начале следующего цикла обработки команды, происходит передача обновленного адреса из счетчика в регистр адреса оперативной памяти и в регистр адреса команды. Недостаток данной схемы заключается в том, что для подсчета адреса команды используется много оборудования (24-разрядный счетчик команди 24-разрядный регистр храненияадреса),Цель изобретения - сокращение оборудования.микропрограммного процессора путем исключения счетчикакоманд и регистра адреса команд безпотери быстродействия.Эта цель достигается тем, чтомикропрограммный процессор, содержатций регистр коммутации, первый адресный вход которого соединен с выходомблока местной памяти, информационныйвход является входом устройства,второй адресныйвход соединен с ныходом арифметического блока, а выходс первыми входами блока местной памяти, регистра команд,арифметичесКого блс.а и с выходом устройства, выходблока и с выходом устройства, выходрегистра команд соединен с первымвходом блока микропрограммного управления, выход которого соединенс управляющими входами регистра коммутации, регистра команд, арифметического блока и блока местной памяти, содержит блок формирования остатка, причем первый вход блокаформирования остатка соединен с выходом регистра коммутации, второйвход - с выходом регистра команд,а управляющий вход - с выходом блока микропрограммного управления, авыход - со вторыми входами блокамикропрограммного управления иарифметического блока.Причем блок формирования остатка.содержит регистр остатка, дешифратор,двухразрядный сумматор, группы элементов И, элементы И, ЙЛИ, причемвходы двух младших разрядов регистраостатка соединены с выходами первогои второго элемента ИЛИ соответственно, первые входы которых соединены свыходами элементов И первой и второйгрупп соотцетстненно, а вторые входы - с выходами элементов И третьейи четвертой групп соответственно,первые входы элементов И первой ивторой групп и вход установки нуля.старшего разряда регистра остаткасоединен с соответствующим выходомблока микропрограммного управления,вторые входы элементов И первой ивторой групп соединены с выходамисоответствующих разрядов регистракоммутации, йервые входы элементовИ третьей и четвертой групп соединены с первым входом элемента И ис .соответствующим выходом блокамикропрограммного управления, а вторыевходы-с первым и вторым выходами двухразрядного сумматора соот-.ветственно, выход переноса которогосоединен со вторым входом элементаИ, выход которого соединен со вхо дом устайовки единицы старшего разряда регистра остатка, первый и второй входы днухразрядного суммато- .ра соединены с единичными выходами двух младших разрядов регистра остатка соответственно, а третий нход - с выходом регистра команд, все выходы регистра остатка соединены с соответствующими входами дешифратора, выходы которого соедидинены со вторыми входами блокамикропрограммного управления и арифметического блока,На фиг. 1 изображена блок-схемамикропрограммного процессора," нафиг. 2 - функциональная схема блокаформирования остатка.Микропрограммный процессор состоит из блока 1 микропроГраммного уп 15равления, шин 2 входа из оперативнойпамяти, регистра 3 коммутации, регистра 4 команд, блока 5 местнойпамяти, блока б формирования остатка,шин 7 выдачи в оперативную память иарифметического блока 8.33 Выборка и отработка команд выполняется под управлением микропрограмм,которые хранятся и блоке 1 микропрограммного управления, который осуществляет адресацию, выборку микрокоманд5 и выдачу сигналов управления но нсеузлы процессора,Командная информация из оперативной памяти выбирается двойным словами (8 байтов) и по шинам 2 принимается на регистр 3 коммутации.Из регистра 3 коммутации очереднаякоманда помещается в регистр 4команды, а остаток командной информации - в фиксированные ячейки 5местной памяти.Код команды из регистра 4 команды поступает н блок 1 микропрограм-.много, управления и однозначно указывает начало микропрограммы текущей команды.40 Команды располагаются в оперативной памяти с границы полусМова.Выбранная командная информация может быть длиной в четыре, три, дваили одно полуслово, Если адресацияоперативнойпамяти выполняется сточностью до байта, то три последние разряда адреса указывают количество байтов выбранной команднойинформации, а два старших разрядаиз этих трех - количество полуслов.Очередная отрабатываемая командаможет быть длиной в одно, два илитри полуслова. Формат (длина) команды определяется соответствующими разрядами кода операции.В зависимости бт величины выбранной командной информации и формата текущей команды в блоке бформирования остатка устанавливается код, который определяетщ величину остатка.После выполнения текущей .команды и выхода на очередную, блок1 микропрограммного управления анализирует состояние, блока б формиу рования остатка, и если остаток ест60 то очередная команда или начало еечитается из блока 5 местной памяти ичерез регистр 3 коммутации помещается в регистр 4 команд,Если в остатке часть команды илиостаток нулевой, то происходит чтение командной информации иэ опера-тивной памятиАдрес командной информации хра-.нится в фиксированной ячейке блока 5местной памяти. При чтении командной информации адрес читается изблока 5 местной памяти и через регистр 3 коммутации по шинам 7 выдается в оперативную память, Параллельно он поступает в арифметическийблок 8, где увеличивается на величинудвойного слова и через регистр 3коммутации опять записывается вблок 5 местной памяти. Т. е. вовремя чтения командной информациипроисходит подготовка адреса для20следующего чтения.Таким образом, в процессе выполнения программь, в фиксированнойячейке 5 местной памяти хранитсяпродвинутый адрес, определяющий 25командную информацию с точностью додвойного слова, и командная информациявыбирается иэ оперативной памятидвойными словами.Для получения адреса следующей 30команды при выполнении некоторыхкоманд переходов и прерываний, продвинутый адрес корректируется на величину остатка,Коррекция выполняется в арифметическом блоке 8 и заключается ввычитании константы их текущего адреса командной информации. Константа определяет количество полусловкомандной информации, находящейся 4в остатке, и формируется в арифметическом блоке 8 по значениям потенциалов остатка, поступающим иэблока б формирования остатка.На фиг, 2 представлен блок бформирования остатка, который состоит из регистра 9 остатка, дешифратора 10, двухразрядного сумматора 11, первой группы элементов И 12,второй группы элементов И 13,элемента И 14, элементов ИЛИ 15.Величина остатка задается кодомтрехраэрядного регистра 9:000 - остаток длиной четыре полуслова (П 04);Х 01 - остаток длиной три полуслова (ПОЗ);Х 10 - остаток длиной дэа полуслова (П 02);Х 11 - ос т аток длиной одно полуслова (П 01);100 - остаток отсутствует (ПОО) .Х - разряд может приниматьлюбое значение.Формат команд определяется двумяразрядами кода операции:65 01 - команда длиной полуслова;10 - команда длиной слово;11 - команда длиной три полуслова.Во время начальной выборки командной информации (со пуску или выполнению, перехода) значение двух младших разрядов регистра 9 остатка устанавливается по управляющему сигналу 1 б, приходящему иэ блока 1 микропрограммного управления, и значению разрядов адреса команды, определяющих количество выбранных полуслбв, и поступающих из регистра 3 коммутации по шинам 17 и 18 через элементы 12 И 15 ИЛИ. Старший разряд регистра 9 остатка по сигналу 16 устанавливается в нуль.В дальнейшем при переходе на отработку очередной команды, регистр 9 остатка переключается по управляющему сигналу 19, поступающему из блока 1 микропрограммного управления. Переключение заключается в сложении предыдущего значения кода двух младших разрядов регистра 9 остатка с йвухразрядным кодом, определякщим формат команды и поступающим с регистра 4 команд, по шине 20 на двухразрядном сумматоре 11. Двухраэрядный код суммы через элементы 13 И и 15 ИЛИ заносится в два младших разряда регистра 9 остатка. Если в процессе сложения возникает перенос из старшего разряда, то через элемент 14 И старший разряд регистра 9 остатка устанавливается в единицу.Выходы регистра 9 остатка поступают на вход дешифратора 10, где происходит дешифрация кода в потенциалы, определяющие величину Ьстатка ПОО, П 01, П 02, ПОЗ и Н 04. Эти потенциалы поступают в блок 1 микропрограммного управления и арифметический блок 8.Размещение текущего адреса команды в ячейке местной памяти, счет адреса в пределах. двойных слов в арифметическом блоке и применение блока формирования остатка позволяет отказаться от использования счетчика команд и регистра адреса команд, что приводит к уменьшению оборудования процессора.Формула изобретения1, Микропрограммный процессор, содержащий регистр коммутации, первый адресный вход которого соединен с выходом блока местной памяти, информационный вход является входом устройства, второй адресный вход соединен с выходом арифметического блока, а выход - с первыми входами блока местной памяти, регистра команд, арифметического блока и свыходом устройства, выход регистра команд соединен с первым входом блока микропрограммного управления, вьжод которого соединен с управляющими входами регистра коммутации, регистра команд, арифметическбго блока и блока местной памяти, о тл и ч а ю щ и й с я тем, что, с целью сокращения оборудования, он содержит блок формирования остатка, причем первый вход блока формирования остатка соединен с выходом регистра коммутации, второй вход - с выходом регистра команд, а управляющий вход - с выходом блока микропрограммного управления, а выход - со вторыми входами блока микропрограммного управления и арифметического блока.2, Процессорпо п. 1, о т л ич а ю щ и й с я тем, что блок формирования остатка содержит регистр остатка, дешифратор, двухразрядный сумматор, группы элементов И, элемэнты И и ИЛИ, причем входыдвух младших разрядов регистра остатка соединены с выходами первого и второго элемента ИЛИ соответственно, первые входы которых соединены с выходами элементов И первой и второй групп собтветственно, а вторые входы - с выходами элементов И третьей и четвертой групп соответственно, первые входы элементов И первой и второй групп и вход установки нуля старшего разряда регистра остатка соединен с соответствующим выходомблока микропрограммного управления,вторые входы элементов И первый ивторой групп соединены с выходамисоответствующих разрядов регистракоммутации, первые входы элементов И третьей и четвертой группсоединены с первым входом элемента И и с соответствующимвыходом блока микропрограммногоуправления, а вторые входы - с первым и вторым выходами двухразрядного сумматора соответственно, выходпереноса которого соединен со вторым входом элемента И, выход которого соединен со входом установки5 единицы старшего разряда регистраостатка, первый и второй входыдвухразрядного сумматора соединеныс единичными выходами двух младшихразрядов регистра остатка соответ 20 ственно, а третий вход - с выходомрегистра команд, все выходы регистраостатка соединены с соответствующими входами дешифратора, выходы которого соединены со вторыми входами25 блока микропрограммного управленияи арифметического блока.Источники информации,принятые во внимание при экспертизе1, Дроздов Е. А. и др. Электрон"ные вычислительные машины единойсистемы.1976, с. 259 - 261, рис. 7.7.2. Хассон С. Микропрограммноеуправление. Мир, 1974, с. 162и. 8.6, рис. 8.1 8,6 (прототип)7445 В 7 актор лини Корректор И. Муска Зака Подписно 4/5 оставитель Г. Пономареве хред Ж. Кас теле в ич 3795/14 Тираж 751 ЦНИИПИ Государственного комитета СС по делам иэобретений и открытий 113035, Москва, Ж, Раушская наб., филиал ППП. Патент, г. Ужгород, ул. Проектная, 4 1 1

СмотретьЗаявка

2600631, 03.04.1978

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ЗАВОД ВЫЧИСЛИТЕЛЬНЫХ И УПРАВЛЯЮЩИХ МАШИН

АНОПРИЕНКО ВАЛЕНТИН ИОСИФОВИЧ, КАЛАШНИК АЛЕКСАНДР ГРИГОРЬЕВИЧ, СИРОТА НИКОЛАЙ АНТОНОВИЧ, ХАРИТОНОВ ВАСИЛИЙ НАУМОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 30.06.1980

Код ссылки

<a href="https://patents.su/5-744587-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для сбора и обработки информации

Следующий патент: Устройство для сопряжения основной и вспомогательной цифровых вычислительных машин

Случайный патент: Устройство для зачистки проката