Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 643874

Автор: Скляров

Текст

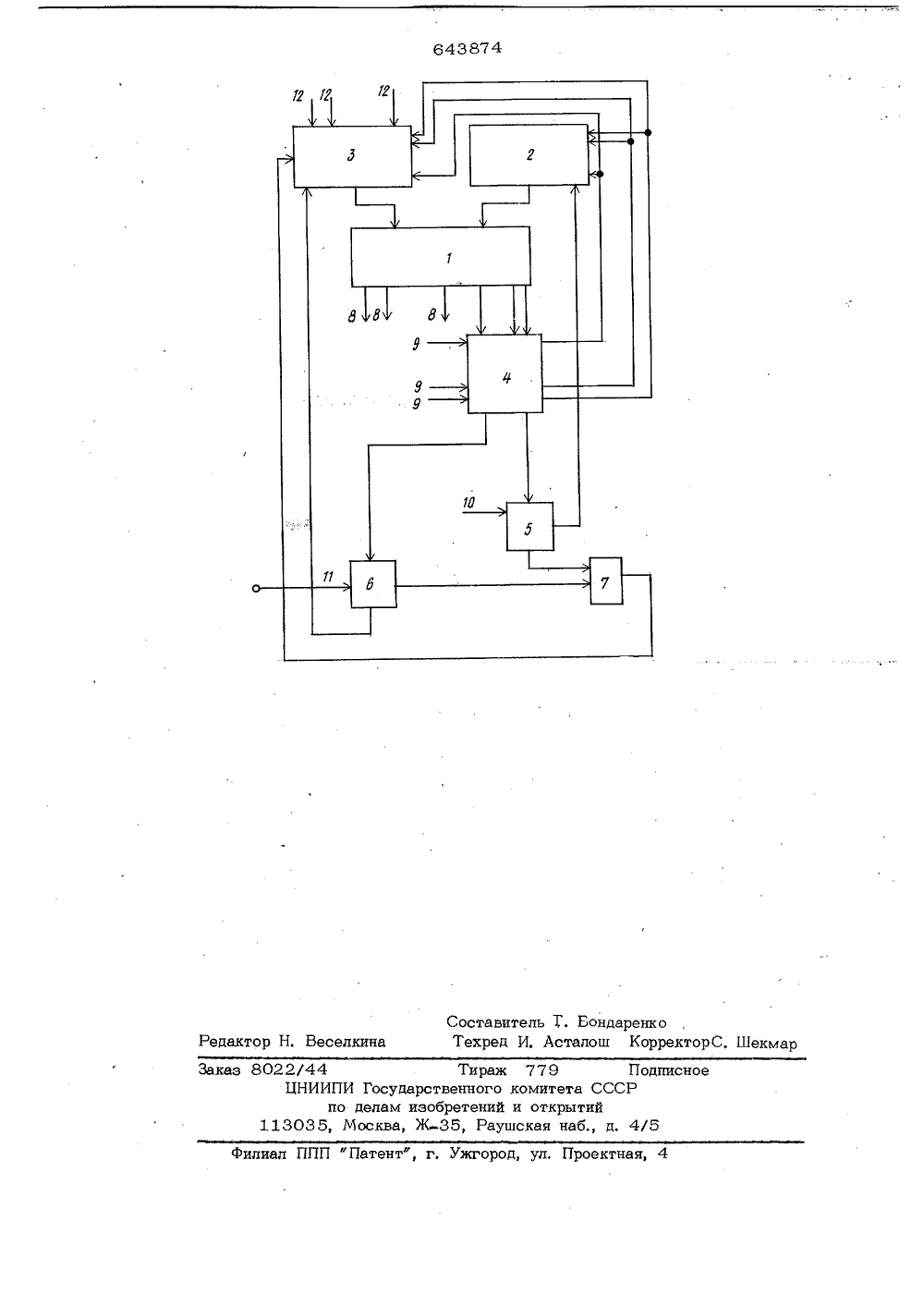

Союз Советских Социалистических Республик, Кл. 9/ Государственный коветет СССР ео делам изооретений и Открытий2) Автор изобретен ВСЕСОК И; 6 АТИ 5".- ЕХР 1;.ФК д Я ИГ ,МП. КА А. Скляров 1) Заяви(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИ ан тком данного устройства явограниченные функционапьнь ти вследствие того,что в нем пяются е возможно Изобретение относится к области вычислительной техники, может использоваться в качестве устройства управления в терминальной аппаратуре автоматизированных систем управления, а также в универсальных и специализированных цифровых вычислительных машинах.Известно микропрограммное устройство управления, содержащее блок памяти микропрограмм, первые выходы которого подключены к первой группе элементов И, а вторые выходы ко второй группе элементов И, связанной с формирователями управляющих сигналов и с первой и третьей группами апементов И, выходы третьей группы элементов И подключены ко входам регистра номера команды, выходы которого подключены к первому алементу третьей группы элементов И и ко входам первой группы алементов И, выходы которых подключены к регистру адреса, соединенному с блоком памяти микропрограмм 1 . Это устройство не позволяет орг изовать параппельное выполнение микропрограмм. При этом в режиме ожиданияоно не выполняет никаких полезных действий, что ограничивает его функционапь 5 ные возможности,Наиболее близким по техническойсущности к предлагаемому является устройство, содержащее блок памяти микропрограмм; блок проверки условий, регистры адреса, элемент И и триггеры,причем выход первого регистра адресасоединен с первым адресным входомблока памяти микропрограмм, группаадресных выходов которого подключенако входам первой группы блока проверки условий, первый управляющий выходкоторого подключен к единичному входу первого триггера, единичный выходкоторого подключен к первому входуэлемента И 2 .Недостаотсутствует возможность параллельного выполнения микропрограмм в режиме ожидания основной микропрограммы. При этом в режиме ожидания устройство не выполняет никаких полезных действий, Это снижает общее быстродействие цифровой аппаратуры, в состав которой входит микропрограммное устройство управления.Целью изобретения является расширение функциональных возможностей путем выполнения микропрограмм в режиме ожидания основной микропрограммы.Лля этого в предлагаемом устройстве второй управляющий выход блока проверки условий соединен с нулевым входом второго триггера, нулевой выход которого соединен с первым установочным входом второго регистра адреса, единичный выход второго триггера соединен со вторым входом элемента И, выход которого подключен ко второму установочному входу второго регистра адреса, выход которого подключен ко второму адресному входу блока памяти микропрограмм, группа информационных выходов блока проверки условий соединена с группой информационных входов первого регистра адреса и с первой группой информационных входов второго регистра адреса, вторая группа информационных входов которого соединена с группой информационных входов устройства, нулевой выход первого триггера соединен с установочным входом первого регистра адреса, вторая группа входов блока проверки условий соединена с группой управляющих входов устройстванулевой вход первого триггера соединен с первым управляющим входом устройства, единичный вход второго триггера соединен со вторым управляющим входом устройства, группа информационных выходов блока памяти микропрограмм соединена с группой информационных выходов устройства.г уУстройство (см. чертеж) содержит: блок 1 памяти микропрограмм, первый регистр 2 адреса, второй регистр 3 адреса, блок 4 проверки условий, первый триггер 5 второй триггер 6 элемент И 7, группу информационных выходов 8 устройства, группу управляющих входов 9 устройства, первый управляющий вход 10 устройства, второй управляющий вход 11 устройства, группу информационных входов 12 устройства. На выходы 8 передаются микрооперации в операционные схемы (например,ЭВМ). По входам 9 на микропрограммное устройство управления поступаютБ осведомительные сигналы (логическиеусловия) для формирования следующегоадреса ( при условии перехода) блока1 памяти микропрограмм, По входу 10поступает логическое условие, по котоО рому осуществляется выход из режимаожидания, По входам 11, 12 поступаютлогические условия соответственно дляустановки в единичное состояние второго триггера 6 и для записи адреса мик 1 Б рокоманды (в регистр 3 адреса) начинаяс которой может выполняться второстепенная микропрограмма (микроподпрограмма) в то время, когда основная микропрограмма находится в режиме ожида 20 ния. Единичное состояние триггера 6говорит о том, что в регистре 3 адресазаписан начальный адрес микропрограммы, Выходы регистров 2 и 3 адресасоединены соответственно с первым и25 вторым входами блока 1 памяти микропрограмм. Группа информационных выходов блока 4 проверки условий соединенас группой информационных входов первого регистра адреса и с первой группой30 информационных входов второго регистра адреса,По этим входам осуществляется запись адреса очередной микрокоманды врегистры 2 и 3 адреса. Установочный35 вход регистра 2 адреса соединен с нулевым выходом триггера 5, а второйустановочный вход регистра 3 адресас выходом элемента И 7. По этим входам осуществляется разрешение или40 запрет записи адреса в регистры 2 и 3адреса.Группа адресных выходов блока 1 памяти микропрограмм соединена со входами блока 4 проверки условий, один45 управляющий выход которого соединенсо входом установки в нуль триггера6, а другой управляющий выход - совходом установки в единицу триггера 5.Сброс триггера 5 осуществляется сигналом по входу 10, Единичные выходытриггеров 5 и 6 соединены со входамиэлемента И 7, Нулевой выход триггера6 соединен с установочным входом регистра 3 адреса и является разрешаю 55щим сигналом для записи информации повходам 12.Блок 1 памяти микропрограмм предназначен для хранения микрокоманд всехгровой информации, которая может производиться как в процессе выполненияосновной микропрограммы, так и в моменты ожидания. Такая обработка циф 10 ровой информации производится по однойили нескольким микроподпрограммам,микрокоманды которых хранятся в блоке1 памяти микропрограмм. Во время выполнения основной микропрограммы при15 возможности параллельных процессовпо специальным. логическим условиям повходам 12 осуществляется запись адреса начальной микрокоманды соответствующей микроподпрограммы в регистр 3адреса. После записи адреса по входу11 производится установка триггера 6в единичное состояние, которое говорито том, что в регистре 3 адреса находится начальный адрес микроподпрограммы,Таким образом, в режиме ожидания единичный сигнал с выходов триггеров 5и 6 через элемент И 7 поступает навход регистра 3 адреса и разрешаетприем информации с выхода блока 4 ивыдачу информации с него на блок 1 памяти микропрограмм (запись информации в регистр 3 адреса по входам 12запрещается сигналом с нулевого выхода триггера 6), Поэтому второй и послеЗ 5 дующие адреса формируются так жекаки в основной микропрограмме, по информационным входам с помощью блока 4проверки условий, Следует отметить чтов регистре 2 адреса хранится адресдомикрокоманды, с которой необходимопродолжать основную микропрограммупри выходе из режима ожидания,Выполнение микроподпрограммы продолжается либо до конца (при дли 45 тельном ожидании), либо до того момента времени, когда по входу 10 поступитсигнал, извещающий об окончании режима ожидания и о продолжении основноймикропрограммы.50При этом триггер 5 устанавливается в нулевое состояние, происходит прерывание выполнения микроподпрограммыи продолжение выполнения основной микропрограммы. При наличии следующего55режима ожидания выполнение микроподпрограммы начинается с прерванного адреса, который хранится в регистре 3 адреса. В случае окончания выполнения 3 6438микропрограмм (микроподпрограмм) работы устройства.Регистр 2 адреса предназначен дляприема адреса очередной микрокомандыи формирования сигналов чтения микрокоманды по принятому адресу в режимеосновной работы.Регистр 3 адреса выполняет функциирегистра 2 адреса в режиме ожиданияосновной микропрограммы и обеспечивает выбор микрокоманд, входящих водну из микроподпрограмм.Триггер 5 предназначен для коммутации регистров 2 и 3 адреса. Единичное состояние этого триггера говорито режиме ожидания основной микропрограммы. При этом с единичного выходатриггера 5 снимается сигнал, который(в случае наличия сигнала на единичномвыходе триггера 6) разрешает чтениеинформации из регистра 3 адреса изапись информации в него из блока 4.В это время сигнал с нулевого выходатриггера 5 запрещает чтение информации из регистра 2 адреса и запись ееиз блока 4. В основном режиме (приотсутствии ожидания) триггер 5 разрешает прием информации на регистр 2адреса и запрещает прием информациина регистр 3 адреса,Соответствующие выходы регистров,2 и 3 адреса объединены на входахблока 1 памяти микропрограмм на элементах ИЛИ,Принцип работы устройства заключается в следующем. При отсутствии ожидания на выходах блока 1 памяти микропрограмм с помощью синхронизирующихсигналов (на чертеже не показаны)производится последовательное формирование микрокоманд. Причем операционная часть каждой микрокоманды поступает по выходам 8 в операционные узлы (например, ЭВМ), а адресная частьна блок 4 проверки условий, на который по входам 9 поступают также осведомительные сигналы. По результатамсравнения адресной части и осведомительных сигналов формируется адресследующей микрокоманды, который записывается в регистр 2 адреса. В случае, если в адресной части содержится признак ожидания (реализация ждущей вершины в графе микропрограммы),на одном управляющем выходе блокапроверки условий формируется сигнал,по которому производится установкатриггера 5 в единичное состояние,74 бПри этом осуществляется запрет на формирование адреса регистром 2 адреса. В процессе выполнения основной микропрограммы возникает необходимость в параллельной обработке различной цифмикроподпрограммы триггер 6 сигналом,поступаюшим из блока 4 проверки условий, устанавливается в нулевое состояние. При этом на нулевом выходе триггера 6 появляется разрешаюшйй сигналдля приема начального адреса по входам12 следунхцейпараллельной мйкроподп рограммы,При наличии режима ожидания в случае, если триггер 6 находится в нулевомсостоянии, никаких действий дб йрйхода сигнала по шине 10 не производится.Таким образом, предложенное устройство, как и прототип; имеет простуюсхему и реализует режим ожидания, Однако в отличие от прототипа оно позволяет формировать параллельные процессы и в режиме ожидания выполняетполезные действия. Это увеличивает обшее быстродействие цифровой аппаратуры, в состав которой входит микропрограммное устройство управления, и расширяет его функциональные возможности.Предложенное микропрограммное устройство управления может использоваться в качестве устройства управлениясамого различного назначения. Особенноперспективно его применение в терминальной аппаратуре автоматизированныхсистем управления, при этом возможна, например, параллельная работа повводу-выводу информации и ее обработке.Ф ормула изобретенияМикропрограммное устройство управления, содержащее блок памяти микропрограмм, блок проверки условий;" регистры адреса, элемент И и триггеры, причем. выход первого регистра адреса соединен с первым адресным входом блока памяти микропрограмм, группа адресных выходов которого подключена ко входам первой группы блока проверки условий, первый управляюший выход которого подключен к единичному входупервого триггера, единичный выход которого подключен к первому входу элемента И, о т л и ч а ю ш е е с я тем,что, с целью расширения функциональных возможностей за счет выполнениямикропрограмм в режиме ожидания основной микропрограммы, второй управляюший выход блока проверки условий О соединен с нулевым входом второготриггера, нулевой выход которого соединен с первым установочным входом второго регистра адреса, единичный выходвторого триггера соединен со вторым 5 входом элемента И, выход которого подключен ко второму установочному входувторого регистра адреса, выход которого подключен ко второму адресному входу блока памяти микропрограмм, группа 20 информационных выходов блока проверкиусловий соединена с группой информационных входов первого регистра адреса и с первой группой информационныхвходов второго регистра адреса, втораягруппа информационных входов которогосоединена с группой информационных входов устройства, нулевой выход первоготриггера соединен с установочным входом первого регистра адреса, втораягруппа входов блока проверки условийсоединена с группой управляюших входовустройства, нулевой вход первого триггера соединен с первым управляющимвходом устройства, единичный вход второго триггера соединен со вторым управляющим входом устройства, группа информационных выходов блока памятимикропрограмм соединена с группой информационных выходов устройства. оИсточники информации, принятые вовнимание при экспертизе1, Авторское свидетельство СССР423127, кл. Я 06 Р 9/16, 1971452. Авторское свидетельство СССР437072, кл. Я 06 Р 9/12, 1972.Тираж 779сударственного комитета СССам изобретений и открытийква, Ж, Раушская наб., д.

СмотретьЗаявка

2392273, 01.08.1976

ПРЕДПРИЯТИЕ ПЯ А-3327

СКЛЯРОВ ВАЛЕРИЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммное

Опубликовано: 25.01.1979

Код ссылки

<a href="https://patents.su/5-643874-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для защиты памяти

Следующий патент: Устройство для контроля последовательсности импульсов

Случайный патент: Способ лечения гипертонической болезни