Микропрограммное устройство управления с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

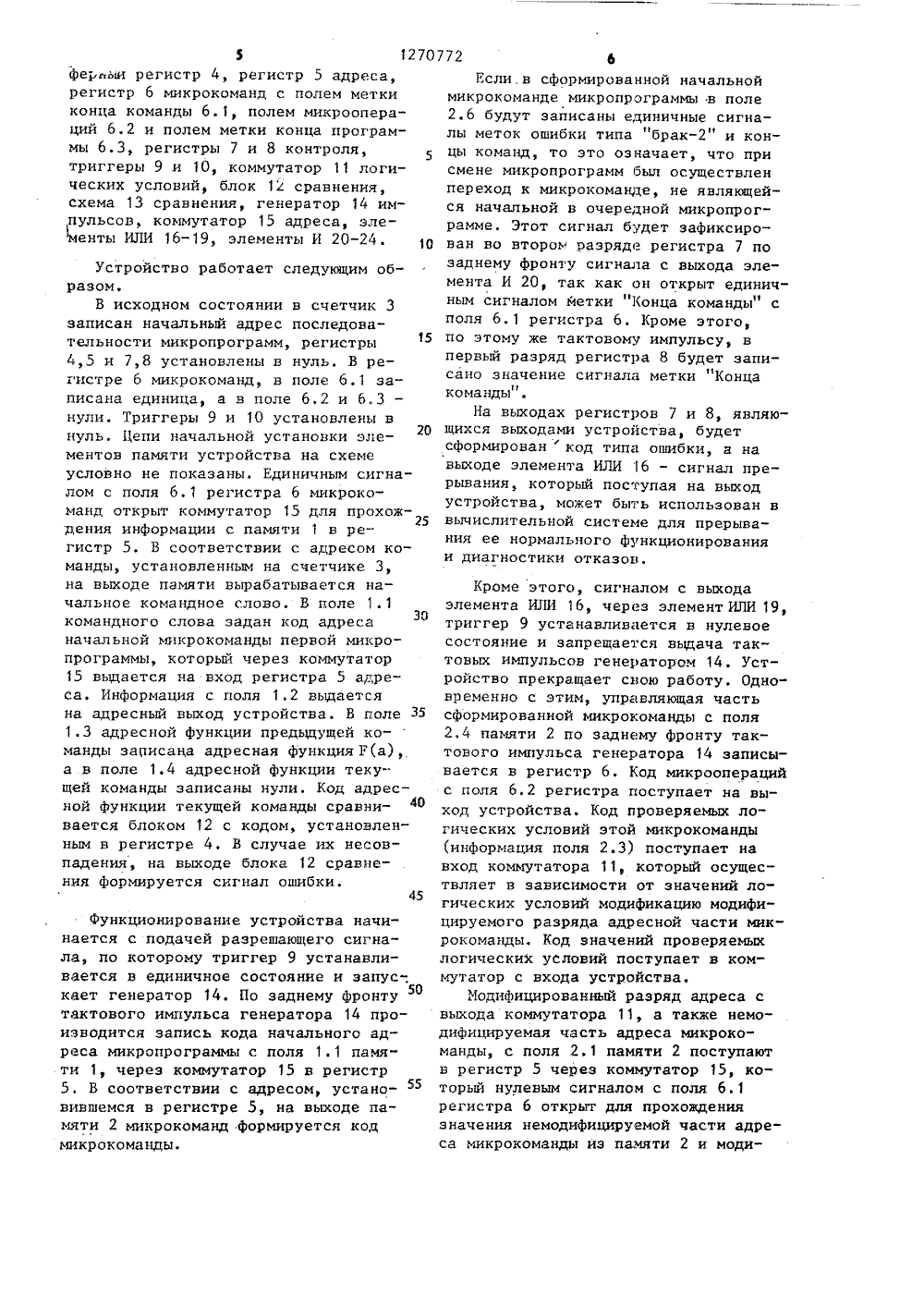

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 06 Р ТВЕННЫЙ НОМИТЕТ СССРм изОБРетений и ОтнРытий ГОС ПО ОБРЕТЕНИ ЕЛЬСТ(57) Изобретенлительной технпостроения микуправления. Цется повышениустройства, Иконтроль правмы путем контпредыдущей иИзобретение тна начальныекоманд за счеошибок. 1 ил. Н 42Кривоносов,качев, М.П.ТкаВ.С.Харченко ельство ССС 22, 1981. ство СССР 9/22, 1985УСТРОЙСТВО ОПИСАНИЕ АВТОРСКОМУ( СВИ(54) МИКРОПРОГРАММНОЕУПРАВЛЕНИЯ С КОНТРОЛЕМ ие относится к вычисике и используется для ропрограммныхустройств елью изобретения являдостоверности работы обретение осуществляет ильности хода програмоля адресных функций оследующей команд, кже осуществляет вь 1 ход икрокоманды при смене установления меток5 1 О 15 2 О ЗО Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих устройств ЭВМ и вычисли: - тельных систем с микропрограммным управлением.Известно микропрограммное устройство, содержащее две памяти, генератор импульсов, триггеры, регистры, счетчик адреса, коммутатор, элементы ИЛИ.Недостатком известного устройства является большой объем контрольного оборудования, который существенно усложняет устройство и снижает его надежность. Недостатком также является низкая достоверность функционирования, которая обусловлена тем, что в устройстве отсутствуют специальные технические средства, которые контролируют правильность функционирования в таких фазах, как выборка адресной информации, переход к управляющему каналу, выборка управляющей информации и переход к адресному каналу, Все это в конечном итоге снижает достоверность функционирования устройства.Кроме того, для повышения достоверности не используется естественная структурная избыточность присущая микропрограммным устройствам со стандартными блоками памяти, Так например, свободные зоны постоянного запоминающего устройства могут быть заполнены специальной контрольной информацией для сигнализации об ошибках. Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является микропрограммное устройство управления с .,контролем, содержащее счетчик команд, выход которого через память команд соединен с входами коммутатора адреса, блока сравнения и буферного регистра, выход которого через соединенные последовательно блок сравнения и первый регистр контроля. соединен с входом первого элемента ИЛИ, выход коммутатора адреса через соединенные последовательно регистр адреса и память микрокоманд соединен .с входами коммутатора адреса, комму" татора логических условий, регистра микрокоманд и первого регистра контроля, генератор импульсов, первый выход которого соединен с входами 35 4 О 45 50 55 регистра микрокоманд и через первый элемент И - с входом буферного регистра, второй выход генератора импульсов соединен с входом регистра адреса, второй элемент ИЛИ.В известном устройстве реализован принцип двухуровневого микропрограммного управления,В одном блоке памяти хранятся коды команд, в другом - микрокоманды. Работа командного и микрокомандного каналов осуществляется попеременно.Недостатком устройства является низкая достоверность его функционирования, обусловленная отсутствием средств контроля последовательности смены команд (микропрограмм) при наличии в программе команд ветвления (команд условного перехода), отсутствием средств контроля правильности попадания на начальные микрокомандымикропрограмм при смене команд. Целью изобретения является повышение достоверности работы устройства.Поставленная цель достигается тем,что в микропрограммное устройствоуправления с контролем, содержащее счетчик команд, выход которого через память команд соединен с входамикоммутатора адреса, блока сравненияи буферного регистра, выход которогочерез соединенные последовательноблок сравнения и первый регистр контроля соединен с входом первого элемента ИЛИ, выход коммутатора адресачерез соединенные последовательнорегистр адреса и память микрокомандсоединен с входами коммутатора адре-.са, коммутатора логических условий,регистра микрокоманд и первого регистра контроля, генератор импульсов,первый выход которого соединен свходами регистра микрокоманд и черезпервый элемент И с входом буферногорегистра, второй выход генератораимпульсов соединен с входом регистраадреса, второй элемент ИЛИ, введенысхема сравнения, два триггера, второй регистр контроля, два элементаИЛИ, четыре элемента И, причем первый выход генератора импульсов соединен с входами второго, третьегои четвертого элемента И и второгорегистра контроля, выходы памятимикрокоманд соединены с входами коммутатора логических условий, второго и третьего элементов ИЛИ, третье 12707721 О 15 20 25 го, четвертого и пятого элементов Ии первого и второго регистров контроля, выходы регистра микрокомандСоединены с входами четвертого элемента ИЛИ и коммутатора адреса, первого элемента И, третьего элементаИЛИ и второго регистра контроля, выход которого через соединенные последовательно первый и четвертый элементы И и первый триггер соединен свходом генератора импульсов, выходкоммутатора логических условий соединен с входами коммутатора адреса ипятого элемента И, выходы второго итретьего элементов ИЛИ через соответственно пятый и второй элементы Исоединены с входами второго триггера,выходы которого и памяти команд через схему сравнения соединены с входом блока сравнения, выходы третьегои четвертого элементов И соединены свходами счетчика команд, выход пер-.вого элемента И соединен с входомпервого регистра контроля. Сущность изобретения состоит в повышении достоверности функционирования микропрограммного устройства управления на основе повышения достоверности контроля последовательности смены команд (микропрограмм) в программе.Повышение достоверности функционирования устройства осуществляется путем организации контроля правильности последовательности смены ко манд при наличии в программе команд условного перехода, Для контроля правильности хода программы на линейных ее участках, при безусловных, а также условныхпереходах предлагает О ся использовать принцип контроля адресных функций Р(а) и Г(а), расположенныхв контрольном поле командного слова блока памяти команд и связывающих две следующие друг за другом 45 команды, При этом адресная функция предыдущей команды запоминается в буферном регистре и сравнивается с адресной функцией текущей команды, схемой сравнения. Факт их несравнения свидетельствует о наличии ошибки.В случае условного перехода производится модификация адресной функции текущей команды в соответствии со значением проверяемого логического условия. Причем адресные функции команд, переход к которым возможен в результате проверки логического условия, должны отличаться в одном разряде.В результате модификации модифицируемого разряда адресной функциитекущей команды, значением логического условия ее код становится равным значению кода адресной функциипредыдущей команды. В зависимостиот разрядности адресных функций может быть обеспечен требуемый уровеньдостоверности контроля порядка следования команд.При увеличении разрядности адресных функций сужается множество команд, имеющих их одинаковое значение, что приводит к увеличению, вероятности обнаружения нарушения последовательности смены команд.Повышение достоверности устройства достигается повышением контроляправильности смены команд путем организации контроля выхода на начальныемикрокоманды микропрограмм при сменекоманд. С этой целью в микрокомандное слово вводится микрооперация(метка) ошибки, которая записываетсяво всех ячейках блока памяти микрокоманд, кроме ячеек с начальными микрокомандами всех микропрограмм,Таким образом, если при сменемикропрограмм первой будет считанамикрокоманда, не являющаяся начальной, то единичный сигнал метки ошибки будет зафиксирован, как сигналОшибки,Повышение вероятности формирования и выдачи ошибки достигается засчет записи в неиспользуемые ячейкипамяти двух меток ошибок, Повышениеглубины диагностирования также достигается за счет увеличения множествафиксируемых ошибок, т.е. увеличенияколичества информации о состоянииустройства.На чертеже изображена функциональная схема предлагаемого устройства.Устройство содержит память 1 команд с полями кодов команд (микропрограмм) 1.1, адреса 1.2, адреснойфункции предыдущей команды 1.3, адресной функции текущей команды 1.4,память 2 микрокоманд с полями немодифицируемой части адреса 2.1, модифицируемого разряда адреса 2.2, кодапроверяемых логических условий 2.3,микроопераций 2.4, метки ошибки типа"брак" 2.5, метки ошибки типа12707 2 3фер,ьы регистр 4, регистр 5 адреса, регистр 6 микрокоманд с полем метки конца команды 6.1, полем микроопераций 6.2 и полем метки конца программы 6.3, регистры 7 и 8 контроля, триггеры 9 и 10, коммутатор 11 логических условий, блок 12 сравнения, схема 13 сравнения, генератор 14 импульсов, коммутатор 15 адреса, элементы ИЛИ 16-19, элементы И 20-24,Устройство работает следующим образом.В исходном состоянии в счетчик 3записан начальный адрес последовательности микропрограмм, регистры4,5 и 7,8 установлены в нуль. В регистре 6 микрокоманд, в поле 6.1 записана единица, а в поле 6,2 и 63нули. Триггеры 9 и 10 установлены внуль, Цепи начальной установки эле 2 Оментов памяти устройства на схемеусловно не показаны. Единичным сигналом с поля 6,1 регистра 6 микрокоманд открыт коммутатор 15 для прохож 25дения информации с памяти 1 в регистр 5. В соответствии с адресом команды, установленным на счетчике 3,на выходе памяти вырабатывается начальное командное слово. В поле 1.1командного слова задан код адресаЗОначальной микрокоманды первой микропрограммы, который через коммутатор15 вьдается на вход регистра 5 адреса. Информация с поля 1,2 вьдаетсяна адресный выход устройства. В поле З 51.3 адресной функции предьдущей команды эаписаца адресная функция Е(а),а в поле 1,4 адресной Функции текущей команды записаны нули. Код адресной функции текущей команды сравнивается блоком 12 с кодом, установленным в регистре 4, В случае их несовпадения, на выходе блока 12 сравнения формируется сигнал ошибки,Функционирование устройства начинается с подачей разрешающего сигнала, по которому триггер 9 устанавливается в единичное состояние и запус". кает генератор 14. По заднему фронту50 тактового импульса генератора 14 производится запись кода начального адреса микропрограммы с поля 1.1 памя" ти 1, через коммутатор 15 в регистр 5, В соответствии с адресом, устано вившемся в регистре 5, на выходе памяти 2 микрокоманд формируется код микрокоманды. Если.в сформированной начальной микрокоманде микропрограммы в поле 2.6 будут записаны единичные сигналы меток ошибки типа "брак" и концы команд, то это означает, что при смене микропрограмм был осуществлен переход к микрокоманде, не являющейся начальной в очередной микропрограмме. Этот сигнал будет зафиксирован во втором разряде регистра 7 по заднему фронту сигнала с выхода элемента И 20, так как он открыт единичным сигналом метки "Конца команды" с поля 6. 1 регистра 6. Кроме этого, по этому же тактовому импульсу, в первый разряд регистра 8 будет записано значение сигнала метки "Конца команды".На выходах регистров 7 и 8, являющихся выходами устройства, будет сформированкод типа ошибки, а на выходе элемента ИЛИ 16 - сигнал прерывания, который поступая на выход устройства, может быть использован в вычислительной системе для прерывания ее нормального функционирования и диагностики отказов. Кроме этого, сигналом с выходаэлемента ИЛИ 16, через элемент ИЛИ 19,триггер 9 устанавливается в нулевоесостояние и запрещается вьдача тактовых импульсов генератором 14. Устройство прекращает свою работу. Одно"временно с этим, управляющая частьсформированной микрокоманды с поля2.4 памяти 2 по заднему фронту тактового импульса генератора 14 записывается в регистр 6, Код микрооперацийс поля 6.2 регистра поступает на выход устройства. Код проверяемых логических условий этой микрокоманды(информация поля 2.3) поступает навход коммутатора 11, который осуществляет в зависимости от значений логических условий модификацию модифицируемого разряда адресной части микрокоманды, Код значений проверяемыхлогических условий поступает в коммутатор с входа устройства,Модифицированный разряд адреса свыхода коммутатора 11, а также немодифицируемая часть адреса микрокоманды, с поля 2.1 памяти 2 поступаютв регистр 5 через коммутатор 15, который нулевым сигналом с поля 6.1регистра 6 открыт для прохождениязначения немодифицируемой части адреса микрокоманды из памяти 2 и моди 7 1270 фицированного разряда с выхода коммутатора 11 - на вход регистра 5. Этим же сигналом запрещается поступление информации в регистр 5 с выхода памяти 1.5Если ошибок в функционировании устройства не обнаружено, то по заднему фронту очередного тактового импульса генератора 14 в регистр 5 будет записан адрес очередной микроко манды. По заднему фронту очередного тактового импульса генератора 14 будет осуществлена запись информации в регистр 8 и регистр 6 аналогично описанному. 15Если в процессе реализации микропрограммы в поле 2,5 сформированной микрокоманды, не являющейся конечной, будет записан единичный сигнал метки ошибки типа "Брак", то это означа ет, что в результате сбоя или отказа оборудования нарушена последовательность переходов в пределах микропрограммы, т,е. при смене микрокоманд осуществлен несанкционированный 25 переход к неиспользуемой ячейке памяти 2.факт нарушения последовательности смены микрокоманд в микропрограмме фиксируется в первом разряде регистра 8 по заднему фронту очередного тактового импульса генератора 14. На выходе устройства выдается код ошибки и сигнал прерывания.Условный переход в программе организуется с использованием команд условного перехода.В микрокоманде проверки логического условия соответствующей микропрограммы условного перехода в поле 2.3 задается код проверяемого логического условия, в поле 2.4 микроопераций - микрооперация условного перехода. В соответствии с кодом проверяемых логических условий, элементом ИЛИ 17 формируется единичный сигнал, который поступает на вход элемента И 24. Этим самым при наличии разрешающего сигнала микрооперации условного перехода элемент И 24 открывается для поступления сигнала с выхода коммутатора 11 и на вход триггера 10. Процесс модификации значений модифицируемого разряда адресной микрокоманды коммутатором 11 логических условий описан выше. По заднему фронту тактового импульса, поступающему через элемент И 21 от генерато 772 8ра 14 на триггер 10, он будет установлен в состояние, соответствующее значению сигнала на выходе элемента И 24. Элемент И 21 открыт при этом через элемент ИЛИ 18 единичным сигналом микрооперации условного перехода с памяти 2.Сигналом с выхода триггера 1 О, поступающим на схему 13 сравнения, осуществляется модификация значения одного разряда адресной функции текущей команды, поступающего с поля 1.4 памяти 1.В связи с тем, что адресные функции микрокоманд, переход к которым возможен в результате заполнения команды условного перехода, отличаются друг от друга на единицу, то в результате модификации адресной функции текущей команды на выходе блока 12 будет нулевой сигнал как при выполнении перехода, так и в том случае, когда переход не осуществлен из-за отсутствия соответствующего условия.Если в процессе выполнения программы, в результате сравнения адресных функций предыдущей и текущей команд, на выходе блока 12 появится единичный сигнал, то это значит, что нарушена последовательность исполнения команд в программе, т.е, последовательность смены микропрограмм. Факт нарушения последовательности смены микропрограмм будет зафиксирован при смене микропрограмм в третьем разряде регистра 7 по заднему фронту управляющего сигнала с выхода элемента И 20, формирование кода адреса очередной команды в случае ус-ловного перехода на уровне команд при выполнении проверяемого логического условия осуществляется следующим образом.Единичйым сигналом микрооперации записи микрокоманды проверки логических условий, поступающим с выхода памяти 2 микрокоманд в очередной микрокоманде будет разрешено прохождение через элемент И 23 тактового импульса генератора 14 на вход синхронизации счетчика 3. По заднему фронту управляющего сигнала с выхода элемента И 23 в счетчик 3 будет записан код адреса с входа устройства. В соответствии с этим адресом на выходе памяти 1 будет сформировано командное слово.Если условие выполнения переходав команде условного перехода отсутствовало, то адрес очередной командывырабатывается естественным продвижением содержимого счетчика 3, длячего вырабатывается микрооперация естественной адресации на выходе полн2.4 памяти 2.Формирование кода адреса очередной микрокоманды при безусловном 10переходе в программе организуетсяаналогично случаю условного перехода,когда условие перехода выполняется.При естественной адресации командединичным сигналом микрооперации естественной адресации с выхода памяти2 разрешается прохождение через элемент И 22 тактового импульса генератора 14, По заднему фронту управляющего сигнала с выхода элемента И 22код, установленный в счетчике 3, будет увеличен на единицу, т.е. будетсформирован адрес очередной команды.При записи в регистр 6 микрокоманды,являющейся конечной в микропрограмме, единичным сигналом метки Конецкоманды" с поля 6.1 коммутатор 15закрывается для прохождения в регистр 5 кода адреса очередной микрокоманды с выхода памяти 2 и разрешается поступление кода начальной микрокоманды очередной микропрограммыс поля 1.1 памяти 1.По заднему фронту очередного тактового импульса генератора 14 кодадреса начальной микрокоманды очередной микропрограммы будет записан врегистр 5. На выходах памяти 2 будетсформирован код микрокоманды. По заднему Фронту очередного тактового импульса генератора 14 аналогично ранее описанному, будет осуществленазапись информации в регистр 6 и врегистр 8, при этом в его второмразряде будет зафиксирован единичныйсигнал метки конца команды,Кроме этого, единичным сигналом с поля 6. 1 метки конца команды регистра 6 будет разрешено прохождение через элементы И 20 и 21 тактового импульса генератора 14,По заднему фронту управляющего сигнала с выхода элемента И 20 будет осуществлена запись кода с выхода поля 1.3 адресной функции предыдущей 55 команды памяти 1 в регистр 4, а также запись информации об обнаруженных ошибках с выхода блока 12 и выходов полей 2,5 и 2.6 меток ошибок памяти2 в регистр 7. По заднему фронту управляющего сигнала с выхода элементаИ 21, триггер 10 будет установлен всостояние, соответствующее значениювыходного сигнала элемента И 24,т.е. в нулевое состояние,Модификация адресной функции текущей команды при организации безусловного перехода, а также при естественной адресации команд не производится.В микрокоманде, являющейся конечной в микропрограмме, в полях 2,1 и2.2 задается адрес перехода к неиспользуемой ячейке памяти, содержащейметки ошибки типа "брак", и "брак" .Поэтому, если по единичному сигналуметки конца команды в регистр 5 микрокоманд будет записан адрес с поля2.1 памяти 2 и выхода коммутатора 11,а не код начального адреса очередной микропрограммы с поля 1.1 памяти 1, то в полях 2,5 и 2.6, сформированной в соответствии с этим адресом микрокоманды, будут записаныметки ошибок типа "брак, "брак".Это свидетельствует о неправильнойсмене микропрограмм (команд). Фактнарушения правильности формированиякодов микропрограмм, т,е. правильности формирования адресов начальныхмикрокоманд микропрограмм фиксируется в первом и втором разрядах регистра 7 по заднему фронту управляющего сигнала с выхода элемента И 20,Одновременно с этим по заднему фронтутактового импульса генератора 14 впервый и второй разряды регистра 8будут записаны единичные сигналы метки ошибки типа "брак", и конца команды соответственно,На выходах типа ошибки аналогично описанному формируется код типаошибки, на соответствующем выходеустройства формируется сигнал прерывания, устройство прекращает работу.При считывании конечной микрокоманды, конечной микропрограммы единичным сигналом метки "Конца програм.мы" с поля 6,3 регистра 6 будет установлен в нулевое состояние триггер 9. По нулевому сигналу с его единичного выхода, генератор 14 прекращает генерацию тактовых импульсов,Таким образом, предлагаемое устройство обеспечивает выполнение мик 11 12 ропрограмм, записанных в памяти 2 микрокоманд, в последовательности, заданной в памяти 1 команд.В предположении, что в устройстве может одновременно отказать не более одного функционального элемента и контрольное оборудование абсолютно надежно можем получить:для известного устройства множество подозреваемых в отказе функциональных элементов может уменьшаться до подмножества функциональных элементов командного уровня или подмножества функциональных элементов микрокомандного уровня; для предлагаемого устройства множество подозреваемых в отказе функциональных элементов может уменьшаться до группы функциональных элементов командного или микрокомандного уровня. Например, по коду типа ошибки 11101 можно сделать вывод об отказе блока памяти микрокоманд.Таким образом, технические преи-мущества предлагаемого устройства по сравнению с известным заключаются в более высокой достоверности функционирования, которое обеспечивается введением дополнительных встроенных средств контроля.формула изобретенияМикропрограммное устройство управления с контролем, содержащее счетчик команд, выход которого через память команд соединен с входами коммутатора адреса, блока сравнения и буферного регистра, выход которого через соединенные последовательно блок сравнения и первый регистр контроля соединен с входом первого элемента ИЛИ, выход коммутатора адреса через соединенные последовательно регистр адреса и память микрокоманд . соединен с входами коммутатора адре 70772 12 са, коммутатора логических условий, регистра микрокоманд и первого регистра контроля, генератор импульсов, первый выход которого соединенс входами регистра микрокоманд и через первый элемент И с входом буфер 10 15 20 25 30 3540 45 ного регистра, второй выход генератора импульсов соединен с входом регистра адреса, второй элемент ИЛИ, о т л и ч а ю щ е е с я тем, что,целью повышения достоверности ра 5 оты устройства, в него введены схема сравнения, два триггера, второй регистр контроля, два элемента ИЛИ, четыре элемента И, причем первый выход генератора импульсов соединен с входами второго, третьего и четвертого элементов И и второго регистра контроля, выходы памяти микро- команд соединены с входами коммутатсра логических условий, второго и третьего элементов ИЛИ, третьего, четвертого и пятого элементов И и первого и второго регистров контроля, выходы регистра микрокоманд соединены с входами четвертого элемента ИЛИ и коммутатора адреса, первого элемента И, третьего элемента ИЛИ и второго регистра контроля, выход которого через соединенные последовательно первый и четвертый элементы ИЛИ и первый триггер соединен с входом генератора импульсов, выход коммутатора логических условий соединен с входами коммутатора адреса и пятого элемента И, выходы второго и третьего элементов ИЛИ через соответственно пятый и второй элементы И соединены с входами второго триггера, выходы которого и памяти команд через схему сравнения соединены с входом блока сравнения, выходы третьего и четвертого элементов И соединены с входами счетчика команд, выход первого элемента И соединен с входом первого регистра контроля,1270772 оставитель В.Супрунехред Л.Сердюкова Корректор В,Синицкая Редактор Ю.Серед аказ 6244/51 Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная Тираж 671 НИИПИ Государственног по делам изобретении 13035, Москва, И, Подписноекомитета СССРи открытийаушская наб., д. 4/

СмотретьЗаявка

3671844, 13.12.1983

ПРЕДПРИЯТИЕ ПЯ А-7160

СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, КРИВОНОСОВ АНАТОЛИЙ ИВАНОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕВ АЛЕКСАНДР ПАВЛОВИЧ, ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 11/26, G06F 9/22

Метки: контролем, микропрограммное

Опубликовано: 15.11.1986

Код ссылки

<a href="https://patents.su/8-1270772-mikroprogrammnoe-ustrojjstvo-upravleniya-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления с контролем</a>

Предыдущий патент: Генератор случайных последовательностей

Следующий патент: Сигнатурный анализатор

Случайный патент: Устройство для ввода информации