Устройство для вычисления дискретного преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1645967

Авторы: Каневский, Коноплицкий, Корчев

Текст

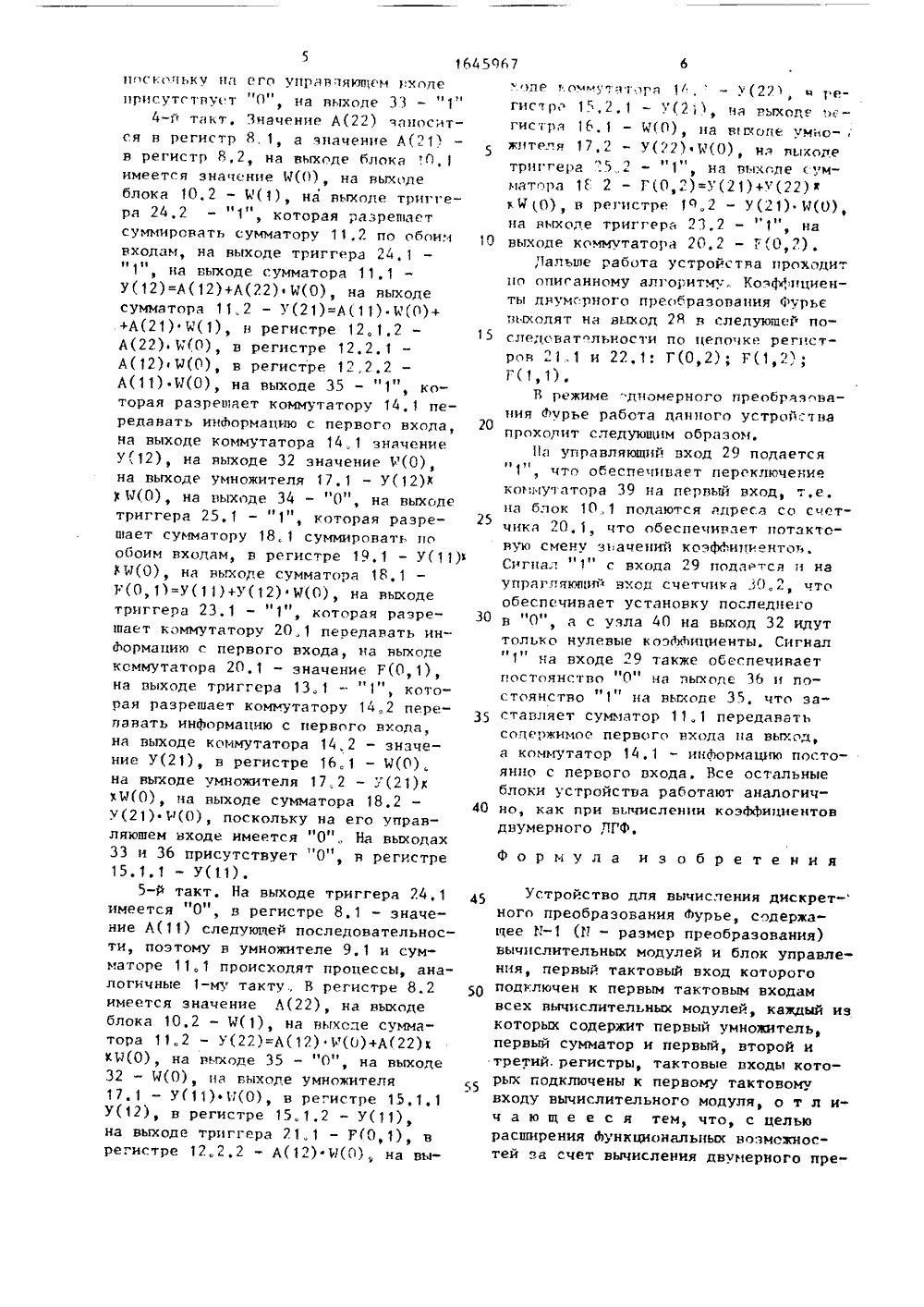

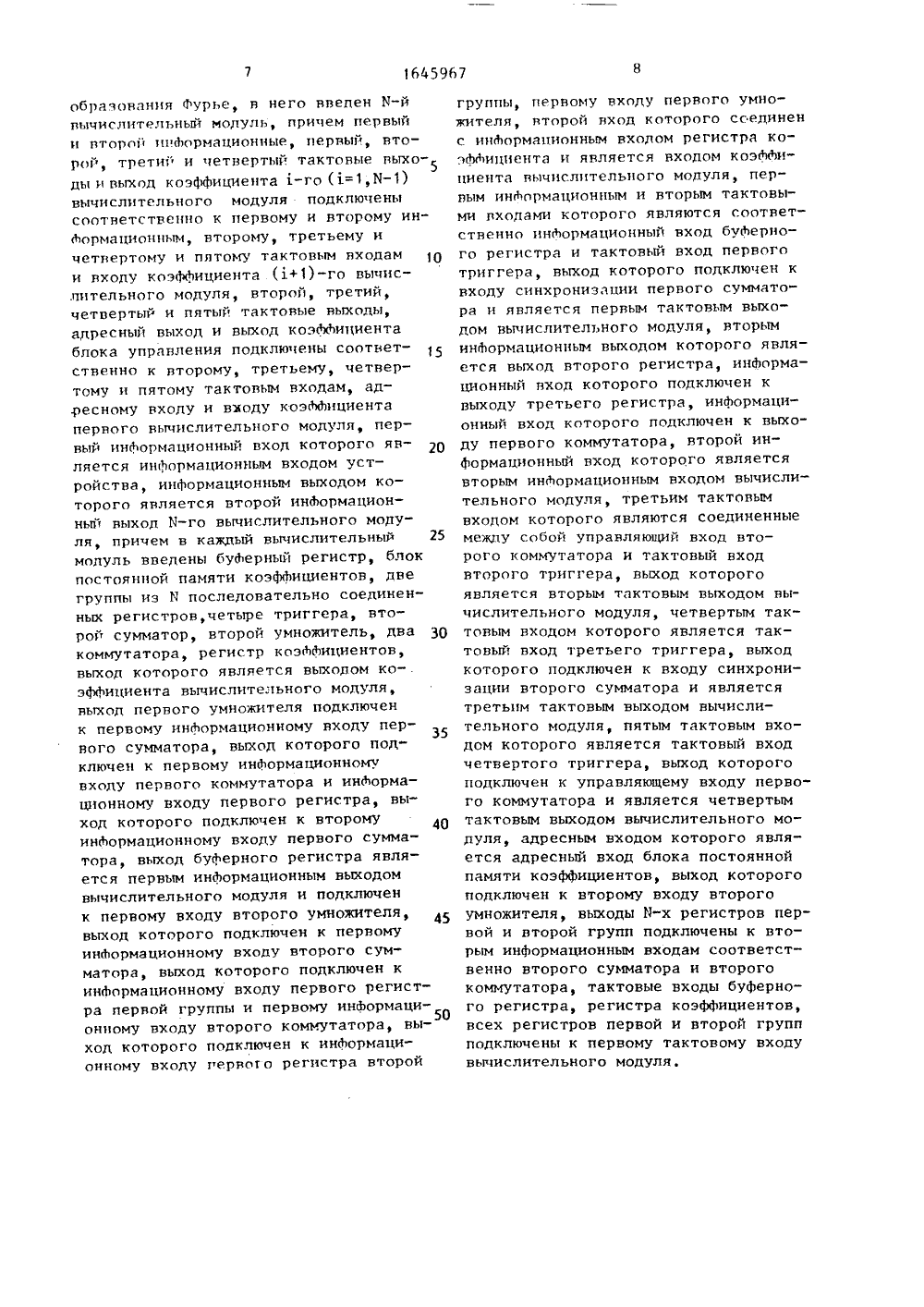

(51) 5 С 06 Р 15/33 ОПИСАНИЕ ИЗОБРЕТЕН ЕЛЬСТВУ ТОРС КОМ Киевскота инстит И.А.Ко нолли сьство СССР5/332, 1984.обработки/ПодМир, с. 349.27 идете06 Еельно Фиг.1 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕВ 1 Я ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ(57) Изобретение относится к вычислнтельноЯ технике, предназначено длявычисления одномерного и двумерногоТРФ и моает быть использовано в системах цифровой обработки различногорода сигналов. Цель изобретения - раширение Функциональных возмозностейэа счет вычисления двумерного дискретного преобразования Фурье. Посталенная цель достигается за счет того1645967 А(11) А(12) А(21) А(22) что в устройство входят блок управления, Н (Б - размер преобразования),вычислительных модулей 3. 1-3,И, каждый иэ которых содержит буферный Регистр 8, умножитель 9, блок 10 постоянной памяти коэффициентов, сумИзобретение относится к вычислительной технике, предназначено длявычисления двумерного и одномерного 15ЛПФ и может быть использовано в системах цифровой обработки различногорода сигналов,1 ель изобретения - расширение Функциональных возможностей эа счет вычисления двумерного дискретного преобразования Фурье,На фиг, 1 и 2 приведена структурная схема устройства для вычисленияРЗЪь; на Фиг. 3 - структурная схема 25блока управления устройством для вычисления двумерного 7 тПФ.Устройство содержит информационныйвход 1, блок 2 управления, Б вычислительных модулей 3,1-3.11 (Н - размер 30преобразования), каждый из которыхсодержит вход 4 коэффициента, информационный вход 5, тактовые входы 6 и 7,буферный регистр 8, умножитель 9,блок 10 постоянной памяти коэффициентов, сумматор 11, группу регистров12, триггер 13, коммутатор 14 группу регистров 15, регистр 16 коэффициентов, умножитель 17, сумматор 18,истр 19 коммутатор 20 реры 4021 и 22, триггеры 23-25, тактовыйвход 26, адресный вход 27 и информационный выход 28.Блок 2 управления (Фиг, 3) содержит управляющий вход 29счетчики 30.145и 30,2, элемент НЕ 31, выходы 32-37,установочный вход 38, коммутатор 39,узел 40 постоянной памяти, дешифраторы 41,1 и 41,2, элемент И 42, элементИЛИ 43 и генератор 44 импульсов.Рассмотрим работу устройства в режиме вычисления двумерного ГПФ.,пля определенности полагаем И 2,допускаем, что коммутаторы 39, 14,1и 20.1 при "0" на управляющем входепередают информацию со второго своеговыхода, а сумматоры 111 и 18,1 при0" на управляющем входе производят матор 11, группа регистров 12, триггер 13, коммутатор 14, группа регистров 15, регистр коэффициентов 16,умножитель 17, сумматор 18, регистр19, коммутатор 20, регистры 21, 22 итриггеры 23, 24, 25, 3 ил. сложение содержимого на первом входе с нулем и при "1" на управляющем входе производят сложение содержимого первого и второго входов.Входные отсчеты непрерывным пото" ком поступают на вход 1: 1-й такт. Операнд А(11) заноситсяв регистр 8. 1. На выходе блока 101имеется значение ЩО), на выходе умножителя 9.1 - значение А(11) У(0),которое передается на выход сумматора 11. 1, поскольку на управляющем вхо"де у него присутствует "0",2-й такт. Значение А(12) заносится в регистр 8.1, на выходе блока10,1 имеется значение У(0), на выходеумножителя 9. 1 и сумматора 11. 1значение А(12) У(0), в регистре12.1.1 - значение А(11) Н(0), в регистре 8,2 - значение А(11), на выходеблока 10.2 - ЩО)на выходе умножителя 9,2 и сумматора 10.2 - значениеА(11) ЩО). На выходе 36 присутствуи 1 ц3-й такт. Значение А(21) заноситсяв регистр 8.1, значение А(12) - в регистр 8,2, на выходе блока 10.1имеется значение ЩО), на выходе блока 10.2 - Ч(О), на выходе триггера24,1 - " 1", которая разрешает суммировать сумматору 11,1 по обоим входам,на выходе сумматора 11,1 имеется зна"чение У(11)=А(11)+А(21) ЩО), на выходе сумматора 11,2 - А(12)У(0), в регистре 12,1.1 - А(12)фЩО), в регистре12, 1,2 - А(11)фИ(0), в регистре12.2,1 - А(11)аЩО), на выходе 35 -" 1", которая разрешает коммутатору14,1 передавать информацию с первоговхода, на выходе коммутатора 14,1значение У(11), на выходе 32 значениеИ(0), на выходе умножителя 17,1У(11) ЩО), на выходе 34 - "1", навыходе сумматора 18,1 - У(11)фИ(0). пеомл утато а 1(,- У (221 цеЭгистр 15,2, - У(2 1, на выходе оегистра 6,1 - 7(0), на вгсоде ум 1 о-жителя7, 2 - У(22)ъ(0), на вы содетриггера .5,2 - "1", на выходе силатора 1 Г 2 - Г(0,2)=У(21)+У(22)фЧО), в регистре с 12 - У(21)ЩО),на выходе триггера 23,2 - "1", на10 выходе коммутатор 20,2 - 1(О 2),,1 алыче работа устройства проходитпо описанному алгоритму. Коэ 4 н;ициенты Лвумг.рного прес 1 бразования Фурьевьхолят на выход 28 в следующей по 5 следовательности по цепочке регистров 21,1 и 22.1: Г(0,2); Г(1,21;Г(1,1),В режиме -дномерного преобразова 20ния Фурье работа данного устройствапроходит следующим образом.1 а управляющий вход 29 подается11, что обеспечивает переключениеколнмутатора 39 на первый вход, т,е,на блок 10,1 подаются адреса со счет 25чика 0,1, что обеспечивает потактовую смену значений каэфФипиенто 1,Сигнал с входа 29 пода"тся и наупрагляющий вход счетчика 30.2, чтообеспечивает установку последнегоЗО в "0", а с узла 40 на выход 32 идуттолько нулевые коэААициенты Сигнал"1" на входе 29 также обеспечиваетпостоянство "0" на выходе 36 и постоянство на вьвсоде 35, что заставляет сумматор 111 передаватьсодержимое первого входа па выход,а коммутатор 14,1 - информацию постоянно с первого входа. Все остальныеблоки устройства работают аналогич 40 но, как при вычислении коэФФициентовдвумерного,пГФ,Формула изобретения 45 Устройство для вычисления дискрет-ного преобразования Фурье, содержащее 11-1 (1 - размер преобразования)вычислительных модулей и блок управления, первый тактовый вход которогоподключен к первым тактовым входамвсех вычислительных модулей, каждый изкоторых содержит первый умножитель,первый сумматор и первый, второй итретий. регистры, тактовые входы которых подключены к первому тактовомувходу вычислительного модуля, о т л ич а ю щ е е с я тем, что, с цельюрасширения Аункциональньсх воэможностей за счет вычисления двумерного пре 1645 с 67и 1 с к.чику на его управаяюпел 1 входеприсутствует "0", на выходе ЗЗ - " 1"4-й такт, Значение А(22) заносится в регистр 8, 1, а значение А(21)в регистр 8,2, на выходе блока О,имеется значение 1(О), на выходеблока 10,2 - с(1), на выходе триггера 24,2 - "1", которая разрешаетсуммировать сумматору 11,2 по обоимвходам, на выходе триггера 24.111 111 , на выходе сумматора 1 1, 1У ( 1 2 ) =А ( 1 2 ) +А ( 2 2 )Щ 0 ) , на выходесумматора 1 1 . 2 - У ( 2 1 ) = А ( 1 1 )ы ( Р ) ++А ( 2 1 )1( 1 ) , в ре гистре 1 2 . 1, 2А ( 2 2 ) Ъ( 0 ) , в регистре 1 2 . 2 , 1А(12)У(0), в регистре 12,2.2А(11) ЩО), на выходе 35 - "1", которая разрешает коммутатору 14, передавать информацию с первого входа,на выходе коммутатора 141 значениеУ(12), на выходе 32 значение (0),на вьпсоде умножителя 17, 1 - У(12)сМО), на выходе 34 - "0", на выходетриггера 25, 1 - " 1", которая разрешает сумматору 181 суммировать псобоим входам, в регистре 19,1 - У(11)1 И(0), на выходе сумматора 18,1Г(0=У(1)+У(12) И(0), на выходетриггера 23. 1 - " 1", которая разрешает коммутатору 201 передавать инФормацию с первого входа на выходекоммутатора 20,1 - значение Р(0,1)на выходе триггера 13.1 - "1", которая разрешает коммутатору 14,2 перелавать информацию с первого входа,на выходе коммутатора 14,2 - значение У(2 1), в регистре 16,1 - И(Р),на вьгсоде умножителя 17,2 - У(2 1)хУ(0), на выходе сумматора 18.2У(21) Н(0) поскольку на его управляюшем входе имеется 1011 На выходах33 и 36 присутствует "0", в регистре15. 1. 1 - У( 1.1) .5-й такт. На выходе триггера 24,1имеется "0", в регистре 8,1 - значение Л(11) следующей последовательности, поэтому в умножителе 9,1 и сумматоре 11. 1 происходят процессы, аналогичные 1-му такту В регистре 8.2имеется значение Л(22), на выходеблока 10,2 - И(1), на выходе сумматора 11,2 - У(22)=А(12) 1(О)+А(22)ХсУ(0), на выходе 35 - "0", на выходе32 - И(0), на выходе умножителя171 - У(11)ф И(0), в регистре 15,1,У(12), в регистре 15. 1.2 - У(11),на выходе триггера 2 11 - Г(011), врегистре 12.2,2 - А(12) Н(О), на вы 1645967образования Фурье, В него введен У-й вычислительный модуль, причем первый и второй информационные, первый, второй третий и четвертый тактовые выхоФ 5 ды и выход коэффициента 1-го (д=1,М) вычислительного модуля подключены соответственно к первому и второму индормационньпч, второму, третьему и четвертому и пятому тактовым Входам и входу коэффициента (1+1)-го вычислительного модуля, второй, третий, четвертый и пятый тактовые Выходы, адресный выход и выход коэФФициента блока управления подключены соответственно к второму, третьему, четвертому и пятому тактовым входам, ад.Ресному входу и входу коэААициента первого вычислительного модуля, перВыи информяционныи Вход котОРОГО яВ- ляется информационным входом устройства, информационным выходом которого является второй информационный выход Б-го вычислительного модуля, причем в каждый вычислительный 25 модуль введены буФерный регистр, блок постоянной памяти коэффициентов, две группы из И последовательно соединенных регистров, четыре триггера, второй сумматор, второй умножитель, два ЗО коммутатора, регистр коэФфициентов, выход которого является выходом ко-.эфФициента вычислительного модуля, выход первого умножителя подключен к первому информационному входу первого сумматора, выход которого подключен к первому информационному входу первого коммутатора и информационному входу первого регистра, выход которого подключен к втоРому 4 О инФормационному входу первого сумматора, выход буферного регистра является первым информационным выходом вычислительного модуля и подключен к перВому ВХОДУ ВТОРОГО УмножителЯ 45 выход которого подключен к первому инФормационному входу второго сумматора, выход которого подключен к информационному входу первого регистра первой группы и первому информационному входу второго коммутатора, выход которого подключен к информационному входу первого регистра второй группы, первому Входу первого умно- жителя, Второй вход которого ссединен с инФормационным входом регистра коОЮ 1 ициента и является входом коэМициента Вычислительного модуля, первым инФормационным и вторым тактовыми входами которого являются соответственно информационный вход буферного регистра и тактовый вход первого триггера, выход которого подключен к входу синхронизации первого сумматора и является первым тактовым выходом вычислительного модуля, вторым информационным выходом которого является выход второго регистра, информационный Вход которого подключен к выходу третьего регистра, информационный вход которого подключен к выходу первого коммутатора, второй информационный вход которого является вторым информационным входом вычислительного модуля, третьим тактовым входом которого являются соединенные между собой управляющий вход второго коммутатора и тактовый вход второго триггера, выход которого является вторым тактовым выходом вычислительного модуля, четвертым тактовым входом которого является тактовый вход третьего триггера, выход которого подключен к входу синхронизации второго сумматора и является третьим тактовым выходом вычислительного модуля, пятым тактовым входом которого является тактовый вход четвертого триггера, выход которого подключен к управляющему входу первого коммутатора и является четвертым тактовым выходом вычислительного модуля, адресным входом которого является адресный вход блока постоянной памяти коэффициентов, выход которого подключен к второму входу второго умножителя, выходы И-х регистров первой и второй групп подключены к вторым информационным входам соответственно второго сумматора и второго коммутатора, тактовые входы буферного регистра, регистра коэффициентов, всех регистров первой и второй групп подключены к первому тактовому входу вычислительного модуля.1 б 45967 фиг. Л Составитель А. Бараноедактор Л.Пчолинская Техред Л,Олийнык рректор Л.Пвт Заказ 1351 415 Подписно Производственно-издательский комбинат Патент , г. Уан 19 л. Гагарина, 101 И Государственного 113035, омитета по осква Жбретениям и открытиям при ГКНТ СССРаушская наб., д. 4/5

СмотретьЗаявка

4683075, 24.04.1989

ЖИТОМИРСКИЙ ФИЛИАЛ КИЕВСКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

КОРЧЕВ ДМИТРИЙ ВЕНИАМИНОВИЧ, КОНОПЛИЦКИЙ ИГОРЬ АНАТОЛЬЕВИЧ, КАНЕВСКИЙ ЮРИЙ СТАНИСЛАВОВИЧ

МПК / Метки

МПК: G06F 15/332

Метки: вычисления, дискретного, преобразования, фурье

Опубликовано: 30.04.1991

Код ссылки

<a href="https://patents.su/5-1645967-ustrojjstvo-dlya-vychisleniya-diskretnogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления дискретного преобразования фурье</a>

Предыдущий патент: Устройство для вычисления преобразования фурье галуа

Следующий патент: Спектроанализатор

Случайный патент: Установка для непрерывного изготовления стружечных плит