Устройство для логарифмирования двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

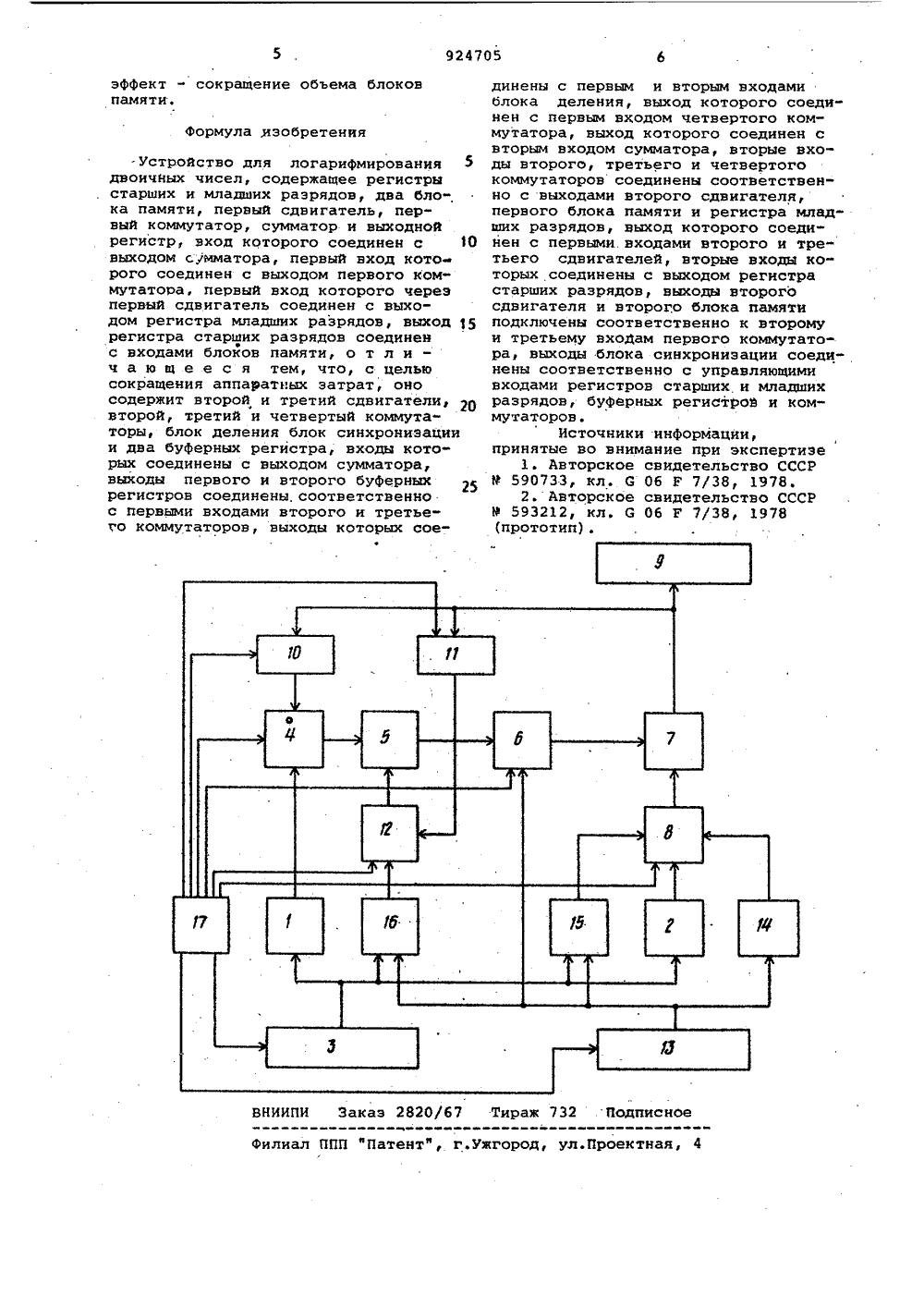

ОПИСАНИЕИЗОБРЕТЕИИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик п 11924705(51 М. Кп.з с присоединением заявки Мо О 06 Р 7/556 Государственный комитет СССР по делам изобретений и открытий(088.8) Дата опубликования описания 30.0482(71) Заявитель Омский политехнический институт(54) УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ ДВОИЧНЫХ ЧИСЕЛИзобретение относится к вычисли- тельной технике и может быть использовано в качестве цифрового генера" тора значений логарифмической Функции.Известно устройство, содержащее регистры числа и результата, блок деления, схему сравнения, накопитель, сдвиговый регистр и блок управления (1) .Недостатком .данного устройстваявляется низкое быстродействие.Наиболее близким по технической сущности к предлагаемому является135 устройство для логарифмирования двоичных чисел, которое содержит регистр старших разрядов аргумента, соединенный с адресными входами двух блоков памяти и регистр младших разрядов аргумента, выход которого через сдвийатель, первый коммутатор и .сумматор подключен к.выходному регистру (2)Недостатком известного устройства является большой объем постояв" ной памяти, требуемой для хранения таблиц коэФФициЕнтов; что существен" но сужает область применения подоб" ных устройств и позволяет испольэо" вать их лишь в малоразрядных ЦВМ(не более 12 - 16 разрядов) . Для аргумента длиной 24 двоичных разряда объем таблиц составляет 119,2, бит., что не позволяет применять данное устройство в качестве узла универсальных ЗВМ.Цель изобретения - сокращение аппаратных затрат.Поставленная цель достигается тем, что в устройство, содержащее регистры старших и младших разрядов, два блока памяти, первый сдвигатель, первый коммутатор, сумматор и выходной регистр, вход которого соединен с выходом сумматора, первый вход которого соединен с выходом первого коммутатора, первый вход которого через первый сдвигатель соединен с выходом регистра младших разрядов, выход регистра старших разрядов соединен с входами блоков памяти, содержит второй и третий сдвигатели, второй, третий и четвертый коммутаторы, блок деления, блок синхронизации и два буферных регистра, входы которых соединены с выходом сумматора, выходы первого и второго буферных регистров соединены соответственно с первыми входами второго и третьего коммутаторов, выходы кото 924705рых соединены с первым и вторым входами блока деления выход которогосоединен с первым входом четвертогокоммутатора, выход которого соединен с вторым входом сумматора, вторыевходы второго, третьего и четвертого коммутаторов соединены соответственно с выходами второго сдвигателя,первого блока памяти и регистра младших разрядов, выход которого соединенс первыми входами второго и третьего 10сдвигателей, вторые входы которыхсоединены с выходом регистра старших разрядов, выходы второго сднигателя и второго блока памяти подклю"чены соотнетственно к второму и 15третьему входам перного коммутатора,выходы блока синхронизации соединенысоответственно с управляющими входами регистрбв старших и младшихразрядов, буферных регистров и коммутаторов.Вычисление натурального логарифмаот нормализованного аргумента Х(1/2 " Х ( 1) производится в предлагаемом устройстве на основе следующих соотношений Ь пХ -, 11(х),где 30 3 ЬМП О0(к) =ЯНГХО+9.44 ЧХ- -О 1 ХО+ХЗдесь Хо - опорная часть аргумента,представленная К старшими разрядамиаргумента, а д Х - приращение аргумента, представленное и-К-двоичнымиразрядами, где и - общее количество З 5разрЯдов требуемого для представления аргумента Х. Значения От ХООкзависящие только от опорной частиаргумента, вычисляются предварительно и заносятся в таблицы, реалиэованные на блоках постоянной памяти.Значение параметра Е для получения верными всех и двоичных раэрядонрезультата необходимо при этом взятьиз выражения К = Г(п - 1)/5).Расчеты, проведенные при п=24, показывают, что потребуется хранитьлишь 32 константы длиной 24 разряда.Таким образом, для рассмотренногоустройства по сравнению с устройст. вом-прототипом получается выигрыш в 50объеме блоков памяти более чем в300 раэ,На чертеже представлена блок-схема предлагаемого устройства.Устройство содержит блоки 1 и 2 55памяти, регистр 3 старших разрядаваргумента, коммутатор 4, блок 5 деления, коммутатор б, сумматор 7, коммутатор 8, выходной регистр 9 ре"зультата, регистры 10 и 11 буферные, 60коммутатор 12, регистр 13 младшихразрядов (аргумента), сдвигатели14 - 1 б, блок 17 синхронизации.Сднигатели 15 и 16 реализуют операции 65 Х - ф 4 Х, +ЬХ и Х - ф 2 Х, +ЬХсоответственно, которые заключаютсян добавлении между старшими и младшими разрядами аргумента соответстну"ющего числа нулей (двух и одного),Устройство для логарифмированиядвоичных чисел работает следующимобразом.В первом такте по сигналу с блокасинхронизации 17 адрес Хэ, передаваемый с выхода регистра старших разрядов аргумента З,поступает на нходы блоков памяти 1 и 2, на выходахэтик блоков памяти появляются соответственно значения - 2 Хи1 пХО, а на выходах сдвигателей 15и 1 б - соответственно значения 4 Х++ ь Х и 2 Х О + ь Х. Значения 2 ХОс выхода первого блока 1 памятй через коммутатор 4 по сигналу с блока17 поступает на вход делимого блока5 деления, значение 2 Х+ ь Х свыхода сднигателя 1 б через коммутатор 12 по сигналу с блока 17,поступает на нход делителя блока 5 деления, на выходе которого образуетсяпромежуточный результат Р= .-2 Х//(2 Х+ дХ). Одновременно с этим значение ДХ с выхода регистра младшихразрядов аргумента 13 через коммутатор б по сигналу с блока 17 поступает на второй вход сумматора 7,напервый вход которого поступает значение 2 ДХ, образованное на выходесдвигателя 14, передаваемое черезкоммутатор 8, по сигналу с блока 17.Результат, равный ЗЬХ запоминается вбуФерном регистре 10,Во втором такте по управляющимсигналам с блока синхронизации 17происходит сложение промежуточногорезультата Р, поступающего на сум-матор 7 через коммутатор б, и значения 4 Х О + ДХ, поступающего с выходасдвигателя 15 через коммутатор 8 навход сумматора 7. Промежуточный результат Р= 4 Х О + ЬХ + Р запоминается на втором буферном регистре.В третьем такте значения ЗЬХс выхода буферного регистра 10 через коммутатор 4 поступает на входделимого блока 5 деления, промежуточный результат Р с выхода буферного регистра 11 через коммутатор 12поступает на вход делителя блока 5деления. Промежуточный результатР= ЗДХ/Р с выхода блока 5 деле"ния через коммутатор б передаетсяна вход сумматора 7. На другой входпоследнего поступает значение с выхода второго блока 2 памяти, передаваемое на сумматор 7 через коммутатор 8. Результат Р = ЗпХ О + Р с выхода сумматора 7 поступает на входрегистра результата 9Таким образом, предлагаемое устройство обеспечивает положительный924705 Формула .изобретения НИИПИ Заказ 2820/67 Тираж 732 Подписное илиал ППП фПатентф, г.Ужгород, ул.Проектна эФфект - сокращение объема блоковпамяти. устройство для логариФмирования 5 двоичных чисел, содержащее регистры старших и младших разрядов, два бло" ка памяти, первый сдвигатель, первый коммутатор, сумматор и выходной регистр, вход которого соединен с 10 выходом сумматора, первый вход кото рого соединен с выходом первого коммутатора, первый вход которого через первый сдвигатель соединен с выходом регистра младших разрядов, выход 15 регистра старших разрядов соединен с входами блоков памяти, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратных затрат, оно содержит второй н третий сдвигателис 20 второй, третий и четвертый коммутаторы, блок деления блок синхронизации и два буФерных регистра, входы которых соединены с выходом сумматора, выходы первого и второго буФерных регистров соединены, соответственно с первыми входами второго и третье" го коммутаторов, выходы которых соединены с первым и вторым входамиблока деления, выход которого соеди"нен с первым входом четвертого коммутатора, выход которого соединен свторым входом сумматора, вторые входы второго, третьего и четвертогокоммутаторов соединены соответственно с выходами второго сдвигателя,первого блока памяти и регистра младших разрядов, выход которого соединен с первыми. входами второго и тре"тьего сдвигателей, вторые входы ко"торых соединены с выходом регистрастарших разрядов, выходы второгосдвигателя и второго блока памятиподключены соответственно к второмуи третьему входам первого коммутатора, выходы блока синхронизации соеди"нены соответственно с управляющимивходами регистров старших и младшихразрядов, буФерных регистров и коммутаторов.Источники инФормации,принятые во внимание при экспертизеАвторское свидетельство СССРР 590733, кл, О Об Г 7/38, 1978.2. Авторское свидетельство СССР9 593212, кл. С 06 Р 7/38, 1978

СмотретьЗаявка

2983669, 30.07.1980

ОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ФЛОРЕНСОВ АЛЕКСАНДР НИКОЛАЕВИЧ, ПОТАПОВ ВИКТОР ИЛЬИЧ, ПЛОТНИКОВ МИХАИЛ ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: двоичных, логарифмирования, чисел

Опубликовано: 30.04.1982

Код ссылки

<a href="https://patents.su/3-924705-ustrojjstvo-dlya-logarifmirovaniya-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для логарифмирования двоичных чисел</a>

Предыдущий патент: Устройство для возведения в куб

Следующий патент: Генератор псевдослучайных чисел

Случайный патент: Способ получения арилпиперазиновых производных аденина или их солей