Дельта-сигма-модулятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1599992

Автор: Малов

Текст

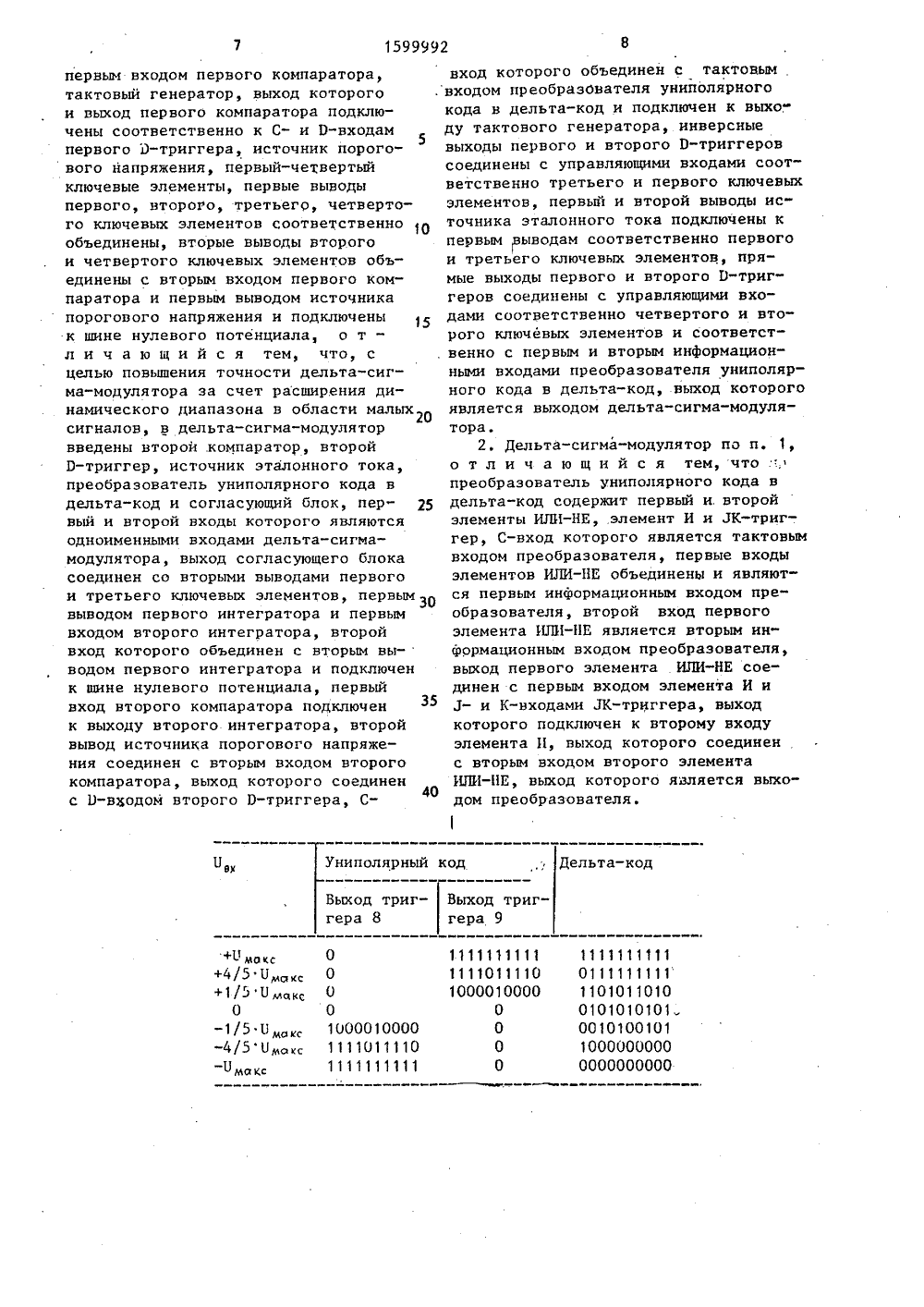

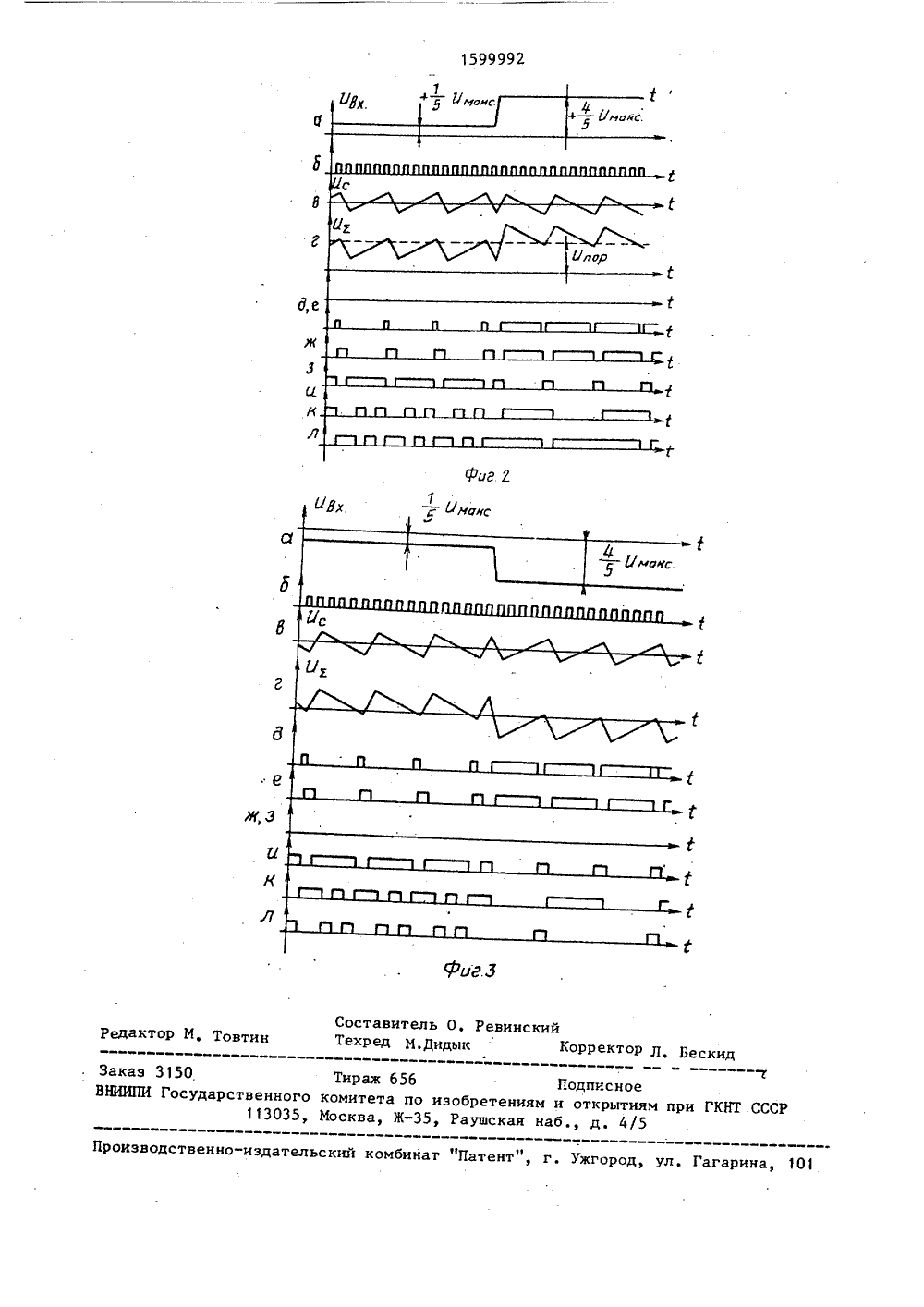

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах передачи информации.5Цель изобретения - повышение точности за счет расширения динамического диапазона в области малых сигна-.лов.На фиг. 1 приведена функциональная схема дельта-сигма-модулятора;на фиг. 2 и 3 - временные диаграммыего работы.Дельта-сигма-модулятор содержитсогласующий блок 1, первый и второйинтеграторы 2, 3, первый и второйкомпараторы 4, 5, источник б порогового напряжения, тактовый генератор7, первый и.второй 0-триггеры 8, 9,источник 10 эталонного тока, первыи - четвертый ключевые элементы11-14 и преобразователь 15 униполярного када в дельта-код. На фиг.обозначены первый и второй входы16, 17,Согласующий блок 1 обеспечиваеттоковый выход, т.е. высокое выходноесопротивление, Он может быть выполнен на дифференциальных усилителях18, 19 и резисторах 2-25 или по любой иной схеме с токовым выходом изаземленной нагрузкой. Высокое выходное сопротивление обеспечивается вприведенном примере при 25 В дельта-сигма-модуляторе реализована двухканальная структура,с разде лением полярности входного сигнала и использованием импульсной обратной связи 35Выходной ток блока 1 равен Е = Жв-, - Б )К где У Бхд- сигналы наьх вк 2входах 16, 17; К, = ----- коэффиКяО К 25 40 циент передачи блока 1.Первый интегратор 2 представляет собой конденсатор.Второй интегратор 2 может быть выполнен на дифференциальном усилителе 45 26, конденсаторе 27 и резисторе 28. Его передаточная характеристика1ы(г) . - . 1 + --- , --г кдсгПреобразователь 15 униполярного ко- да в дельта-код содержит 1 К-триггер 29, первый и второй элементы ИЛИ-НЕ 30, 31 и элемент И 32. Первый компаратор 4, первый Р- триггер 8 и ключевые элементы 11, 12 образуют первый канал компенсации для входного сигнала отрицательной полярности. Второй канал компенсации для входного сигнала положительной полярности образован вторым компаратором 5 с источником 6 порогового напряжения, вторым триггером 9 и ключевыми элементами 13, 14Для устойчивого разделения полярности входного сигнала пороги срабатывания первого и второго компараторов 4, 5 должны быть разнесены на величину найряжения порогового источника 6, определяемого из условия БорЕ "Е /Сгде Е - значение эталонного тока исЭтточника 10;Т - период тактовой частоты генератора 7;С - емкость конденсатора 2,Постоянная времени. К С интегратора 3 выбирается на порядок больше постоянной времени интегратора 2, что можно записать в виде выражения Ку" С ) 10 1При выполнении данного условия среднее напряжение на выводах интегратора 2 равно нулю независимо от величины и полярности входного сигнала. Полученное свойство исключает влияние сопротивления утечки интегратора 2 и параллельно подключенных к нему элементов. Достигается равенство зарядоз , уравновешивания интегратора 2 для входного сигнала двух полярностей, несмотря на построение преобразователя по двухканальной структуре с разделением полярностей с помощью двух компараторов со смещенными порогами срабатывания.Ключевые элементы 11-14 включаются при появлении на управляющем входе "0", а выключаются сигналом "1".На фиг. 2 и 3 обозначены: О разность напряжений на входах 16 и 17; о - импульсы тактовой частоты генератора 7; о - пилообразное напряжение на выводах интегратора 2; пилообразное напряжение с постоянной составляющей на выходе интегратора 3;" импульсы на выходе первого компаратора 4; е - импульсы на выходе первого 0-триггера 8; ж - импульсы на выходе второго компаратора 5 ф - импульсы на выходе второго 0-тригге 1599992ра 9; ц - импульсы на выходе элемента ИЛИ-НЕ 30; К - импульсы на выходеЗК-триггера 29; й - выходные импульсы дельта-сигма-модулятора на выходеэлемента ИЛИ-НЕ 31,5Временные диаграммы (фиг. 2) раскрывают процесс получения выходногодельта-кода для положителЬного входного напряжения двух уровней 10вх 5 мас и 5 максгде У - максимально возможное входное напряжение.Временные диаграммы фиг. 3 раскрывают процесс получения выходногодельта-хода для отрицательного входного напряжения двух уровней:1 4Нвх 5 Нмакс и Н вх 5 смаке,Дельта-сигма-модулятор работаетследующим образом.Разность напряжений с входов 1 б,17 с помощью блока 1 преобразуется впропорциональный ток и заряжает конденсатор 2. При положительном входном напряжении Ннапряжение У навыводах конденсатора 2 начинает увеличиваться (фиг. 2, в). НапряжениеН на выходе интегратора 3 равно сумме напряжения на выводах конденсатора2 и напряжения на выводах конденсатора 27, поэтому по форме оно будетповторять напряжение Б , но будетсмещено на величину практически постоянного напряжения на выводах конденсатора 27, равного интегралу отнапряжения Б . При превышении напряжением 0 положительного порога срабатывания второго компаратора 5, определяемого источником б, второй компаратор 5 выдает единичный импульс,устанавливая второй Ъ-триггер 9 вединичное состояние по приходу фронта тактового импульса генератора 7на С-вход триггера 9, В этом случае 45начинает работать второй канал компенсации, а первый канал компенсации"молчит", так как его элементы 4 и 8находятся в нулевом состоянии. Формирователь биполярного эталонного тока, 50образованный элементами 10-15, будетвыдавать импульсы эталонного тока отрицательной полярности, компенсирующиезаряд интегратора 2 от положительноговходного напряжения. На второй вход 55преобразователя 15 будет поступатьпоследовательный уииполярный код.На выходе преобразователя 15 будетсформирован дельта-код, гропорцнональныи униполярному коду и, соответственно, пропорциональный величине и полярности входного напряжения,При отрицательном входном напряжении Б(фиг. Зв) напряжение У на выводах конденсатора 2 будет уменьшаться, При этом будет работать первый канал компенсации, а второй канал компенсации будет выключен, так как его второй компаратор 5 будет находиться в нулевом состоянии. Формирователь биполярного эталонного тока будет выдавать импульсы эталонного тока положительной полярности, компенсирующие отрицательный заряд конденсатора 2 от отрицательного входного напряжения. На первый вход преобразователя 15 будет поступать последовательный униполярный код.Коэффициент передачи от выхода блока 1 до входов преобразователя 15 определяется только величинами 1 эталонного источника 10 и периодом Т тактового генератора, Частота потявления единичных посылок в униполярном коде длительностью Тт будет пропорциональна величине (Бв Нва )" кК 3 Е /Тэ В целом логика преобразо вания отражена в таблице.В таблице выходной код расшифрован в течение времени равного 10 Т т. Величина Бма, определяется выражением:Положительный эффект достигается благодаоя снижению частоты переключения ключевых элементов 11-.14 в области малого сигнала со значения Г-./2, до практически нулевого значения и симметрированню коэффициентов передачи для входного напряжения положительной и отрицательной полярности путем использования общего источника 10 эталонного тока. При отсутствии входного сигнала отсутствует перезаряд интегратора 2 импульсами эталонного тока, т.е. уменьшено количество. эталонного электричества, участвующего в процессе уравновешивания входного сигнала малой величины. При этом необходимыи на высоте дельта-код типа меандрвосстанавливается цифровым способом с помощью ЗК-триггера 29.Формула изобретения1, Дельта-си гма-модуля тор, содержащий первый интегратор, второй интегратор, выход которого .:н.дпнен с-4/5Омам ксЦ макс первым входом первого компаратора, тактовый генератор, выход которого и выход первого компаратора подключены соответственно к С- и П"входам5 первого д-триггера, источник порогового напряжения, первый-четвертый ключевые элементы, первые выводы первого, второго, третьего, четвертого ключевых элементов соотвеТственно объединены, вторые выводы второго и четвертого ключевых элементов объединены с вторым входом первого компаратора и первым выводом источника порогового напряжения и подключены к шине нулевого потенциала, о т - л и ч а ю щ и й с я тем, что, с целью повышения точности дельта-сигма-модулятора за счет расширения динамического диапазона в области малых сигналов, в дельта-сигма-модулятор введены второи компаратор, второй П-триггер, источник эталонного тока, преобразователь униполярного кода в дельта-код и согласующий блок, пер вый и второй входы которого являются одноименными входами дельта-сигма- модулятора, выход согласующего блока соединен со вторыми выводами первого и третьего ключевых элементов, первым ЗО выводом первого интегратора и первым входом второго интегратора, второй вход которого объединен с вторым выводом первого интегратора и подключен к шине нулевого потенциала, первый вход второго компаратора подключен к выходу второго интегратора, второй вывод источника порогового напряжения соединен с вторым входом второго компаратора, выход которого соединен с 0-входом второго Р-триггера, С 40 вход которого объединен с тактовым входом преобразователя униполярного кода в дельта-код и подключен к выхо; ду тактового генератора, инверсные выходы первого и второго Э-триггеров соединены с управляющими входами соответственно третьего и первого ключевых элементов, первый и второй выводы источника эталонного тока подключены к первым выводам соответственно первого и третьего ключевых элементов, прямые выходы первого и второго 0-триггеров соединены с управляющими входами соответственно четвертого и второго ключевых элементов и соответственно с первым и вторым информационными входами преобразователя униполярного кода в дельта-код, .выход которого является выходом дельта-сигма-модулятора.2. Дельта-сигма-модулятор по п. 1, о т л и ч а ю щ и й с я тем, что .".,1 преобразователь униполярного кода в дельта-код содержит первый и, второй элементы ИЛИ-НЕ, элемент И и,Ж-триггер, С-вход которого является тактовым входом преобразователя, первые входы элементов ИЛИ-НЕ объединены и являются первым информационным входом преобразователя, второй вход первого элемента ИЛИ-НЕ является вторым информационным входом преобразователя, выход первого элемента ИЛИ-НЕ соединен с первым входом элемента И и 3- и К-входами Ж-триггера, выход которого подключен к второму входу элемента И, выход которого соединен с вторым входом второго элемента ИЛИ-НЕ, выход которого является выходом преобразователя.1599992 ь О. РевинскийДидык Корректор Л. Беск Редакт Товтин Заказ 3150, Тираж 656ВНИИПИ Государственного комитета по изобретения113035, Москва, Ж, Раушская ьский комбинат "Патент", г. Ужгор оизводственно-изда агарина, 1 СоставиТехред одписное открытиям при ГКНТ СССР д. 4/5

СмотретьЗаявка

4479290, 05.09.1988

ПРЕДПРИЯТИЕ ПЯ В-2969

МАЛОВ ВЛАДИМИР СЕМЕНОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-сигма-модулятор

Опубликовано: 15.10.1990

Код ссылки

<a href="https://patents.su/5-1599992-delta-sigma-modulyator.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-сигма-модулятор</a>

Предыдущий патент: Преобразователь кода в скорость вращения вала

Следующий патент: Преобразователь биполярного кода

Случайный патент: Наконечник криохирургического инструмента