Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

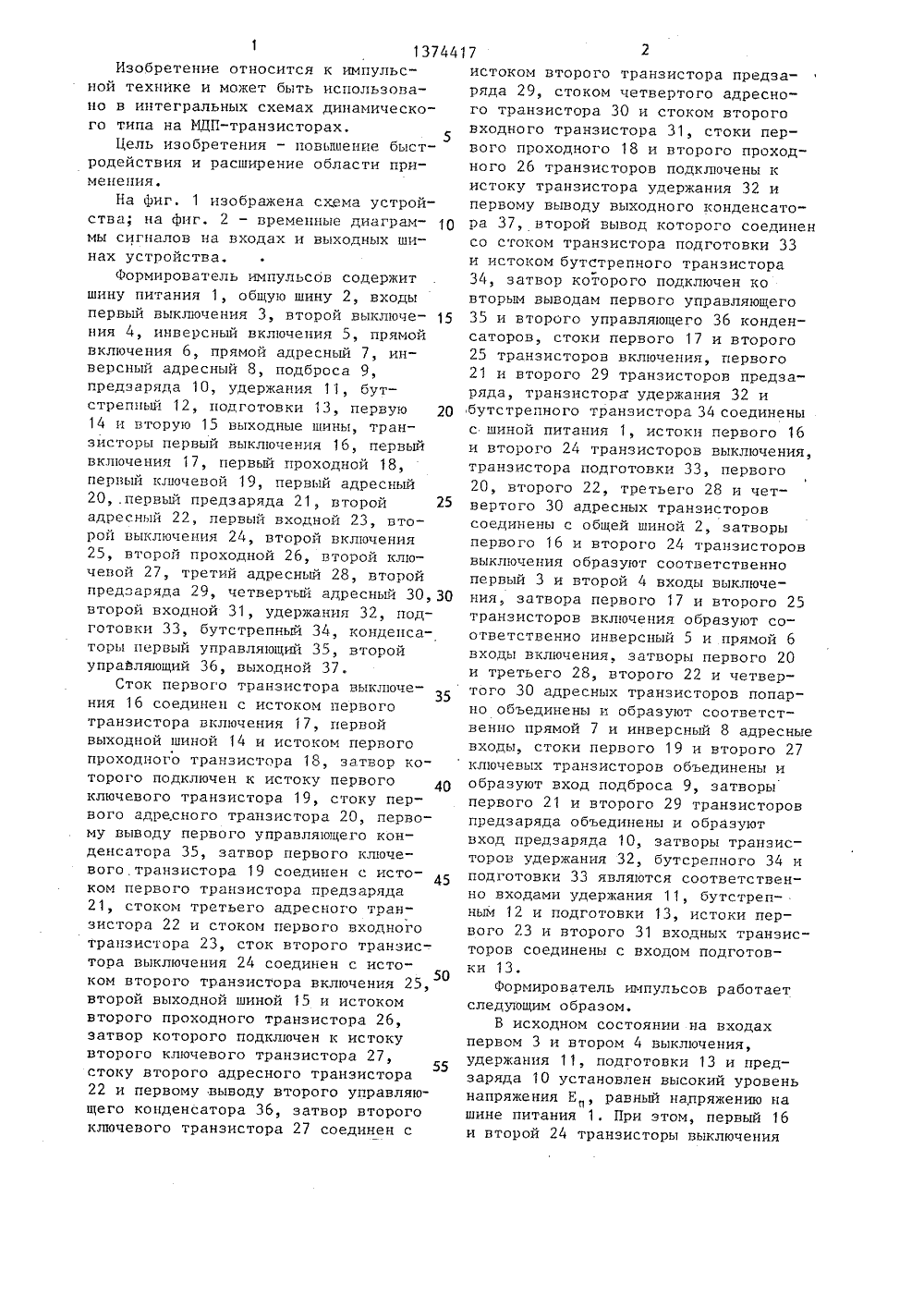

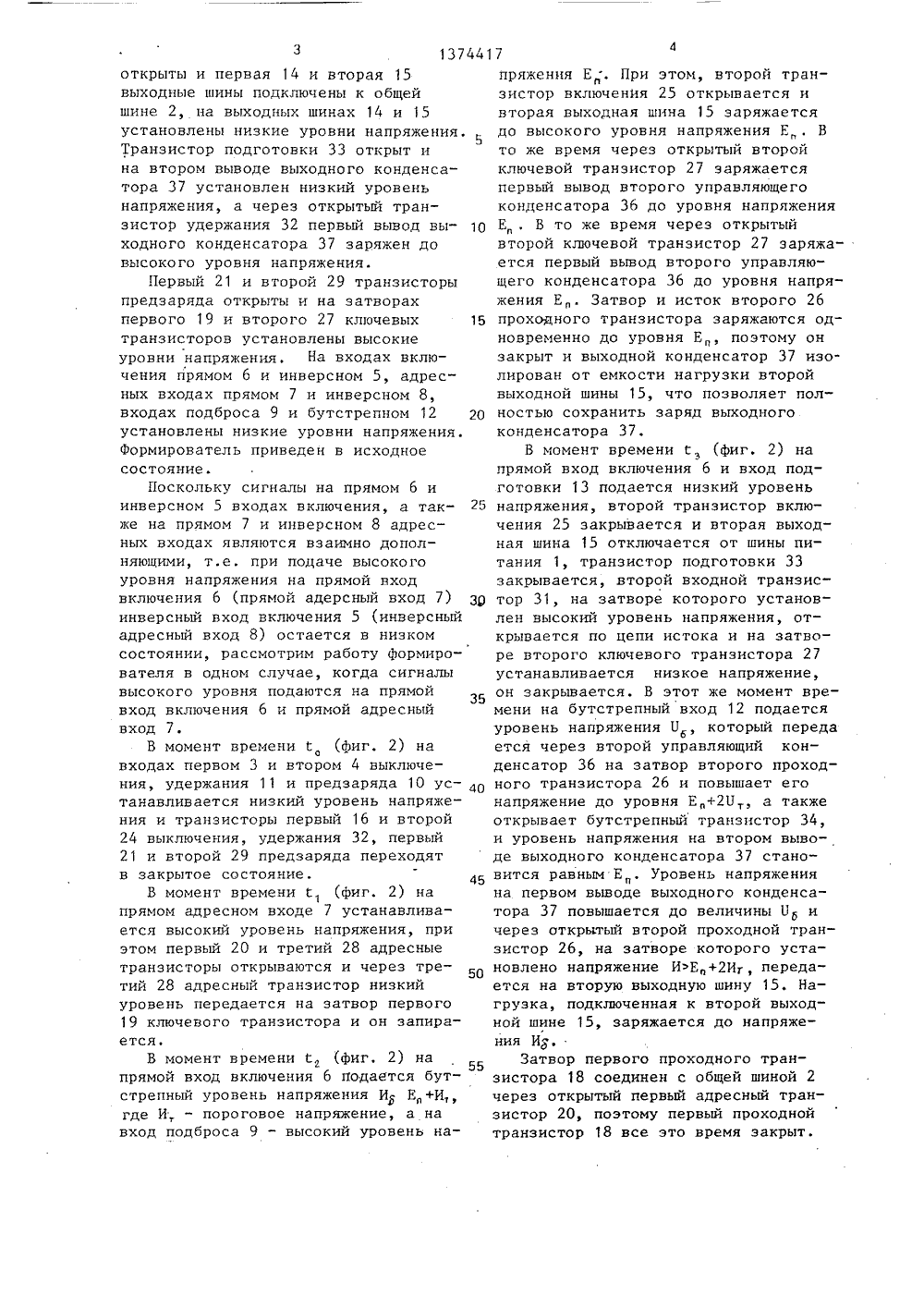

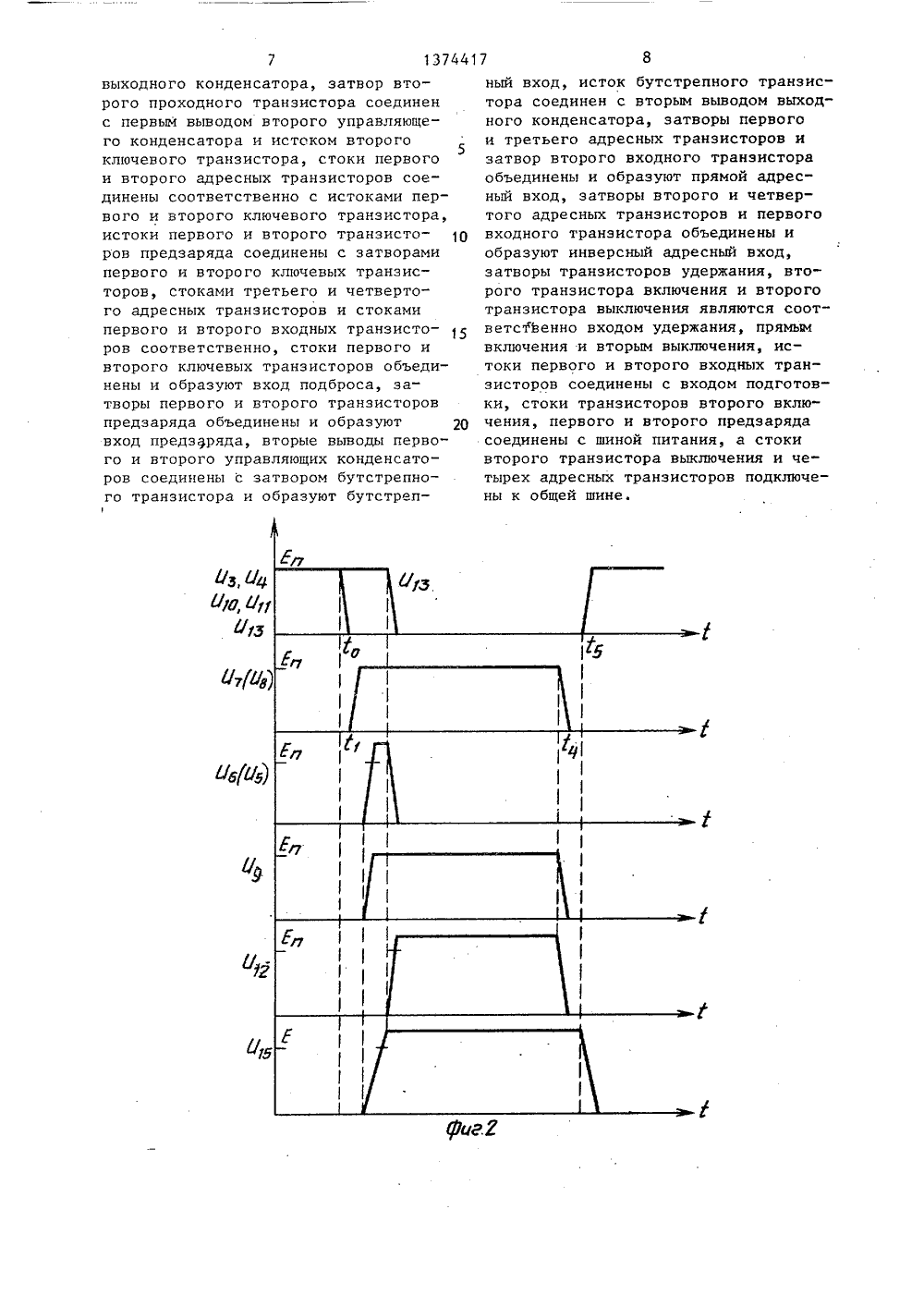

(51)4 и 03 К 5/13 ИСАНИЕ ИЗОБРЕТЕНИЯ СВИДЕТЕПЬОТ Н АВТОРЧИК(56) Заявка Франции Мкл. Н 03 К 17/60, 1980 6И. Макаровлицын 432799,ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(5) Изобретение мохет быть использовано в интегральных схемах динамического типа на МДП - транзисторах.Целью изобретения является повышениебыстродействия формирователя и расширение области его применения. Формирователь содержит шину 1 питания,общую шину 2, входы: выключения 3 и4, инверсный включения 5, прямойвключения б, прямой адресный 7, инверсный адресный 8, подброса 9, перезаряда 10, удерхания 11, бутстрепный 12, подготовки 13; выходные шиЯО 1374417 А 1 ны: первую 14, вторую 15; транзисторы; включения 16 и 24, включения 17и 25, проходной 18, ключевые 19 и27, адресные 20, 22, 28 и 30, перезаряда 21 и 29, входные 23 и 31, проходной 26, удержания 32, подготовки33, бутстрепный 34; конденсаторы:управляющие 35 и 36, выходной 37.Расширение области применения достигается за счет введения второй выходной шины 15, что позволяет использовать формирователь без дополнительного блока селекции сигнала приполучении сигнала по двум шинам, Формирователь предпочтительно использовать для формирования сигнала выборки строки и/или столбца, посколькупервая и вторая выходные шины полностью независимы по управлению. Снижение емкости на каждой выходной шинепо сравнению с прототипом повышаетбыстродействие предложенного формирователя импульсов. 2 ил.137441Изобретение относится к импульсной технике и может быть использовано в интегральных схемах динамического типа на ИДП-транзисторах,5Цель изобретения - повышение быстродействия и расширение области применения.На фиг. 1 изображена схема устройства; на фиг. 2 - временные диаграммы сигналов на входах и выходных шинах устройства,Формирователь импульсов содержитшину питания 1, общую шину 2, входыпервый выключения 3, второй выключения 4, инверсный включения 5, прямойвключения б, прямой адресный 7, инверсный адресный 8, подброса 9,предзаряда 10, удержания 11, бутстрепный 12, подготовки 13, первую 2014 и вторую 15 выходные шины, транзисторы первый выключения 16, первыйвключения 17, первый проходной 18,первый ключевой 19, первый адресный20 первый предзаряда 21, второй 25адресный 22, первый входной 23, второй выключения 24, второй включения25, второй проходной 26, второй ключевой 27, третий адресный 28, второйпредэаряда 29, четвертый адресный 30, 30второй входной 31, удержания 32, подготовки 33, бутстрепный 34, конденсаторы первый управляющий 35, второйуправляющий 36, выходной 37.Сток первого транзистора выключения 16 соединен с истоком первоготранзистора включения 17, первойвыходной шиной 14 и истоком первогопроходного транзистора 18, затвор которого подключен к истоку первогоключевого транзистора 19, стоку первого адресного транзистора 20, первому выводу первого управляющего конденсатора 35, затвор первого ключевого транзистора 19 соединен с истоком первого транзистора предзаряда21, стоком третьего адресного транзистора 22 и стоком первого входноготранзистора 23, сток второго транзистора выключения 24 соединен с исто 50ком второго транзистора включения 25,второй выходной шиной 15 и истокомвторого проходного транзистора 26,затвор которого подключен к истокувторого ключевого транзистора 27,стоку второго адресного транзистора22 и первому выводу второго управляющего конденсатора 36, затвор второгоключевого транзистора 27 соединен с 7 2истоком второго транзистора предзаряда 29, стоком четвертого адресного транзистора 30 и стоком второго входного транзистора 31, стоки первого проходного 18 и второго проходного 26 транзисторов подключены к истоку транзистора удержания 32 и первому выводу выходного конденсатора 37, второй вывод которого соединен со стоком транзистора подготовки 33 и истоком бутстрепного транзистора 34, затвор которого подключен ко вторым выводам первого управляющего 35 и второго управляющего 36 конденсаторов, стоки первого 17 и второго 25 транзисторов включения, первого 21 и второго 29 транзисторов предэаряда, транзистора удержания 32 и ,бутстрепного транзистора 34 соединены с шиной питания 1, истоки первого 16 и второго 24 транзисторов выключения, транзистора подготовки 33, первого 20, второго 22, третьего 28 и четвертого 30 адресных транзисторов соединены с общей шиной 2, затворы первого 16 и второго 24 транзисторов выключения образуют соответственно первый 3 и второй 4 входы выключения, затвора первого 17 и второго 25 транзисторов включения образуют соответственно инверсный 5 и прямой 6 входы включения, затворы первого 20 и третьего 28, второго 22 и четвертого 30 адресных транзисторов попарно объединены и образуют соответственно прямой 7 и инверсный 8 адресные входы, стоки первого 19 и второго 27 ключевых транзисторов объединены и образуют вход подброса 9, затворы первого 21 и второго 29 транзисторов предзаряда объединены и образуют вход предзаряда 10, затворы транзисторов удержания 32, бутсрепного 34 и подготовки 33 являются соответственно входами удержания 11, бутстрепным 12 и подготовки 13, истоки первого 23 и второго 31 входных транзисторов соединены с входом подготовки 13.Формирователь импульсов работает следующим образом.В исходном состоянии на входах первом 3 и втором 4 выключения, удержания 11, подготовки 13 и пред- заряда 10 установлен высокий уровень напряжения Е, равный напряжению на шине питания 1. При этом, первый 16 и второй 24 транзисторы выключенияоткрыты и первая 14 и вторая 15 выходные шины подключены к общей шине 2, на выходных шинах 14 и 15 установлены низкие уровни напряжения Транзистор подготовки 33 открыт и на втором выводе выходного конденсатора 37 установлен низкий уровень напряжения, а через открытый транзистор удержания 32 первый вывод выходного конденсатора 37 заряжен до высокого уровня напряжения.Первый 21 и второй 29 транзисторы предзаряда открыты и на затворах первого 19 и второго 27 ключевых транзисторов установлены высокие уровни напряжения. На входах включения прямом 6 и инверсном 5, адресных входах прямом 7 и инверсном 8, входах подброса 9 и бутстрепном 12 установлены низкие уровни напряжения. Формирователь приведен в исходное состояние.Поскольку сигналы на прямом 6 и инверсном 5 входах включения, а также на прямом 7 и инверсном 8 адресных входах являются взаимно дополняющими, т,е, при подаче высокого уровня напряжения на прямой вход включения 6 (прямой адерсный вход 7) инверсный вход включения 5 (инверсный адресный вход 8) остается в низком состоянии, рассмотрим работу формирователя в одном случае, когда сигналы высокого уровня подаются на прямой вход включения 6 и прямой адресный вход 7.В момент времени Т, (фиг. 2) на входах первом 3 и втором 4 выключения, удержания 11 и предзаряда 10 устанавливается низкий уровень напряжения и транзисторы первый 16 и второй 24 выключения, удержания 32, первый 21 и второй 29 предзаряда переходят в закрытое состояние.В момент времени 1 (фиг. 2) на прямом адресном входе 7 устанавливается высокий уровень напряжения, при этом первый 20 и третий 28 адресные транзисторы открываются и через третий 28 адресный транзистор низкий уровень передается на затвор первого 19 ключевого транзистора и он запирается.В момент времени(фиг. 2) на прямой вход включения 6 подается бутстрепный уровень напряжения И Е+И где И, - пороговое напряжение, а на вход подброса 9 - высокий уровень напряжения Е . При этом, второй транзистор включения 25 открывается ивторая выходная шина 15 заряжаетсядо высокого уровня напряжения Е,. Вто же время через открытый второйключевой транзистор 27 заряжаетсяпервый вывод второго управляющегоконденсатора 36 до уровня напряжения 10 Е . В то же время через открытыйвторой ключевой транзистор 27 заряжается первый вывод второго управляющего конденсатора 36 до уровня напряжения Е. Затвор и исток второго 26 15 проходного транзистора заряжаются одновременно до уровня Е поэтому онзакрыт и выходной конденсатор 37 изолирован от емкости нагрузки второйвыходной шины 15, что позволяет пол ностью сохранить заряд выходногоконденсатора 37.В момент времени с (фиг. 2) напрямой вход включения 6 и вход подготовки 13 подается низкий уровень 25 напряжения, второй транзистор включения 25 закрывается и вторая выходная шина 15 отключается от шины питания 1, транзистор подготовки 33закрывается, второй входной транзисЗд тор 31, на затворе которого установлен высокий уровень напряжения, открывается по цепи истока и на затворе второго ключевого транзистора 27устанавливается низкое напряжение,он закрывается. В этот же момент времени на бутстрепный вход 12 подаетсяуровень напряжения П , который передается через второй управляющий конденсатор 36 на затвор второго проход ного транзистора 26 и повышает егонапряжение до уровня Е+20, а такжеоткрывает бутстрепный транзистор 34,и уровень напряжения на втором выводе выходного конденсатора 37 стано 4 б вится равным Е, Уровень напряженияна первом выводе выходного конденсатора 37 повышается до величины У ичерез открытый второй проходной транзистор 26, на затворе которого установлено напряжение ИЕ,+2 Иг, передается на вторую выходную шину 15. Нагрузка, подключенная к второй выходной шине 15, заряжается до напряженияЗатвор первого проходного транзистора 18 соединен с общей шиной 2через открытый первый адресный транзистор 20, поэтому первый проходнойтранзистор 18 все это время закрыт.В момент времени(фиг. л) набутстрепном входе 12, прямом адресном входе 7 и входе подброса 9 устанавливается низкий уровень напряжения, транзисторы бутстрепный 34, первый 20, и третий 28 адресные, второй входной 31 и второй проходной 26закрываются, В момент времени т 5(фиг. 2) на входы предзаряда 10, подготовки 13, удержания 11, первый 3и второй 4 выключения подаются высокие уровни напряжения. Через открытый второй транзистор выключения 24вторая выходная шина 15 разряжается.На первом выводе выходного конденсатора 37 через открытый транзисторудержания 32 устанавливается высокийуровень напряжения, на второй еговыводе через открытый транзистор подготовки 33 - низкий, на затворахключевых транзисторов 19 и 27 черезоткрытые транзисторы предзаряда 21и 29 - высокий уровень напряжения,а на затворах проходных транзисторов,2518 и 26 через открытые ключевыетранзисторы 19 и 27 - низкий уровеньнапряжения, Формирователь вернулсяв исходное состояние и готов к новому циклу работы. 30Для получения выходного сигналапервой выходной шине 14 необходимоподать сигналы на инверсный входвключения 5 и инверсный адресныйвход 8, при этом на прямой входвключения 6 и на прямой адресный35вход 7 должны быть поданы низкиеуровни напряжения.Для упрощения схем управления итопологии формирователя импульсоввозможно объединение вхоцов первого3 и второго 4 выключения, предзаряда 10 и удержания 11, поскольку сигналы, подаваемые на эти входы совпадают (фиг. 2), при этом транзисторыудержания 32, первый 21 и второй 29предзаряда могут быть со встроеннымиканалами.Расширение области применения достигается введением второй выходной50шины, что позволяет использовать формирователь без дополнительного блокаселекции сигнала в случае необходимости получения сигнала по двум выходным шинам,Данный формирователь импульсовпредпочтительнее использовать в качестве формирователя сигнала выборкистроки и/или столбца, поскольку первая и вторая выходные шины полностьюнезависимы по управлению,При формировании сигнала выборкистроки и/или столбца емкость нагрузки разделяется поровну на две группы,которые подключаются к первой и второй выходным шинам, поэтому емкостьнагрузки на каждой выходной шинеменьше, чем емкость на выходе известного устройства, что повышает быстродействие предложенного формирователяимпульсов. Формула и з о б р е т е н и яФормирователь импульсов, содержащий первый транзистор выключения, блок которого соединен с первой выходной шиной, с истоками первого транзистора включения и первого проходного транзистора, сток которого подключен к истоку транзистора удержания и первому выводу выходного конденсатора, затвор первого проходного транзистора соединен с первым выводом первого управляющего конденсатора и истоком первого ключевого транзистора, транзистор подготовки, сток которого соединен с истоком бутстрепного транзистора, стоки первого транзистора включения, транзистора удержания и бутстрепного транзистора подключены к шине питания, истоки первого транзистора выключения и транзистора подготовки подключен к общей шине, затворы первого транзистора включения, первого транзистора выключения, транзистора подготовки образуют соответственно входы инверсный включения, первый выключения и подготовки, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия и области применения, в него введены вторая выходная шина, второй транзистор включения, второй транзистор выключения, второй проходной транзистор, второй ключевой транзистор, первый и второй транзисторы предзаряда, с первого по четвертый адресные транзисторы, первый и второй входные транзисторы и второй. управляющий конденсатор, причем сток второго транзистора выключения соединен с второй выходной шиной, с истоками второго транзистора включения и второго проходного транзистора, сток которого подключен к первому выводу выходного конденсатора, сток которого подключен к первому выводуюг выходного конденсатора, затвор второго проходного транзистора соединенс первым выводом второго управляющего конденсатора и истоком второгоключевого транзистора, стоки первогои второго адресных транзисторов соединены соответственно с истоками первого и второго ключевого транзистора,истоки первого и второго транзисторов предзаряда соединены с затворамипервого и второго ключевых транзисторов, стоками третьего и четвертого адресных транзисторов и стокамипервого и второго входных транзисторов соответственно, стоки первого ивторого ключевых транзисторов объединены и образуют вход подброса, затворы первого и второго транзисторовпредзаряда объединены и образуют щвход предзаряда, вторые выводы первого и второго управляющих конденсаторов соединены с затвором бутстрепного транзистора и образуют бутстрепный вход, исток бутстрепного транзистора соединен с вторым выводом выходного конденсатора, затворы первогои третьего адресных транзисторов изатвор второго входного транзистораобъединены и образуют прямой адрес"ный вход, затворы второго и четвертого адресных транзисторов и первоговходного транзистора объединены иобразуют инверсный адресный вход,затворы транзисторов удержания, второго транзистора включения и второготранзистора выключения являются соответсЪенно входом удержания, прямьщвключения и вторым выключения, истоки первого и второго входных транзисторов соединены с входом подготовки, стоки транзисторов второго включения, первого и второго предзарядасоединены с шиной питания, а стокивторого транзистора выключения и че"тырех адресных транзисторов подключены к общей шине.

СмотретьЗаявка

3851366, 31.01.1985

ПРЕДПРИЯТИЕ ПЯ Р-6429

БЕСПАЛОВ ВЛАДИМИР ПЕТРОВИЧ, МАКАРОВ АЛЕКСАНДР ИВАНОВИЧ, МЕЩАНОВ ВЛАДИМИР ДМИТРИЕВИЧ, ТЕЛИЦЫН НИКОЛАЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H03K 5/13

Метки: импульсов, формирователь

Опубликовано: 15.02.1988

Код ссылки

<a href="https://patents.su/5-1374417-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Формирователь импульсов

Следующий патент: Устройство для задержки импульсов

Случайный патент: Упругий соединитель труб